# A Simplified PWM Technique for Reduced Switch Count Multilevel Inverter

A. Ramesh<sup>1</sup>, O. Chandra Sekhar<sup>2</sup>, M. Siva Kumar<sup>3</sup>

<sup>1,2</sup>K. L. University, Guntur, India <sup>3</sup>Gudlavalleru Engineering College, Gudlavalleru, India

#### **Article Info**

#### Article history:

Received Sep 19, 2017 Revised Dec 30, 2017 Accepted Jan 17, 2018

#### Keywords:

Multilevel Inverter Pulse Width Modulation Renewable Energy Sources Total Harmonic Distortion

#### ABSTRACT

Penetration of multilevel inverters (MLI) in to high power and medium voltage application has been increasing because of its advantages. A conventional two level inverter has high harmonic distortion which gives poor power quality. Lot of topologies has been developed to overcome the drawbacks of two level inverter. These topologies include more number of switching devices which increases the design complexity and cost. The optimum design of inverter requires less number of switches with better quality in waveform. In this paper, a symmetrical five level and seven level inverter configuration with simplified pulse width modulation technique is proposed. This proposed inverter requires less switches, less protection circuits along with low cost and size. The analysis of the inverter circuits is done by using Matlab/Simulink software. The synthesized staircase wave form is shown and total harmonic distortion (THD) is also measured.

Copyright © 2018 Institute of Advanced Engineering and Science.

All rights reserved.

711

# Corresponding Author:

A. Ramesh,

K. L. University, Guntur, India.

Email: rameshadireddy007@gmail.com

# 1. INTRODUCTION

In recent years, the industries have started to operate at higher power rating machines. And for some medium voltage drives and applications, they need medium voltage and high power level. For this purpose, multilevel inverter [1]-[3] concept has been developed for high power and medium voltage applications. These inverters are not only used for high power applications, but also used for interfacing the renewable energy sources (RES) [4]-[6] to the utility grid. The renewable energy sources like solar, wind and fuel cell could be easily connected to the grid using multilevel inverters. The multilevel inverter concept has been introduced since 1975. It has started with a three level inverter and consequently lot of inverter topologies has been introduced

However, the major objective of the multilevel inverter is to get high power using power semiconductor switches with number of low voltage dc sources. The characteristics of less total harmonic distortion (THD) [7-8], reduced dv/dt and low common mode voltage are the reasons for getting popularity for the multi-level inverters in medium voltage and high power applications. The advantages of multilevel inverter are given below.

- a. Reduces the electromagnetic compatibility problems because of low dv/dt stress and less harmonic distortion.

- b. The common mode voltage of a multilevel inverter is small. Therefore, if a multilevel inverter is connected to drive the stresson the bearing will be reduced.

- c. The current drawn by the multilevel inverter has low distortion.

- d. Multilevel inverters can able to operate at fundamental as well as high switching frequency.

However, more number of switching devices in the inverter causes to decrease the efficiency and reliability of the drive [9]-[10]. Therefore, it is necessary to improve the reliability and efficiency by reducing

712 ISSN: 2502-4752

the number of switches. In this paper, a reduced switch count multilevel inverter for five and seven level is proposed. A simplified pulse width modulation technique is implemented for control strategy [11]. A five level inverter is proposed with five switches and a 7 level inverter is proposed with six switches. These circuits are implemented using Matlab/Simulink software. The total harmonic distortion for voltage wave form is measured by fast Fourier transform analysis.

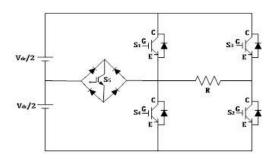

#### FIVE SWITCH FIVE LEVEL INVERTER

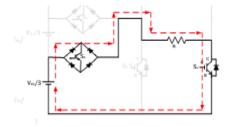

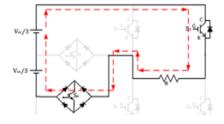

The proposed 5 switch five level multilevel inverter is shown in figure 1. This topology consists of four switches of IGBT and one ideal switch. The source voltage is divided in to two equal parts as V<sub>dc</sub>/2each. The configuration of the circuit with R load is shown.

The required five level output voltage levels 0,  $V_{dc}/2$ ,  $V_{dc}$ ,  $-V_{dc/2}$  and  $-V_{dc}$  are obtained by operating these five switches in proportional manner. The diagrams for each level are illustrated in following figures.

Figure 1. Proposed five level inverter

Figure 2. Operational diagram for 0 voltage level

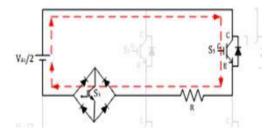

Figure 3. Operational diagram for  $V_{dc}/2$  voltage level

Figure 4. Operational diagram for  $V_{\text{dc}}$  voltage level

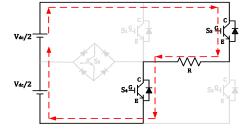

Figure 5. Operational diagram for -V<sub>dc/2</sub> voltage level Figure 6. Operational diagram for -Vdc voltage level

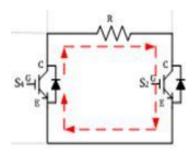

# Level - 0

To get zero voltage level, the switches S2 and S4 should be turned on. The load becomes short circuit and the voltage across it is zero. The operational diagram is shown in Figure 2.

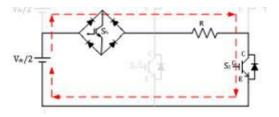

The voltage level of Vdc/2 is produced by switching ON the switches S2 and S5.In this case only bottom source is connected to the load and the voltage  $V_{\text{dc/2}}$  appears across the load. The operational diagram is shown in figure 3.

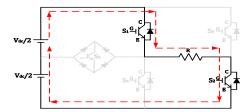

# $Level-V_{dc} \\$

By switching ON switches S1 and S2 we can get the voltage level of  $V_{dc}$ . In this case both the voltage sources appear across the load. The operational diagram is shown in Figure 4.

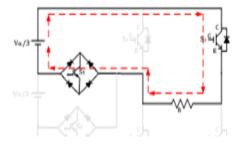

#### Level - $-V_{dc/2}$

The  $-V_{dc/2}$  voltage level is obtained by closing the switches S3 and S5. In this case the upper voltage source is connected to the load. The operational diagram is shown in Figure 5.

#### $Level - -V_{dc}$

The voltage level  $-V_{dc}$  could be obtained by operating the switches S3 and s4. Both the voltage sources are connected to load with negative polarity. The operational diagram is shown in Figure 6.

Table 1. Switching Sequence for Five Level Five Switch Multilevel Inverter

| Voltage              | Switching Sequence |       |       |       |       |

|----------------------|--------------------|-------|-------|-------|-------|

| levels               | $S_1$              | $S_2$ | $S_3$ | $S_4$ | $S_5$ |

| 0                    | OFF                | ON    | OFF   | ON    | OFF   |

| $V_{dc/2}$           | OFF                | ON    | OFF   | OFF   | ON    |

| $V_{dc}$             | ON                 | ON    | OFF   | OFF   | OFF   |

| $-V_{\mathrm{dc/2}}$ | OFF                | OFF   | ON    | OFF   | ON    |

| $-V_{ m dc}$         | OFF                | OFF   | ON    | ON    | OFF   |

The Table 1 shows the switching pattern for five switch five level inverter.

# 3. SIX SWITCH SEVEN LEVEL INVERTER

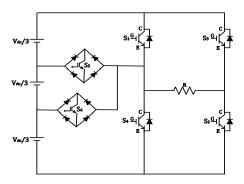

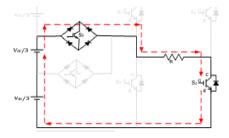

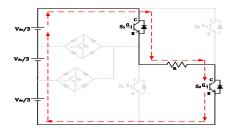

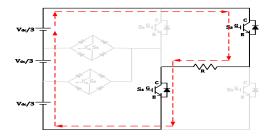

The proposed 6 switch seven level multilevel inverter is shown in Figure 7. This topology consists of four switches of IGBT and two ideal switches. The source voltage is divided in to three equal parts as Vdc/3each. The configuration of the circuit with R load is shown.

Figure 7. Proposed seven level inverter

The required seven level output voltage levels 0,  $V_{dc/3}$ ,  $2V_{dc/3}$ ,  $V_{dc}$ ,  $-V_{dc/3}$ ,  $-2V_{dc/3}$  and  $-V_{dc}$  are obtained by operating these six switches in proportional manner. The diagrams for each level are illustrated in following figures.

Figure 8. Operational diagram for level zero

Figure 9. Operational diagram for level  $V_{\text{dc/3}}$

714 🗖 ISSN: 2502-4752

Figure 10. Operational diagram for level 2V<sub>dc/3</sub>

Figure 11 Operational diagram for level V<sub>dc</sub>

Figure 12 Operational diagram for level -V<sub>dc/3</sub>

Figure 13 Operational diagram for level -2V<sub>dc/3</sub>

Figure 14. Operational diagram for level -V<sub>dc</sub>

#### Level - 0

To get zero voltage level, the switches S2 and S4 should be turned on. The load becomes short circuit and the voltage across it is zero. The operational diagram is shown in Figure 8.

# Level - $V_{dc/3}$

The voltage level of Vdc/3 is produced by switching ON the switches S2 and S6.In this case only bottom source is connected to the load and the voltage  $V_{\text{dc/3}}$  appears across the load. The operational diagram is shown in Figure 9.

# Level - $2V_{dc/3}$

The voltage level of 2Vdc/3 is produced by switching ON the switches S2 and S5.In this case bottom two sources are connected to the load and the voltage  $2V_{dc/3}$  appears across the load. The operational diagram is shown in Figure 10.

# $Level-V_{dc}$

By switching ON switches S1 and S2 we can get the voltage level of  $V_{dc}$ . In this case all the voltage sources appear across the load. The operational diagram is shown in Figure 11.

# Level - - V<sub>dc/3</sub>

The voltage level of  $-V_{dc/3}$  is produced by switching ON the switches S3 and S5.In this case only upper source is connected to the load and the voltage  $-V_{dc/3}$  appears across the load. The operational diagram is shown in Figure 12.

# Level - $-2V_{dc/3}$

The voltage level of  $2V_{dc/3}$  is produced by switching ON the switches S3 and S6.In this case top two sources are connected to the load and the voltage  $-2V_{dc/3}$  appears across the load. The operational diagram is shown in Figure 13.

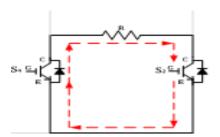

#### Level – -V<sub>d</sub>

By switching ON switches S3 and S4 we can get the voltage level of  $-V_{dc}$ . In this case all the voltage sources appear across the load. The operational diagram is shown in Figure 14.

# 4. SIMPLIFIED PWM TECHNIQUE

#### 4.1. For Five Switch Five Level

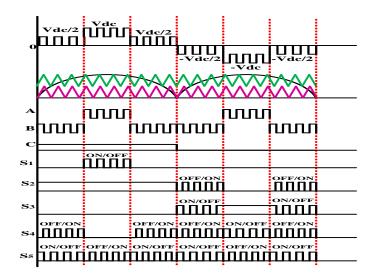

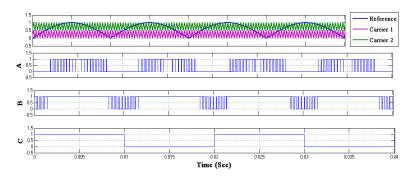

In multilevel inverters the output voltage is controlled by using different modulation strategies. In PWM control, there are three techniques like fundamental switching frequency PWM, PWM technique based on carrier and space vector PWM technique. Among these, the carrier based PWM technique is frequently used because; it has less complexity even when output voltage levels are more. In this paper, a multi-carrier based SPWM (sinusoidal pulse width modulation) technique has been implemented. It contains a reference signal which is compared with the two high frequency carrier signals to generate switching states A, B and C (Figure 15). The two carriers have a small difference in its magnitude which are disposed vertically. By combining these switching states, the gating pulses are generated for the switches using following logical notation.

$$\begin{split} S_1 &= A \cdot C \\ S_2 &= C + \bar{B}\bar{C} \\ S_3 &= B \cdot \bar{C} \\ S_4 &= \bar{B}C + \bar{B}\bar{C} + A\bar{C} \\ S_5 &= B\bar{C} \end{split}$$

Figure 15. PWM technique for five level

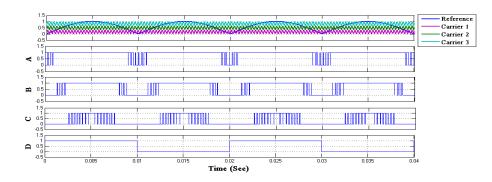

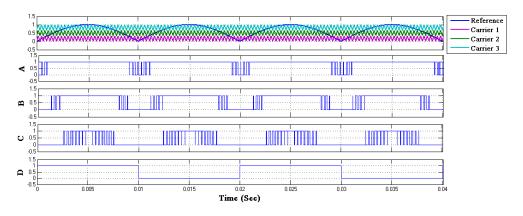

#### 4.2. For Six Switch Seven Level

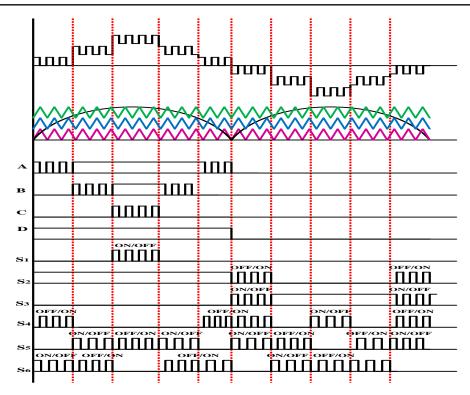

In this control three carrier waveforms are used to generate the four switching states. The logical combination of four switching states A, B, C and D gives us the pulses for switches S1 through S6. The PWM technique and switching logic is given.

By combining these switching states, the gating pulses are generated for the switches using following logical notation.

$$\begin{split} S_1 &= C \cdot D \\ S_2 &= D + \bar{A} \overline{D} \\ S_3 &= A \cdot \overline{D} \\ S_4 &= \bar{A} D + \bar{A} \overline{D} + C \overline{D} \\ S_5 &= B \overline{C} D + A \overline{B} \overline{D} \\ S_6 &= A \overline{B} D + B \overline{C} \overline{D} \end{split}$$

Figure 16. PWM technique for seven level

# 5. SIMULATION RESULTS

# 5.1. Five switch Five level inverter

# Case 1: R-load

Figure 17. Shows the output voltage of the five switch five level inverter.

Figure 17. Output voltage

The output current wave form is shown in Figure 18

Figure 18. Output current

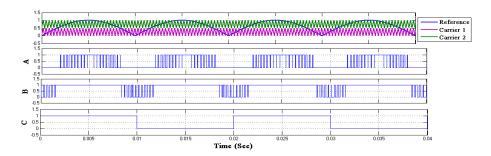

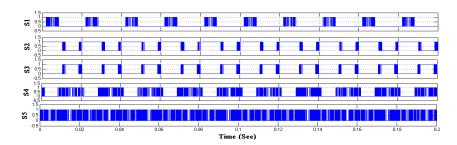

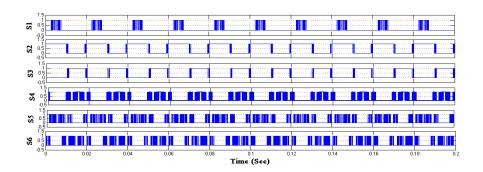

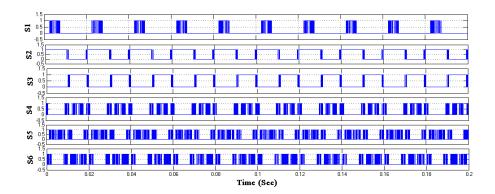

The PWM waveforms and switching pulses are shown in Figure 19 and 20 respectively.

Figure 19. PWM wave forms

Figure 20. Switching pulses

# Case 2: RL-Load

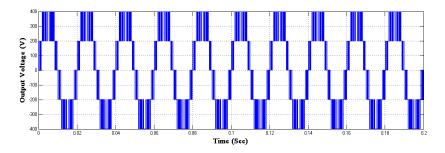

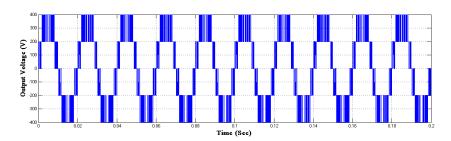

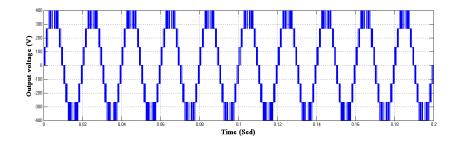

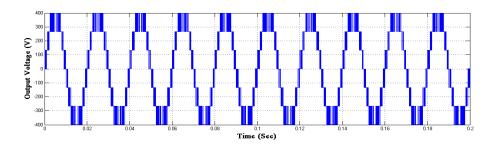

The output voltage waveform is shown in Figure 21.

Figure 21. Output voltage

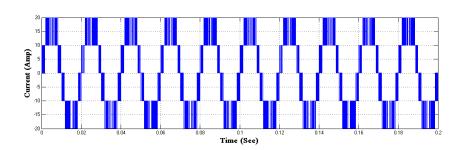

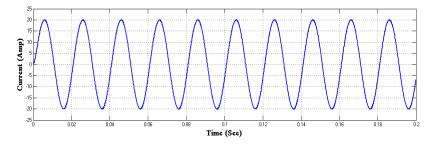

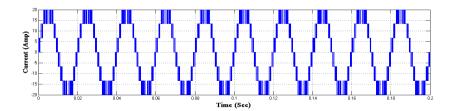

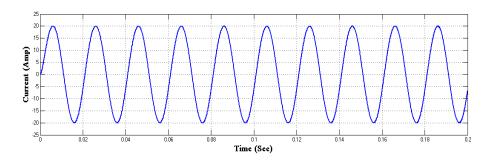

Figure 22 shows the output current wave form.

Figure 22. Output current

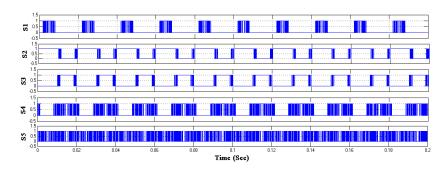

PWM wave forms and switching pulses are shown in Figure 23 and 24 respectively.

Figure 23. PWM wave forms

Figure 24. switching pulses

The total harmonic distortion for voltage wave form is given in figure 25 and the THD measured is 26.87%.

Figure 25. THD Graph

# 5.2. Six Switch Seven Level Inverter

# Case 1: R-load

The output voltage of six switch seven level is shown in Figure 26.

ISSN: 2502-4752

Figure 26. Output voltage

Figure 27 shows the output current.

Figure 27. Output current

The PWM waveforms and switching pulses are shown in Figure 28 and 29 respectively.

Figure 28 PWM waveform

Figure 29. Switching pulses

# Case 2: RL-load

Figure 30 shows the output voltage wave form.

720 ISSN: 2502-4752

Figure 30. Output voltage Output current waveform is shown in Figure 31.

Figure 31. Output current

Figure 32 and 33 shows the PWM waveform and switching pulses respectively.

Figure 32. PWM wave form

Figure 33. Switching pulses

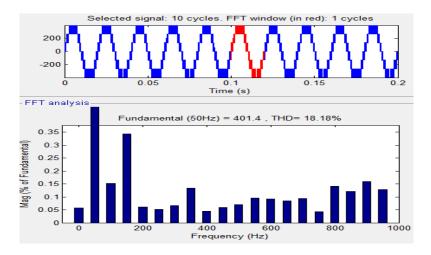

The total harmonic distortion is shown in Figure 34 and measured 18.18%.

ISSN: 2502-4752

Figure 34. THD

#### 6. CONCLUSION

In this paper, the five switch five level and a six switch seven level multilevel inverter is proposed. A simplified pulse width modulation technique also has been implemented for proposed inverters. Based on the PWM wave forms a digital switching logic has been developed and implemented to the control logic. The five level and seven level inverters are analyzed with R and RL load and the results are presented. The total harmonic distortion is also measure for both the levels. The THD for five level is 26.87% and for seven level is 18.18%.

#### REFERENCES

- [1] S. Sridhar, P. Satish Kumar, M. Susham "A Novel Generalized Topology for Multi-level Inverter with Switched Series-Parallel DC Sources" Indonesian Journal of Electrical Engineering and Computer Science (IJEECS) Vol 4, Nov 2016. pp41-51

- [2] C.R. Balamurugan, S.P. Natarajan, R. Bensraj "Analysis of a New Reduced Switch Nine Level Inverter" Indonesian Journal of Electrical Engineering and Computer Science (IJEECS) Vol 1, No 3: March 2016 .pp490-501

- Mohammed Rasheed, Rosli Omar, Marizan Sulaiman "Harmonic Reduction in Multilevel Inverter Based on Super Capacitor as Storage" Indonesian Journal of Electrical Engineering and Computer Science (IJEECS) Vol 16, No 3 December 2015 pp520-530

- [4] H. Manafi H. Ebrahimian M. Salimi "7-level cascade multilevel inverter using a single DC source and minimum THD of Output Voltage" <em>Int. Symp. Smart Electr. Distrib. Syst. Technol. EDST 2015</em> pp. 390-393 2015

- [5] N. Farokhnia H. Vadizadeh S. H. Fathi F. Anvariasl "Calculating the formula of line-voltage THD in multilevel inverter with unequal DC sources" <em>IEEE Trans. Ind. Electron</em> vol. 58 no. 8 pp. 3359-3372 2011.

- [6] Baby T. Charles YS. Sabah Krishna Prabhakar. Lall "Multilevel Inverter fed Induction motor Drivefor Pumping Application" <em>IEEE International Conference on Technological Advancements in Power & Energy</em> 2015.

- [7] M. Beye, M. Elsied, A. M. Mabwe and C. Onambele, "Grid interconnection of renewable energy sources based on advanced multi-level inverter," 2017 IEEE International Conference on Environment and Electrical Engineering and 2017 IEEE Industrial and Commercial Power Systems Europe (EEEIC / I&CPS Europe), Milan, 2017, pp. 1-6

- [8] G. R. Dhikale and G. N. Jadhav, "Design and analysis of TZ-source inverter for integration of renewable energy," 2016 IEEE 7th Power India International Conference (PIICON), Bikaner, Rajasthan, India, 2016, pp. 1-6.

- S. Gupta, S. Singh, G. Bhuvaneswari, B. Singh and N. Mohan, "A thyristorised phase-controlled cycloconverter based power electronic transformer for grid integration of renewable energy sources," 2016 IEEE 7th Power India International Conference (PIICON), Bikaner, Rajasthan, India, 2016, pp. 1-6.

- [10] A. Zhetessov and A. Ruderman, "Simultaneous Selective Harmonic Elimination and Total Harmonic Distortion minimization for a single-phase multilevel inverter with staircase modulation," 2017 International Conference on Optimization of Electrical and Electronic Equipment (OPTIM) & 2017 Intl Aegean Conference on Electrical Machines and Power Electronics (ACEMP), Brasov, 2017, pp. 729-734.

- [11] A. S. Al-Ogaili, I. Aris, M. L. Othman, N. B. Azis, D. Isa and Y. Hoon, "New technique for decreasing of total harmonic distortion of three-phases bridge rectifier by using the method of harmonic injection," 2016 IEEE Conference on Systems, Process and Control (ICSPC), Bandar Hilir, 2016, pp. 248-253.

- [12] Y. Yu, X. Chen and Z. Dong, "Current sensorless direct predictive control for induction motor drives," 2017 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Harbin, China, 2017, pp. 1-6.