# New Technique Based Peasant Multiplication for Effcient Signal Processing Applications

## Mahendra Sharma\*, Dr Santhosh Kumar Singh

Department of Information Technology, AMET University, Chennai

#### Abstract

The Direct Form FIR channel is utilized for DSP application where the channel request is settled. For the most part this channel devours more range and power. To defeat this issue Multiplier Control Signal Decision window (MCSD) plans is joined into Direct Form FIR channel to powerfully change the channel arrange. MCSD structures comprise of Control flag Generator (CG) and Amplitude Detection (AD) rationale circuits. Advertisement rationale is utilized to disavow the correct duplication process and screen the amplitudes of information tests. CG is utilized to control the channel operation through inside counter. Traditional reconfigurable FIR channel is planned utilizing Vedic Multiplier that devours more territory and deferral. In this paper, changed reconfigurable FIR filer is intended to additionally decrease the APT (Area, Power and Timing) item. The proposed Reconfigurable FIR filer, Vedic Multiplier is supplanted by Russian Peasant Multiplication procedure. Subsequently adjusted Reconfigurable FIR channel with Russian Peasant Multiplier expends less region, postponement and power than all analyzed techniques.

**Keywords**: Finite Impulse Response (FIR), Digital signal processing (DSP), Multiplier Control Signal Decision Window (MCSD), Control signal generator (CG), Amplitude detection (AD), Russian Peasant Multiplication (RPM)

#### Copyright © 2017 Institute of Advanced Engineering and Science. All rights reserved.

#### 1. Introduction

The flimsy development in convenient sight and sound and versatile registering applications has extended the interest for low power Digital signal processing (DSP) frameworks and Wireless Communication. A standout amongst the most widely utilized capacities executed in DSP is Finite Impulse Response (FIR) separating. In a few applications, keeping in mind the end goal to achieve high phantom concealment and commotion decrease, FIR channels with respectably enormous number of taps are basic. A great deal of earlier endeavours for diminishing force utilization of FIR channel typically concentrate on the scaling down of the channel coefficients while keeping up a settled channel arrange. FIR channel structures are improved to limiting the quantity of options/subtractions and include and move operations. However, one of the issues experienced is that one time the channel engineering is resolved, the coefficients can't be changed; thusly, those are not fitting to FIR channel with programmable coefficients. Genuinely precise flag preparing frameworks are additionally utilized for the outline of low power advanced channels. An efficient approach for the removal of bipolar impulse noise using median filter is described in [6]. Synthesis, surface morphological and electrical properties as well as structural features of Pr6O11–MgO nano-composite is studied briefly in [7].

## 2. Finite Impulse Response Filter

An FIR filter is also called as Recursive filter. The word recursive literally means "running back", and refers to the fact that previously-calculated output values go back into the calculation of the latest output. The FIR filter uses, previous output values with input values in every stage, hence it is called as the recursive filter. These, like previous input values are stored in the processor's memory.

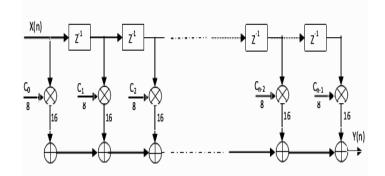

Figure 1. Direct form FIR Filter structure

# 3. Proposed Russian Peasant Multiplication

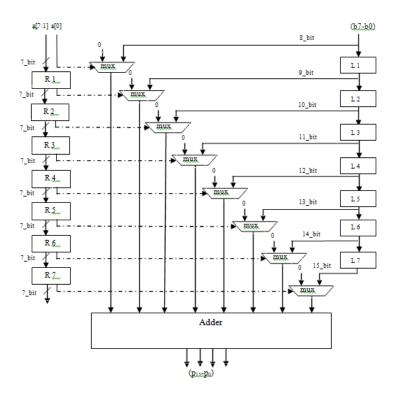

The architecture for Russian Peasant Multiplier consists of Shifters, 2:1 Multiplexers and adder units to perform multiplication. This architecture is quite simple and easy to design.

Figure 2. Architecture of Russian Peasant Multiplier

The Figure 2 shows the 8 bit Russian Peasant Multiplier architecture. Similarly, 16-bit Russian Peasant Multiplier can be extended from figure 4.1. Here, two shifters namely, Right shifters and Left shifters are used to shift the Multiplicand and Multiplier values respectively in each stage. In each stage, Least Significant Bit (LSB) value of Right shifter generates the control signal for 2:1 Multiplexers. The effective Carry Save Adder (CSA) is used to addition part of Russian Peasant Multiplier. The proposed multiplier is performed efficiently compare than the booth multiplier.

## 4. Simulation Results

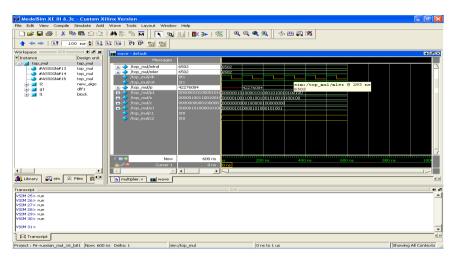

The proposed Russian peasant multiplication technique is implemented by using Verilog HDL language. The proposed multiplication technique is mainly proposed for the efficient Multiplication and accumulation (MAC) unit in the filters applications. The proposed multiplier is perform efficiently compare than the conventional booth multiplier unit. Proposed MAC unit is implemented in terms of the VLSI design environment. The simulation result of the proposed multiplier as illustrated in Figure 3.

Figure 3. Simulation output of the proposed multiplier unit

# 5. Synthesis Results

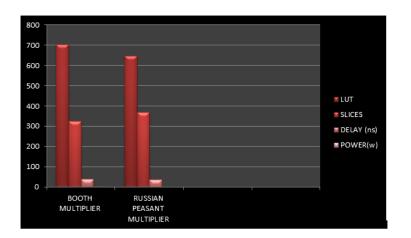

The proposed multiplier is performed efficiently in terms of the area, delay and power. These synthesis results are evaluated by using Xilinx ISE as tabulated as Table 1. And graphically represented in Figure 4.

| Table 1. Synthesis results of the conventional and p | proposed multiplier |

|------------------------------------------------------|---------------------|

|------------------------------------------------------|---------------------|

| DESCRIPTION           | A<br>LUT | REA<br>SLICES | DELAY      | POWER   |

|-----------------------|----------|---------------|------------|---------|

| BOOTH                 | 704      | 325           | 38.984 ns  | 0.392 W |

| MULTIPLIER<br>RUSSIAN | 648      | 368           | 36.768 ns  | 0.305 W |

| PEASANT               | 040      | 300           | 30.700 115 | 0.305 W |

| MULTIPLIER            |          |               |            |         |

## 6. Conclusion

In this work, the ADP (Area, Delay and Power) efficient Russian peasant multiplication is implemented by using Verilog HDL. The proposed multiplier consumes 56 Look-up-tables compared than the booth multiplier. The computation time of the proposed multiplier is 2.216 ns low compare than the existing method and also the power utilization is efficient so the proposed multiplier is applicable for the low power applications. In future, the proposed Russian peasant technique is applied in FIR filters and also in image processing application for sampling process.

# References

- [1] Akhilesh Tyagi. A Reduced Area Scheme for Carry- Select Adders. *IEEE transaction on computer*. 1993; 42: 1163 1170.

- [2] Bedrij OJ. Carry Select Adder. IRE Transaction Electronics Computer. 1962; 11: 340- 344.

- [3] Chang TY and Hsiao MJ. Carry Select Adder using Single Ripple Carry Adder. *Electronics Letters*. 1998; 34: 2101 2103.

- [4] Chyn Wey I, Cheng Chen, Yi Sheng Lin and Chin Chang pengl. An Area- Efficient CSLA Design by Sharing the Common Boolean Logic Term. International Multi conference of Engineers and Computer Scientists. 2012; 2: 14 -16.

- [5] He Y, Chang CH and Gu J. An Area Efficient 64-bit Square Root Carry Select Adder for Low power Application. IEEE International Symposium Circuits Systems. 2005; 4: 4082 – 4085.

- [6] Kadali KS and Rajaji L. An efficient approach for the removal of bipolar impulse noise using median filter. *Indian Journal of Science and Technology*. 2015; 8(13).

- [7] Selvi KT, Alamelumangai K, Priya M, Rathnakumari M, Kumar PS and Sagadevan S. Studies on synthesis, structural, surface morphological and electrical properties of Pr6O11–MgO nanocomposite. *Journal of Materials Science: Materials in Electronics*. 2016; 27(6): 6457-6463.