DOI: 10.11591/ijeecs.v7.i3.pp676-686

# Performance Evaluation of Multicarrier Based Techniques for Single Phase Hybrid Multilevel Inverter using Reduced Switches

**676**

### Nunsavath Susheela\*, P. Satish Kumar

Department of Electrical Engineering, University College of Engineering, Osmania University, Hyderabad, Telangana, India

\*Corresponding author, e-mail: nsusheela2007@yahoo.com

#### Abstract

The multilevel inverters are very popular in high power high voltage applications. However the multilevel inverters has some demerits such as requiring higher number of components, PWM control method is complex and capacitor voltage balancing problem. The hybrid multilevel inverter presented in this paper has superior characteristics over conventional multilevel inverters. The hybrid multilevel inverter employs fewer components and less carrier signals when compared to conventional multilevel inverters. It consists of level generation and polarity generation stages which involves high frequency and low frequency switches. The complexity and overall cost for higher output voltage levels are greatly reduced. Implementation of single phase 7-level, 9-level and 11-level hybrid multilevel inverter has been performed using sinusoidal pulse width modulation (SPWM) strategies i.e., phase disposition (PD), alternate phase opposition disposition (APOD) and carrier overlapping (CO). Also the three techniques are compared in terms of total harmonic distortion (THD) for various modulation indices and observed to be greatly improved when compared to conventional topologies. The performance of single phase eleven level hybrid inverter is analyzed for different loads. Simulation is performed using MATLAB/ Simulink.

**Keywords**: sinusoidal pulse width modulation, phase disposition, multilevel inverter, carrier overlapping, total harmonic distortion

Copyright © 2017 Institute of Advanced Engineering and Science. All rights reserved.

#### 1. Introduction

Renewable energy sources such as photovoltaic, wind, and fuel cells can be easily interfaced to a multilevel converter system for a high-power application. Contemporary research has engaged novel converter topologies and unique modulation schemes. Moreover, three different major multilevel converter structures have been reported in the literature cascaded Hbridges converter with separate dc sources, diode clamped (neutral clamped), and flying capacitors (capacitor clamped). Moreover, abundant modulation techniques and control paradigms have been developed for multilevel converters. Latest trend of multilevel inverters (MLI) is to use medium voltages in industrial drives to meet the power requirements going up to several megawatts. MLI technologies are receiving increased attention for high power applications in power industry. This is due to the improvement in output waveforms compared to two level inverter [1-5]. The bipolar junction transistor (BJT), insulated gate bipolar transistor (IGBT), metal oxide semiconductor field effect transistor (MOSFET) switches of the inverter are turned on and off as per the sequence specified by a pulse width modulation (PWM) method to produce ac output waveforms. The concept of power conversion in multilevel inverters(MLI) is to synthesize a staircase voltage waveform from several lower voltage DC sources which approaches the sinusoidal wave with reduced harmonic distortion has got several advantages and have drawn tremendous interest in high power high voltage applications. In case of multilevel inverters the semiconductors are wired to form series type connection so that the operation at higher voltages is possible.

The switching losses and the switching frequency can be reduced by staggering the switching because the switches are not truly series connected. Conventional multilevel inverters include neutral point clamped (diode-clamped) inverter, flying capacitor (capacitor clamped) inverter and cascaded H-bridge inverter. The major drawback of multilevel inverters is the higher number of power semiconductor switches needed that complicates the overall

system [6-8]. Using lower rated switches in the multilevel inverter can reduce the cost of active semiconductors compared to two level inverters. Associated gate drive circuits are required for each active semiconductor which increases the complexity. A reversing voltage topology for multilevel inverters is discussed in recent research [9]. This multilevel inverter topology requires less number of components when compared to conventional multilevel inverters. A multilevel inverter with reversing voltage component has many advantages as the levels increase when compared to conventional multilevel inverters. The hybrid topology eliminates the diodes and capacitors that are used in diode clamped inverters, capacitors used in flying capacitor inverters and also reduces the switches and carrier signals required than in cascaded inverters, diode clamped, and flying capacitors inverters. An approach of utilizing high-power devices with lowswitching-frequency reduces voltage distortion of output but has got current harmonics which is a major drawback [10-13]. There are asymmetrical methods of using different values of voltage source which requires more number of power switches and diodes with different rating. Some topologies suffer from the capacitor balancing problems. Whereas in case of hybrid multilevel inverter, the voltage sources used have equal values and has many advantages compared with the methods discussed above. It uses less number of switches and carrier waves and also operates the switching devices at line frequency which results in more efficiency.

Various carrier-based PWM techniques are reported to minimize total harmonic distortion (THD). Advanced multilevel inverter topologies have been proposed recently such as hybrid multilevel inverter, soft switching inverter and generalized multilevel inverter. The multilevel inverters have been extensively used in applications like FACTS, tractions and industrial drives [14-19]. In this paper, phase disposition (PD), alternate phase opposition disposition (APOD) and carrier overlapping (CO) sinusoidal pulse width modulation(SPWM) techniques are utilized to drive the inverter.

#### 2. Hybrid Multilevel Inverter

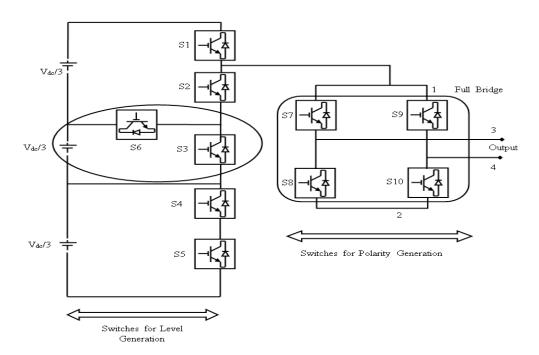

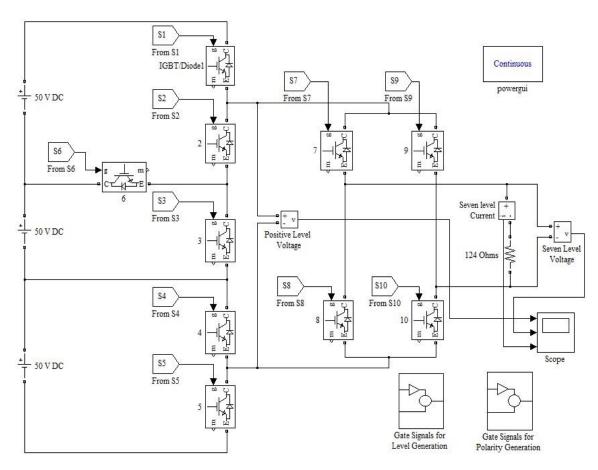

The hybrid MLI topology is a combination of level generation as well as polarity generation parts which is responsible for multilevel output voltage generation. Here, the level generation part that consists of high-frequency switches produce the positive levels. And the polarity generation part with low frequency switches is responsible to give output polarity. Hybrid multilevel inverter mainly eliminates higher number switches that are required to produce output levels. A single phase hybrid inverter for seven levels is shown in Figure 1.

Figure 1. Single phase seven level hybrid multilevel inverter

It consists of three isolated sources and ten switches. High frequency switches will generate the required output levels without polarity. Later, the output voltage polarity is decided by the switches that has low frequency which is a full bridge converter. This concept can be applied to any number of voltage levels just by duplicating the state that is represented in the middle of Fig.1. Moreover, conventional seven level multilevel inverters using sinusoidal pulse width modulation requires six carriers, but three carriers are sufficient for hybrid multilevel inverter. The various switching modes for a seven-level hybrid inverter are shown in Table 1 for generating the required levels. There are six switching patterns to control seven level hybrid inverter.

Table 1. Switching States for Single Phase Seven Level Hybrid Inverter

|  | Modes | Level 0  | Level 1  | Level 2  | Level 3 |  |  |

|--|-------|----------|----------|----------|---------|--|--|

|  | 1     | S2,S3,S4 | S2,S3,S5 | S2,S6,S5 | S1,S5   |  |  |

|  | 2     |          | S2,S4,S6 | S1,S4    |         |  |  |

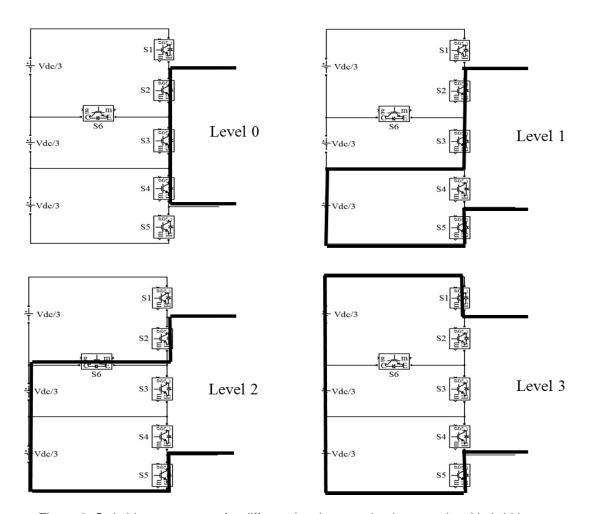

The sequences of switches (S2–S3-S4), (S2-S3-S5), (S2-S6-S5), and (S1-S5) are shown in Figure 2 for levels from 0 to 3.

Figure 2. Switching sequences for different level generation in seven level hybrid inverter

From the above figure it is clear that the number of switches in the hybrid inverter that conduct the circuit current is lower than the conventional multilevel inverters. This is helpful for better efficiency of the converter. In the following discussion, the multicarrier based sinusoidal pulse width modulation techniques implemented for hybrid inverter are discussed.

## 2.1. Phase Disposition Technique for Hybrid Inverter

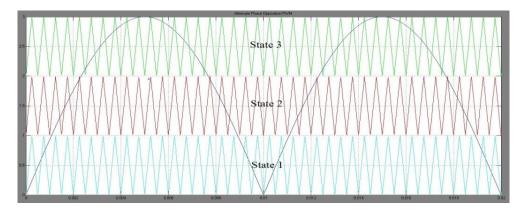

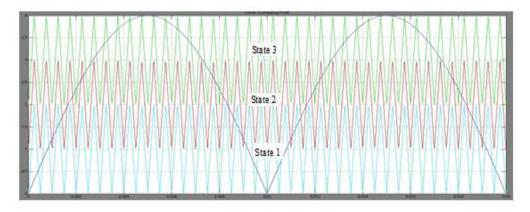

A single phase seven level hybrid multilevel inverter using phase disposition sinusoidal pulse width modulation methods needs only three carrier waveforms and a sinusoidal reference signal as shown from Figure 3 to produce seven levels.

Figure 3. PD SPWM technique for seven level hybrid inverter

#### 2.2. Alternate Phase Opposition Disposition Technique for Hybrid Inverter

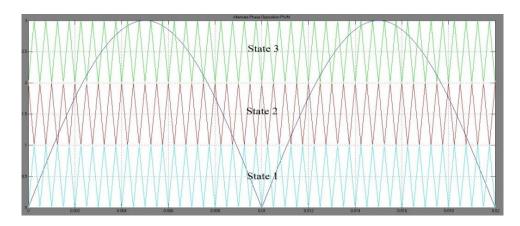

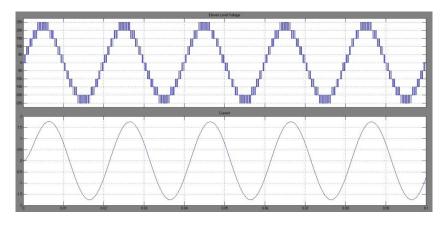

The carrier waveform of a single phase seven level hybrid multilevel inverter using alternate phase opposition disposition sinusoidal pulse width modulation method is shown in Figure 4.

Figure 4. APOD SPWM technique for seven level hybrid inverter

## 2.3. Carrier Overlapping Technique for Hybrid Inverter

Figure 5 depicts the carrier waveform of a single phase seven level hybrid multilevel inverter using carrier overlapping sinusoidal pulse width modulation method.

Figure 5. CO SPWM technique for seven level hybrid inverter

## 3. Result and Discussion

The single-phase seven level, nine level and eleven level hybrid inverters are performed. The simulation model of hybrid inverter for seven levels using R load is depicted in Figure 6.

Figure 6. Simulation model of single phase seven level inverter

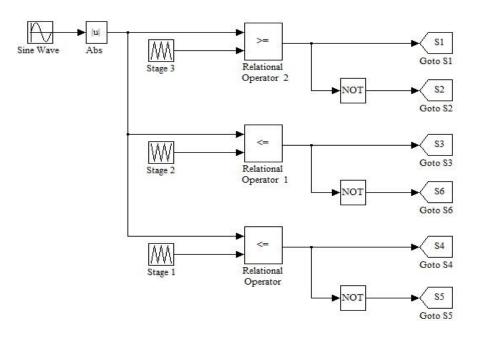

The simulation model for producing gating signals in level generation stage of seven level hybrid inverter is represented in Figure 7 using alternate phase opposition disposition pulse width modulation method.

Figure 7. Simulation model for gating signals of level generation part

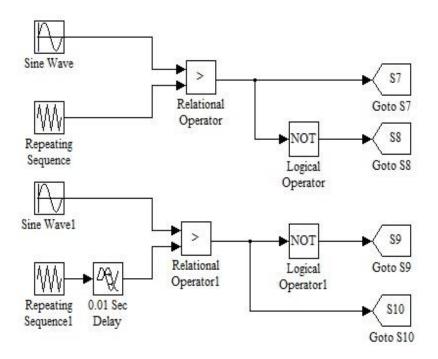

Figure 8 presents the simulation model for producing gating signals in polarity generation stage of seven level hybrid inverter.

Figure 8. Simulation model for gating signals of Polarity Generation Part

The results are shown for alternate phase opposition disposition methods for modulation index ma =0.9.

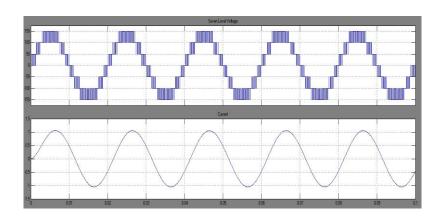

# 3.1. Single Phase Seven Level Hybrid Inverter

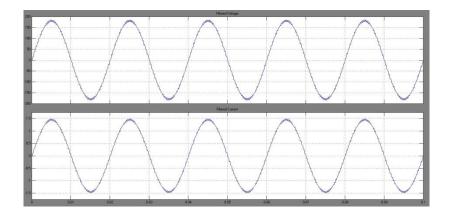

The results obtained for single phase seven level hybrid multilevel inverter are shown from Figure 9 to Figure 11.

Figure 9. Voltage and current waveforms of seven level inverter for R load

Figure 10. Voltage and current waveforms of seven level inverter for R load using LC filter

Figure 11. Voltage and current waveforms of seven level inverter for R-L load

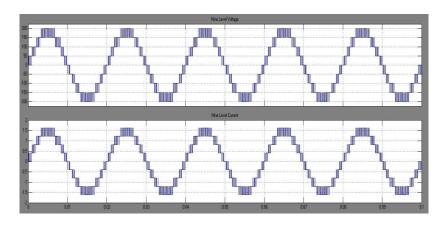

# 3.2. Single Phase Nine Level Hybrid Inverter

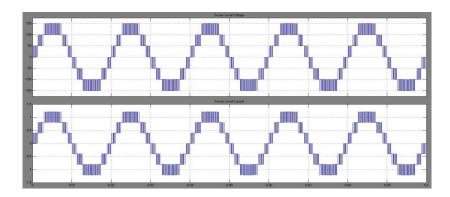

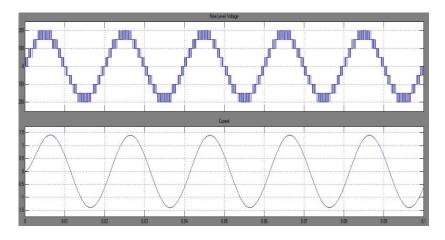

Figure 12 to Figure 14 represents the results for single phase nine level hybrid multilevel inverter.

Figure 12. Voltage and current waveforms of nine level inverter for R load

Figure 13. Voltage and current waveforms of nine level inverter for R load using LC filter

Figure 14. Voltage and current waveforms of nine level inverter for R-L load

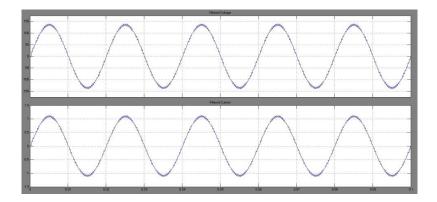

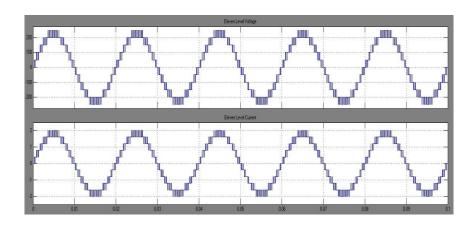

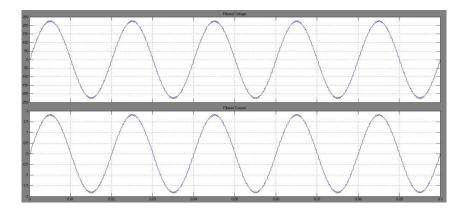

# 3.3. Single phase eleven level hybrid inverter

The waveforms of single phase eleven level hybrid multilevel inverter are shown from Figure 15 to Figure 17.

Figure 15. Voltage and current waveforms of eleven level inverter for R load

Figure 16. Voltage and current waveforms of eleven level inverter for R load using LC filter

Figure 17. Voltage and current waveforms of eleven level inverter for R-L load

# 3.4. Comparative Analysis of Single Phase Hybrid Inverters

FFT analysis is carried out for different levels of single phase hybrid multilevel inverter at various modulation indices using phase disposition, alternate phase opposition disposition and carrier overlapping sinusoidal pulse width modulation techniques. The Comparision of the above mentioned techniques for R-load is summarized in Table 2 for seven level. Whereas Table 3 and Table 4 summarizes the THD of nine level inverter and eleven level inverter for R-load.

|         |           |           |       |        | _        |           | _      |

|---------|-----------|-----------|-------|--------|----------|-----------|--------|

| Tahla 2 | . THD (%) | of Single | Dhaca | Hybrid | Invertor | for Savan | ו בעבו |

|         |           |           |       |        |          |           |        |

|       |                | . <u> </u> | 0 1 11000 1 1 1 1011 | <u> </u>           | 00.0 =0.0. |      |

|-------|----------------|------------|----------------------|--------------------|------------|------|

| $m_a$ |                | Sii        | ngle phase seven     | level hybrid inver | rter       |      |

|       | Without Filter |            |                      | •                  |            |      |

|       | PD             | APOD       | CO                   | PD                 | APOD       | CO   |

| 0.85  | 12.29          | 12.21      | 14.71                | 1.13               | 1.10       | 6.97 |

| 0.9   | 11.48          | 11.56      | 13.88                | 1.05               | 1.02       | 6.38 |

| 0.95  | 11.08          | 11.12      | 12.99                | 1.00               | 0.99       | 6.04 |

| 1     | 9.84           | 9.70       | 12.08                | 0.92               | 0.86       | 5.83 |

Table 3. THD (%) for Single Phase Hybrid Inverter for Nine Level

| m <sub>a</sub> | Single phase nine level hybrid inverter |                |       |             |      |      |  |  |

|----------------|-----------------------------------------|----------------|-------|-------------|------|------|--|--|

|                |                                         | Without Filter |       | With Filter |      |      |  |  |

|                | PD                                      | APOD           | CO    | PD          | APOD | CO   |  |  |

| 0.85           | 9.05                                    | 8.96           | 11.54 | 0.81        | 0.78 | 6.25 |  |  |

| 0.9            | 8.60                                    | 8.53           | 10.84 | 0.92        | 0.83 | 5.71 |  |  |

| 0.95           | 8.40                                    | 8.37           | 10.25 | 0.84        | 0.74 | 5.37 |  |  |

| 1              | 7.38                                    | 7.44           | 9.47  | 0.81        | 0.69 | 5.22 |  |  |

Table 4. THD (%) for Single Phase Hybrid Inverter for Eleven Level

| m <sub>a</sub> | Single phase eleven level hybrid inverter |                |      |             |      |      |  |  |

|----------------|-------------------------------------------|----------------|------|-------------|------|------|--|--|

|                |                                           | Without Filter |      | With Filter |      |      |  |  |

|                | PD                                        | APOD           | CO   | PD          | APOD | CO   |  |  |

| 0.85           | 7.17                                      | 7.34           | 9.93 | 0.79        | 0.72 | 5.59 |  |  |

| 0.9            | 6.78                                      | 7.00           | 9.15 | 0.8         | 0.71 | 5.01 |  |  |

| 0.95           | 6.58                                      | 6.52           | 8.51 | 0.83        | 0.71 | 4.71 |  |  |

| 1              | 6.09                                      | 6.02           | 7.79 | 0.77        | 0.66 | 4.65 |  |  |

Table 5 summarizes the comparision of phase disposition, alternate phase opposition disposition and carrier overlapping techniques for seven level, nine level and eleven level hybrid multilevel inverters with R-L load.

Table 5. Current THD (%) for Single Phase Hybrid Multilevel Inverter

| ma   | Seven level inverter |      |      | Nine level inverter |      |      | Eleven level inverter |      |      |

|------|----------------------|------|------|---------------------|------|------|-----------------------|------|------|

|      | PD                   | APOD | CO   | PD                  | APOD | CO   | PD                    | APOD | CO   |

| 0.85 | 0.28                 | 0.28 | 3.42 | 0.21                | 0.20 | 3.22 | 0.17                  | 0.16 | 2.94 |

| 0.9  | 0.26                 | 0.27 | 2.82 | 0.20                | 0.20 | 2.61 | 0.17                  | 0.16 | 2.39 |

| 0.95 | 0.25                 | 0.24 | 2.40 | 0.19                | 0.18 | 2.18 | 0.16                  | 0.15 | 1.94 |

| 1    | 0.22                 | 0.22 | 2.18 | 0.17                | 0.16 | 1.96 | 0.14                  | 0.14 | 1.74 |

#### 4. Conclusion

The phase disposition, alternate phase opposition disposition and carrier overlapping SPWM control methods are implemented in this paper to drive the single phase hybrid multilevel inverter for different levels at various modulation indices. The hybrid inverter requires less number of high frequency switches when compared to any other multilevel inverters.

It is observed that the hybrid inverter has superior features compared to diode clamped inverter, cascaded inverter and flying capacitor inverter in terms of the required switches, control requirements, cost, reliability and efficiency. In the proposed topology, the switching operation is separated into high and low-frequency parts. It is possible because of generating only positive carriers for pulse width modulation control. The results obtained from simulation also illustrate the performance and effectiveness of the hybrid inverter for both R and R-L loads. The components required for different voltage levels for single phase hybrid inverter are lower compared to conventional multilevel inverters. The hybrid inverter is a good potential for FACTS, STATCOM and HVDC applications. As the hybrid inverter requires low rated dc sources, the fuel cells, photovoltaic arrays can also be used as dc sources

## **Acknowledgements**

We thank the Science and Engineering Research Board (SERB), Government of India, New Delhi for providing Research Project under 'Fast Track Scheme for Young Scientists' to carry out the Research on Multilevel Inverters.

#### References

- [1] A Nabae, I Takahashi, A Akagi. A new neutral-point clamped PWM inverter. *IEEE Trans. Ind. Appl.* 1981: 19: 518–523.

- [2] G Mondal, K Gopakumar, P N Tekwani, E Levi. A reduced switch-count five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive. *IEEE Trans. Ind. Electron.* 2007; 54 (4): 2344–2351.

- [3] P M Bhagwat, V R Stefanovic. Generalized structure of a multilevel PWM inverter. *IEEE Trans. Industry Applications*. 1983; 19 (6): 1057-1069.

- [4] A Rufer. An aid in the teaching of multilevel inverters for high power applications. Proc. Rec. IEEE PESC'95. 1995; 347–352.

- [5] L M Tolbert, F Z Peng, and T. G. Habetler.Multilevel converters for large electric drives. *IEEE Trans. Ind. Appl.* 1999; 35 (1): 36–44.

- [6] N Susheela, P Satish Kumar, C H Reddy. Performance Analysis of Four Level NPC and NNPC Inverters using Capacitor Voltage Balancing Method. IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering. Varanasi. 2016; 212-217.

- [7] G Carrara, S Gardella, M Marchesoni, R Salutari, G Sciutto. A new multilevel PWM method: a theoretical analysis. *IEEE Trans.Power Electronics*. 1992; 7 (3): 497–505.

- [8] J Rodriguez, J S Lai, F Z. Peng. Multilevel inverters: A survey of topologies, controls, and applications. *IEEE Trans. Ind. Electron. 2002*; 49 (4): 724–738.

- [9] E Najafi, A H M Yatim, A S Samosir. A new topology-Reversing Voltage (RV)-for multilevel inverters. IEEE 2<sup>nd</sup> International Power and Energy Conference (PECon 08). 2008; 604 – 608.

- [10] S A Gonzalez, M I Valla, C F Christiansen. Analysis of a cascade asymmetric topology for multilevel converters. Proc. IEEE ISIE. 2007; 1027–1032.

- [11] N Susheela, P Satish Kumar, B Sirisha, "Hybrid Topologies of Multilevel Converter for Current Waveform Improvement", *International Journal of Inventive Engineering and Sciences 2013*; 1 (4): 29-37.

- [12] E Beser, B Arifoglu, S Camur, E K. Beser. Design and application of a single phase multilevel inverter suitable for using as a voltage harmonic source. *J. Power Electron. 2010;* 10 (2): 138–145.

- [13] G M Martins, J A Pomilio, S Buso, G Spiazzi. Three-phase low frequency commutation inverter for renewable energy systems. *IEEE Trans. Ind. Electron.*2006; 53 (5): 1522–1528.

- [14] Ehsan Najafi, Abdul Halim Mohamed Yatim. Design and Implementation of a New Multilevel Inverter Topology. *IEEE Transactions on Industrial Electronics*. 2012; 59 (11):4148-4154.

- [15] E Babaei. Optimal topologies for cascaded sub-multilevel converters. J. Power Electron. 2010; 10 (3): 251–261.

- [16] C Govindaraju, K Baskaran. Analysis and implementation of multiphase multilevel hybrid single carrier sinusoidal modulation. *J. Power Electron.*2010; 10 (4): 365–373.

- [17] R Stala. Application of balancing circuit for dc-link voltages balance in a single-phase diodeclamped inverter with two three-level legs. IEEE Trans. Ind. Electron.2011; 58 (9): 4185–4195.

- [18] B Sirisha, N Susheela, P Satish kumar "Three Phase Two Leg Neutral Point Clamped Converter with output DC Voltage Regulation and Input Power Factor Correction" *International Journal of Power Electronics and Drive System (IJPEDS)*, 2012; 2, (2):138 -150.

- [19] B Ravikumar, P Satish Kumar "Performance Analysis of Modified SVPWM Strategies for Three Phase Cascaded Multi-level Inverter fed Induction Motor Drive", *International Journal of Power electronics drives (IJPEDS)*, 2017; 8 (2): 835-843.