## Interlined dynamic voltage restorer using time-domain methodologies with Z-source inverter/voltage source inverter

# Chandrasekar Anuradha<sup>1</sup>, Rathinam Anantha Raman<sup>2</sup>, Ganesan Arunsankar<sup>3</sup>, Maharajan Robinson Joel<sup>4</sup>, Pitchamuthu Sathyanathan<sup>5</sup>, Hanumaji Kantari<sup>6</sup>, Subbiah Murugan<sup>7</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Faculty of Engineering and Technology, SRM Institute of Science and Technology, Kattankulathur, India

<sup>2</sup>Department of Computer Science and Engineering, KoneruLakshmaiah Education Foundation, Vijayawada, India <sup>3</sup>Department of Electronics and Communication Engineering, Gojan School of Business and Technology, Chennai, India

<sup>4</sup>Department of Information Technology, Kings Engineering College, Chennai, India

<sup>5</sup>Department of Electrical and Electronics Engineering, VelTechRangarajanDr.Sagunthala R&D Institute of Science and Technology, Chennai, India

<sup>6</sup>Department of Electrical and Electronics Engineering, Bharath Institute of Higher Education and Research, Chennai, India <sup>7</sup>Department of Biomedical Engineering, Saveetha School of Engineering, Saveetha Institute of Medical and Technical Sciences, Saveetha University, Chennai, India

#### Article Info

#### Article history:

Received Oct 16, 2023 Revised May 25, 2024 Accepted Jun 5, 2024

#### Keywords:

Dynamic voltage restorer IDVR MSRF Voltage sag and power quality Z-source inverter

### ABSTRACT

Electronic devices and loads are very sensitive to the voltage disturbances like voltage sag and voltage swell. Significant financial losses and safety issues may emerge from voltage sags and interruptions, which can be caused by variables such as system breakdowns and load changes. In order to protect against voltage fluctuations and keep vital loads running, dynamic voltage restorers (DVRs) have become more popular. To mitigate the voltage disturbances, an interlined DVR (IDVR) using a Z-source inverter (ZSI) is developed to protect the sensitive devices and loads. Back-to-back DVR connects the distributed feeders with a common direct current (DC) link. The IDVR compensates for the sag voltage and supplies the energy to control the power flow. In addition, proposed a modified synchronous reference frame (MSRF)/direct quadrature theory, hysteresis controller, and proportional integral (PI) controller, which provides the required amount of signals for a ZSI and voltage source inverter control (VSD. MATLAB/Simulink validated the simulation results. The experimental findings show that the suggested system can be implemented successfully and is effective at reducing voltage dips and interruptions, allowing crucial loads to keep operating consistently and without interruption in residential as well as commercial environments.

This is an open access article under the <u>CC BY-SA</u> license.

#### **Corresponding Author:**

Chandrasekar Anuradha Department of Electrical and Electronics Engineering, Faculty of Engineering and Technology SRM Institute of Science and Technology Kattankulathur, Chennai, Tamil Nadu, India Email: anuradhc@srmist.edu.in

#### 1. INTRODUCTION

Voltage fluctuations are a power quality issue that can seriously harm users with sensitive loads [1]. System errors, load fluctuations, energization of heavy loads, and poorly built systems are typically to blame for these disruptions. Uninterruptible power supply (UPS), constant voltage transformers, and tap-changing transformers are common traditional techniques for reducing voltage fluctuations. Utilizing specialized power

equipment, such as a dynamic voltage restorer (DVR), is a way to improve the quality of the power [2]. To meet the need for actual power, external energy storage is required. Therefore, a DVR's capacity is determined by the highest actual power delivered to the load during voltage sag mitigation. The DVR is a device circuit that recognizes sags or swells and links a voltage source in series with the supply voltage to maintain the load voltage within the set tolerance limits [3], [4]. It is often put in a distribution network at the point of common coupling (PCC) between the essential load feeder and the supply. The IDVR structure comprises many DVRs connected by a common DC connection. Each is situated in a separate feeder, protecting sensitive loads from voltage sags [5]. The other DVRs in an IDVR structure work in a rectification state and provide the direct current (DC) link with power to keep its voltage constant when one of them begins to absorb the power factor from a common DC link to correct the voltage sag [6], [7].

One of the most recent power electronics designs is ZSI. The ZSI features a special impedance network of two capacitors and inductors to couple the power source with the inverter's main circuit. Combining two linear energy storage components, L and C, creates the fundamental impedance source network. Inverters can function in the shoot-through mode because ZSI can improve the boost performance of the inverter's alternating current (AC) output voltage [8]. ZSI is a one-stage energy processing buck-boost inverter with unique passive input circuits that use the shoot-through of the power supply. An inverter bridge is used to increase the DC input voltage. The ZSI impedance network stores electricity and ensures a double filtration grade at the inverter's input [9]. The DC supply is converted to AC by the DVR with Z-source, reducing voltage-related problems such as voltage swells or sags in a distribution network caused by abruptly switching a balanced three-phase non-linear load [10].

By a tiny difference, the modified synchronous reference frame (MSRF) approach is identical to the SRF [11]. The (Idq) instantaneous current component technique is another term. In contrast to the phase-locked loop (PLL) [12] used in the SRF approach, the MSRF method obtains the transformation angle using the voltages of the AC network. For this, in a process known as clark's transformation, comparable to the approach, the stationary coordinate system of three-phase a-b-c would be first changed to a two-phase  $\alpha$ - $\beta$  system [13]. The next transformation, park's transformation, turns this two-phase  $\alpha$ - $\beta$  stationary coordinate system ordinate system [14]. A hysteresis controller raises the load voltage and chooses the inverter gates' switching signals [15]. Between the DVR reference voltage (Vref) and injection voltage (Vinj), an error signal that generates appropriate control signals is the basis of the hysteresis voltage control. A hysteresis relay will set a hysteresis band with a specific tolerance value [16]. It provides the inverter'sswitches with suitable gate pulses, generating the necessary voltage to mitigate power quality issues [17]. The use of DVR may be improved to lower the dynamic response time for managing voltage sag in the power system by employing the ZSI system under the control of a proportional integral (PI) controller layout [18]. The steady-state error for a step input is zero due to the PI controller's integral term.

The design of a discrete-time control strategy for mitigating unbalanced and balanced voltage instability in a DVR is presented [19]. To obtain an error of zero-tracking for the fundamental element in the event of balanced voltage sags, the system is based on a design with two nested regulators, one of which employs a necessary action, and the scheme is implemented in the SRF [20]. Uncertainty and disturbance estimator (UDE)-based framework control technique is presented to enhance the DVR's reaction to correctly adjust the load voltage under a range of power quality challenges, especially those connected to grid voltage disturbances [21]. Every type of disruption in the power system must be compensated for and acknowledged for it to function normally and efficiently [22]. Various custom power devices (CPDs) are utilized to address these problems [23]. DVR controls voltage under unbalanced load conditions and load imbalance [24]. The power quality enhancement uses fuzzy logic controllers and PI controllers. Total harmonic distortion (THD) and the device's performance are compared. A battery performance-monitoring device is used for photovoltaic control and monitoring system [25]. The conventional ziegler-nichols (ZN) technique tunes the PI derivative (PID) controller parameters. Subsequently, the adjusted parameters acquired from the ZN-PID controller are optimized via a method of optimization that relies on the reduction of the incorporated absolute error [26], [27]. The smart energy meter controls and computes the energy expenditure utilizing Espressif Systems8266 [28], [29]. The objective of Bayesian algorithm to improve energy and share the data well [30].

Problem statement and main contribution: existing DVRs can only manage voltage disturbances at a high cost and with limited efficiency. VSIs are common in conventional DVRs, and these devices use complex control techniques based on the SRF and PI controllers. These devices are helpful in decreasing voltage dips and power cuts, but they have certain drawbacks. Energy efficiency cannot always be maximized, and VSIs may limit the voltage increase capabilities of DVRs. This creates a serious problem for DVRs, which must keep voltage quality at a high level while using as little energy as possible.

The suggested system's main contribution is the novel and efficient method that it employs to restore voltage and improve power quality in electrical distribution networks. With Z-source inverters (ZSI) and the SRF direct quadrature control approach, voltage restoration may be precisely and quickly controlled.

ZSIs provide a number of integrated benefits that make them ideal for resolving voltage drops and power outages quickly and effectively. When compared to conventional DVRs based on VSI, the system's capacity to maintain greater voltage levels during disruptions is remarkable. IDVR and related advancements will be extensively explored in the subsequent sections of this article.

#### 2. PROPOSED METHOD

#### 2.1. Basic operations of IDVR

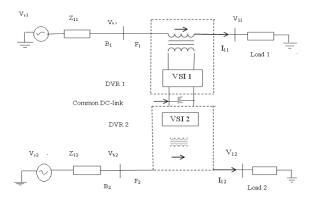

Thesystem comprises many DVRs in various feeders (F) with a common DC-link. A two-line IDVR system utilizes two DVRs that are back-to-back coupled to two Fs, with one of the DVRs compensating for voltage swell/sag and another DVR operating in power-flow control mode. The DC source is supplied through the commonly linked capacitor between the two Fs. The IDVR system comprises many DVRs in various F that share a common DC-link. A two-line IDVR system utilizes two DVRs that are back-to-back coupled to two Fs, with one of the DVRs compensating for voltage swell/sag and another DVR operating in power-flow control mode. The DC source is supplied through the commonly linked capacitor between the two Fs. Generally, due to the more considerable electrical distance of the transmission system, the voltage sag/swell is produced. The IDVR system connects the two different Fs with two grid substations. It implies in F1. The voltage distortion would be a lesser impact on F2. The DVR is coupled in series with the F, and a common DC link links DVRs from different Fs. The DVR is connected in series to the non-linear loads (1&2) across each F. Figure 1 explains a schematic diagram of IDVR.

The injection of a suitable voltage necessitates a particular quantity of reactive power (Q) and real or active (P), which the DVR must supply. P is provided by an energy storage facility linked to the DC link. In an AC power system, capacitors are often employed to create Q. Capacitors, on the other hand, may be utilized to store energy in a DC system. The capacitor terminal voltage lowers when energy is extracted from the capacitors. As a result, considerable capacitors in DC-link energy storage are required to efficiently minimize voltage swell of great depth and length. After the fault can be corrected and the supply can be operated under normal conditions, the DVR supplies the energy from the normal system. The capacitor bank rating depends on the load, which can protect the duration of sag depth. Whereas the sag correction uses P, the power electronics are fed from the capacitor bank and ZSI.

Figure 1. Schematic diagram of IDVR

#### 2.2. Time domain methodologies

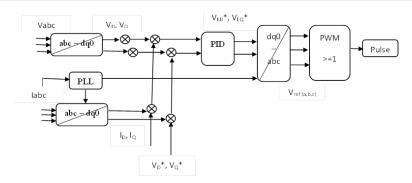

The SRF direct quadrature control method is based on a series APF compensator shown in Figure 2. During the on-grid condition, series APF provides source voltage against voltage fluctuations in the PCC. The injected source voltage and the PCC current act in the same phase. At the point when the series APF signals are sent into the PID controller, which in turn generates control signals that are transformed into pulse width modulation (PWM) switching signals in the abc domain, the synchronized decision-making process returns the pulse to the series APF converter. For a deeper understanding of the functioning controller, consider the (1) and (2).

$$V_{ED} *= V_D * -I_D, V_{ED} = V_D - I_D$$

(1)

$$V_{EQ} *= V_Q * -I_Q, V_{EQ} = V_Q - I_Q$$

<sup>(2)</sup>

Figure 2. Direct quadrature theory

#### 2.3. Hysteresis control method

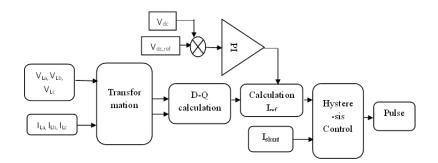

The switching sequence of the inverter, which is coupled to the shunt APF, is generated via this control mechanism. This control approach knows the stability of the systems completely, is simple to apply, and is basic. Both the reference and the current that is injected from the controlling signal are crucial to this approach. The hysteresis current regulator determines the switching pattern. When the error approaches the top of the bands, the current immediately drops since this action is established as the reference current. The current is increased automatically when the error reaches a lower limit. The relevant framework can be seen in Figure 3.

Figure 3. Block diagram of hysteresis control

#### 2.4. PLL with PI control

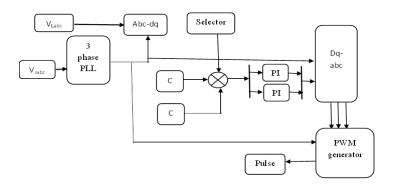

Three basic easy to understand PLL connected to the voltage source Vsabc make up the PI controller. Given the voltage load abc VLabc, the direct quadrature transform transforms it to the direct quadrature domain. Once more, the signal transforms from the direct quadrature-abc domain, and the selection is used for extracting the signals to PI at constant values. Here, the PWM generator controls the signals and, in the end, supplies the series APF compensator with a pulse. Figure 4 explains a PI control.

Figure 4. PI control

2.5. ZSI

A power inverter, typically described as a ZSI. Due to its distinctive circuit design acts as a buckboost inverter without using a DC-DC converter bridge. The impedance source inverter's storage of energy and filtration part is a combined networking circuit. One feature that is provided by an impedance source inverter is the second-order filter. When it comes to reducing voltage and current ripples, this approach performs better. Another distinction is that the inductor and capacitor requirements should be lesser than of a conventional inverter.

#### 3. SIMULATION AND RESULTS

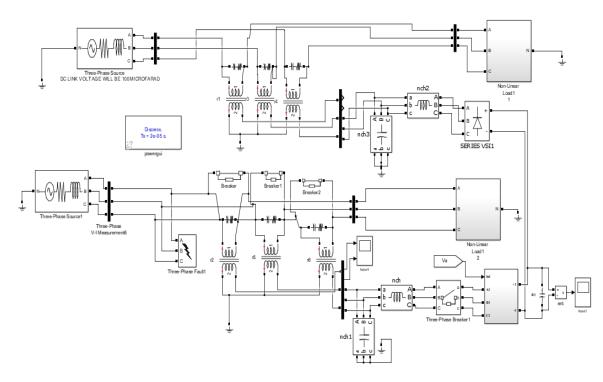

The IDVR system's thorough simulation comprises multiple feeders with parameters that must be performed using MATLAB/Simulink. MATLAB provides great performance for the simulation, an interactive system shown in Figure 5. A comprehensive simulation of a basic IDVR system consisting of two 11 KV voltage lines was performed. Two lines supply 230 VA loads with a unity power factor.

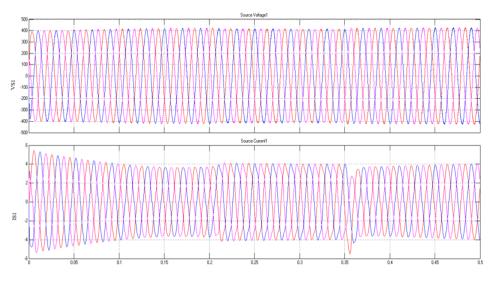

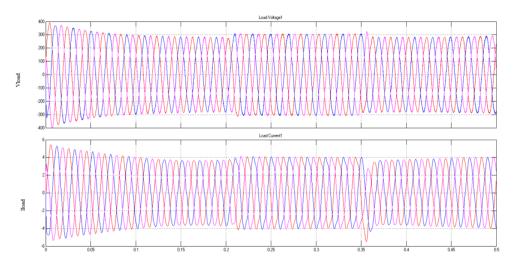

The two line supplies are three-phase sources with 50 Hz, 3-phase short circuit level at base voltage is 100 mVA, 25 MVrms, and X/R ratio is 10. Then the sources are connected to the DVR, implemented through the linear windings transformer with the nominal power and frequency of 4 KV and 50 Hz. The series RC elements are implemented in the range of 1  $\Omega$  and 100  $\mu$ F. The transformer is linked to the three-phase LC circuit to filter purposes with the content of 100 mH and 250 F. Then the line is connected to the series VSI, which is linked with the common DC link voltage. The fault is produced in line two, and the fault circuit breaker is used to diagnose the fault. As well as the breaker should select the external switching time of fault duration [0.2 0.35]. Likewise, a three-phase parallel LC branch with 370 mH and 0.19 F injects the voltage and current compensation of the power quality issues. Figure 6 illustrates the proposed system's source voltage (Vs) and source current (Is). The Vs and Is are 400 V and 4 A, respectively. Figure 7 represents the interlined first line's load voltage (VL1) and load current (IL1), which are not faulted. This first DVR dynamically replenishes the energy in the common DC link. The IDVR's performance and restoration capacity were evaluated using MATLAB/Simulink simulation.

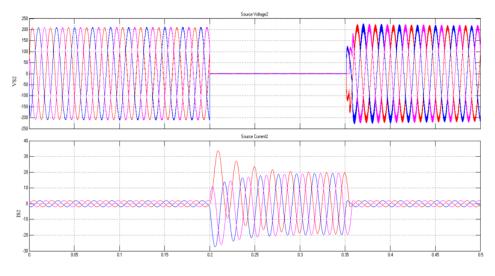

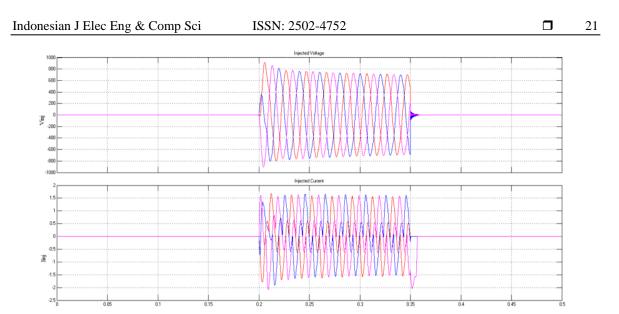

The system was exposed to 100% sag, shown in Figure 8. The transient performance at the sagging front and recovery were studied during simulations. The performance was also analyzed when the DC voltage dropped during a long sag. However, DVR's energy storage capabilities are limited, typically comprised of capacitors. Figure 9 shows the injected voltage and current second IDVR. The voltage should be injected from 800 V to 600 V during 0.2s to 0.35s to mitigate the voltage sag in IDVR. Then the current is injected to 1.5 A from 0.2s to 0.35s.

Figure 5. Simulation circuit of the proposed IDVR

Interlined dynamic voltage restorer using time-domain methodologies ... (Chandrasekar Anuradha)

Figure 6. Source voltage and current of the interlined IDVR system

Figure 7. Load voltage and load current of the first line interlined IDVR system

Figure 8. Vs2 and Is2 of without compensation

Figure 9. Injected voltage and current

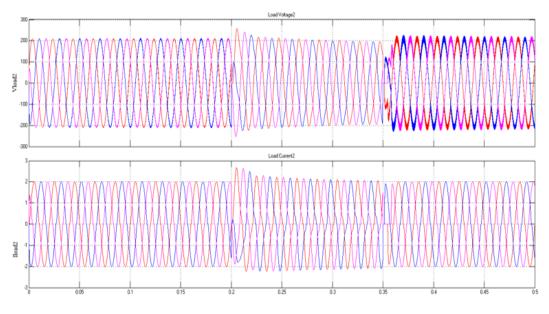

As a result, it must be studied how to limit injection energy while keeping the load voltage near the pre-fault value. When operational, the DVR's architecture permits P and Q to be provided or absorbed. If a minor defect develops on the protected system, the DVR can rectify it using just internal Q. The DVR may be necessary to create P to restore significant defects. An energy storage device is required to enable the development of P; the DVR design currently employs a capacitor bank. Figure 10 illustrates the voltage and current compensation of the IDVR system using the MSRF control technique. The compensated voltage is 200b V, and 2 A is supplied to the non-linear loads.

Figure 10. Compensated voltage and current

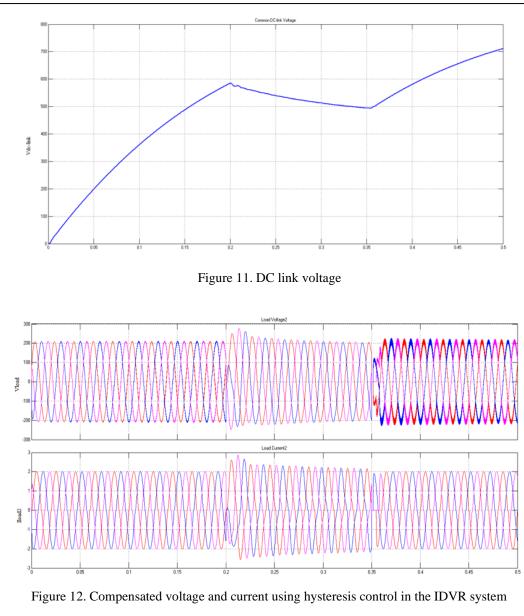

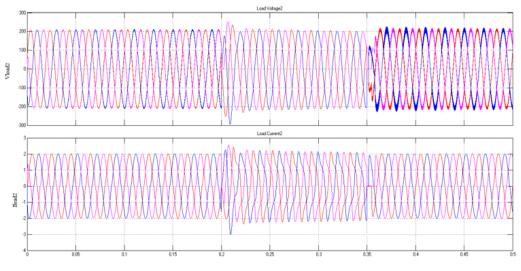

Figure 10 demonstrates the simulated voltage waveforms across loads 1 and 2 with IDVR employing a hysteresis controller system and a shared DC link voltage. It also indicates utilizing the inverter's buck-boost capability. The IDVR operating ZSI may store energy in the common DC link during the voltage compensation process. Figure 11 represents the compensated voltage and current using hysteresis control and Figure 12 demonstrates the compensated voltage and current using PI controlling the IDVR system. This compensation is slightly different than using the proposed controlling technique.

Interlined dynamic voltage restorer using time-domain methodologies ... (Chandrasekar Anuradha)

Figure 13. Compensated voltage and current using PI control in IDVR system

The IDVR in a distributed system using various control techniques has been used to analyze the THD. THD is often created by non-linear loads employed by end consumers of electricity. Non-linear loads, which are power electronic loads, draw current in a non-sinusoidal mode. This comparative analysis shows that the MSRF/ direct quadrature theory is better than hysteresis and PI control. Table 1 explains the THD analysis of controlling techniques. This table presents ZSI and VSI. In ZSI compared to load 1 and load 2, MSRF, hysteresis, and PI control are higher. Also, in VSI, load 2 is higher than load 1.

| Table 1. THD analysis of controlling techniques |        |        |        |        |

|-------------------------------------------------|--------|--------|--------|--------|

| Methods                                         | ZSI    |        | VSI    |        |

|                                                 | Load 1 | Load 2 | Load 1 | Load 2 |

| MSRF/direct quadrature                          | 3.45%  | 4.34%  | 3.47%  | 4.52%  |

| Hysteresis control                              | 3.45%  | 4.60%  | 3.70%  | 4.37%  |

| PI control                                      | 4%     | 4.14%  | 4.10%  | 4.68%  |

#### 4. CONCLUSION

This IDVR is used to improve the multiline power quality and is economical. This proposed IDVR system uses several DVRs commonly connected DC links. The proposed IDVR system has two interlined DVR and the IDVR's control strategy utilizes a multi-loop feedback control mechanism that is identical for voltage compensation and P regulation. The designed IDVR system and its PI and hysteresis controller were evaluated using MATLAB/Simulink simulations. It was discovered that the IDVR efficiently adjusts for sag disruptions while fully utilizing the common DC-link via the ZSI's buck-boost capabilities via the MRSF controller. The proposed IDVR system's limiting factor is that the amount of power that can transmit from on line to the DC-link power storage depends on the load power factor. According to the simulation, a two-line IDVR system may minimize voltage sag with a longer duration emerging in one line. IDVR modeling research for distribution line power flow control and voltage stabilization. The simulation results demonstrate the IDVR's unique capacity to rectify power imbalance in a distribution network with more than two lines and receive end voltage stability of a line at the sub-station utilizing ZSI for MRSF/direct quadrature, hysteresis and PI controller.

#### REFERENCES

- M. Moradlou and H. R. Karshenas, "Design strategy for optimum rating selection of interline DVR," *IEEE Transactions on Power Delivery*, vol. 26, no. 1, pp. 242–249, Jan. 2011, doi: 10.1109/TPWRD.2010.2071403.

- [2] S. Aali and D. Nazarpour, "Voltage quality improvement with neural network-based interline dynamic voltage restorer," *Journal of Electrical Engineering and Technology*, vol. 6, no. 6, pp. 769–775, Nov. 2011, doi: 10.5370/JEET.2011.6.6.769.

- [3] M. Sharanya, B. Basavaraja, and M. Sasikala, "An overview of dynamic voltage restorer for voltage profile improvement," *International Journal of Engineering and Advanced Technology*, no. 22, pp. 2249–8958, 2012, doi: 10.13140/RG.2.2.28072.06407.

- [4] M. Shahabadini and H. Iman-Eini, "Improving the performance of a cascaded h-bridge-based interline dynamic voltage restorer," *IEEE Transactions on Power Delivery*, vol. 31, no. 3, pp. 1160–1167, Jun. 2016, doi: 10.1109/TPWRD.2015.2480967.

- [5] H. F. Ahmed and H. Cha, "A new class of single-phase high-frequency isolated Z-source AC-AC converters with reduced passive components," *IEEE Transactions on Power Electronics*, vol. 33, no. 2, pp. 1410–1419, Feb. 2018, doi: 10.1109/TPEL.2017.2686903.

- [6] P. Suresh and B. Baskaran, "Reduction of line losses by using interline dynamic voltage restorer," *International Journal of Control Theory and Applications*, vol. 9, no. 25, pp. 417–422, 2016.

- [7] N. Saeed, A. Ibrar, and A. Saeed, "A review on industrial applications of Z-source inverter," *Journal of Power and Energy Engineering*, vol. 05, no. 09, pp. 14–31, 2017, doi: 10.4236/jpee.2017.59002.

- [8] M. Prasad, A. K. Akella, and A. Youssef, "Design and analysis of solar photovoltaic fed Z-source inverter based dynamic voltage restorer," *Scientia Iranica*, vol. 27, no. 6 D, pp. 0–0, Feb. 2019, doi: 10.24200/sci.2019.51096.2000.

- [9] N. N. Gopal and M. S. Abirami, "A dynamic voltage restorer system by modified Z-source inverter to mitigate voltage sag," *International Journal of Applied Engineering Research*, vol. 13, no. 10, 2018.

- [10] H. F. Ahmed, H. Cha, A. A. Khan, and H. G. Kim, "A family of high-frequency isolated single-phase Z-source AC-AC converters with safe-commutation strategy," *IEEE Transactions on Power Electronics*, vol. 31, no. 11, pp. 7522–7533, Nov. 2016, doi: 10.1109/TPEL.2016.2539216.

- [11] B. S. Rakhonde and P. R. Dhabe, "Power quality improvement using modifiedsynchronous reference frame theory," *International Research Journal ofModernization in Engineering Technology and Science*, vol. 4, 2022.

- [12] X. Q. Guo, W. Y. Wu, and H. R. Gu, "Phase locked loop and synchronization methods for gridinterfaced converters: A review," *Przeglad Elektrotechniczny*, vol. 87, no. 4, pp. 182–187, 2011.

- [13] P. V. Manitha and M. G. Nair, "Adapted synchronous reference frame based control for a dynamic voltage restorer," in 2019 Innovations in Power and Advanced Computing Technologies, i-PACT 2019, Mar. 2019, pp. 1–5, doi: 10.1109/i-PACT44901.2019.8960020.

- [14] B. Tian, Q. T. An, J. D. Duan, D. Semenov, D. Y. Sun, and L. Sun, "Cancellation of torque ripples with FOC strategy under twophase failures of the five-phase PM motor," *IEEE Transactions on Power Electronics*, vol. 32, no. 7, pp. 5459–5472, Jul. 2017, doi: 10.1109/TPEL.2016.2598778.

- [15] R. Manivasagam and R. Prabakaran, "Power quality improvement by UPQC using ANFIS-based hysteresis controller," *International Journal of Operational Research*, vol. 37, no. 2, pp. 174–197, 2020, doi: 10.1504/IJOR.2020.105368.

- [16] M. Rashad, M. Ashraf, A. I. Bhatti, and D. M. Minhas, "Mathematical modeling and stability analysis of DC microgrid using SM hysteresis controller," *International Journal of Electrical Power & Energy Systems*, vol. 95, pp. 507–522, Feb. 2018, doi: 10.1016/j.ijepes.2017.09.001.

- [17] E. M. Findlay and F. Udrea, "Reverse-conducting insulated gate bipolar transistor: a review of current technologies," *IEEE Transactions on Electron Devices*, vol. 66, no. 1, pp. 219–231, Jan. 2019, doi: 10.1109/TED.2018.2882687.

- [18] T. A. Naidu, S. R. Arya, R. Maurya, and S. Padmanaban, "Performance of DVR using optimized PI controller based gradient adaptive variable step LMS control algorithm," *IEEE Journal of Emerging and Selected Topics in Industrial Electronics*, vol. 2, no. 2, pp. 155–163, Apr. 2021, doi: 10.1109/JESTIE.2021.3051553.

- [19] A. P. Torres, P. Roncero-Sanchez, J. Vazquez, F. J. Lopez-Alcolea, and E. J. Molina-Martinez, "A discrete-time control method for fast transient voltage-sag compensation in DVR," *IEEE Access*, vol. 7, pp. 170564–170577, Feb. 2019, doi: 10.1109/ACCESS.2019.2955177.

- [20] A. P. Torres, P. Roncero-Sanchez, J. Vazquez, F. J. Lopez-Alcolea, and E. J. Molina-Martinez, "A discrete-time control method for fast transient voltage-sag compensation in DVR," *IEEE Access*, vol. 7, pp. 170564–170577, 2019, doi: 10.1109/ACCESS.2019.2955177.

- [21] S. D. Dehnavi, C. Negri, S. Bayne, and M. Giesselmann, "Dynamic voltage restorer (DVR) with a novel robust control strategy," *ISA Transactions*, vol. 121, pp. 316–326, Feb. 2022, doi: 10.1016/j.isatra.2021.04.010.

- [22] Sukanth, Harika, S. Jayanthu, and J. Lakshmi, "Improvement of power quality using DVR by different control techniques," *International Journal of Recent Technology and Engineering*, vol. 8, no. 3, pp. 7366–7369, Sep. 2019, doi: 10.35940/ijrte.C6123.098319.

- [23] A. P. M. Meenakumari, S. L, R. N, S. Jayaprakash, and S. Murugan, "Intelligent power control models for the IoT wearable devices in BAN networks," in 2023 International Conference on Intelligent and Innovative Technologies in Computing, Electrical and Electronics (IITCEE), Jan. 2023, pp. 820–824, doi: 10.1109/IITCEE57236.2023.10090918.

- [24] V. K. Awaar, P. Jugge, S. T. Kalyani, and M. Eskandari, "Dynamic voltage restorer–a custom power device for power quality improvement in electrical distribution systems," in *In Power Quality: Infrastructures and Control*, 2023, pp. 97–116.

- [25] Z. E. Dallalbashi, S. Alhayalir, M. J. Mnati, and A. A. A. Alhayali, "Low-cost battery monitoring circuit for a photovoltaic system based on LoRa/LoRaWAN network," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 29, no. 2, pp. 669–677, Feb. 2023, doi: 10.11591/ijeecs.v29.i2.pp669-677.

- [26] I. D. Fajuke and A. Raji, "Optimal tuning of PID controller for speed control of DC motor using equilibrium optimizer," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 30, no. 1, pp. 89–101, Apr. 2023, doi: 10.11591/ijeecs.v30.i1.pp89-101.

- [27] V. Srividhya, S. Gowriswari, N. V. Antony, S. Murugan, K. Anitha, and M. Rajmohan, "Optimizing electric vehicle charging networks using clustering technique," in 2024 2nd International Conference on Computer, Communication and Control (IC4), Feb. 2024, pp. 1–5, doi: 10.1109/IC457434.2024.10486422.

- [28] A. V. Panchbhai, R. Raman, C. B. Thacker, S. Muthumarilakshmi, and S. Murugan, "Residential electric vehicle charging station using the internet of things," in 2023 International Conference on Power Energy, Environment & Intelligent Control (PEEIC), Dec. 2023, pp. 987–991, doi: 10.1109/PEEIC59336.2023.10450569.

- [29] T. Meenakshi, R. Ramani, A. Karthikeyan, N. S. Vanitha, and S. Murugan, "Power quality monitoring of a photovoltaic system through IoT," in 2023 International Conference on Sustainable Communication Networks and Application (ICSCNA), Nov. 2023, pp. 413–418, doi: 10.1109/ICSCNA58489.2023.10370494.

- [30] M. J. Kumar, S. Mishra, E. G. Reddy, M. Rajmohan, S. Murugan, and N. A. Vignesh, "Bayesian decision model based reliable route formation in internet of things," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 34, no. 3, pp. 1665–1673, Jun. 2024, doi: 10.11591/ijeecs.v34.i3.pp1665-1673.

#### **BIOGRAPHIES OF AUTHORS**

**Dr. Chandrasekar Anuradha b X s** received her B.E. degree in Electrical and Electronics Engineering in Madras University and M.Tech. degree in Power Electronics and Drives from SRM University, in 2004 and 2010 respectively. She has done her Ph.D. on Design and analysis of multi-port converter for micro grid applications in 2021 at SRMIST. She has published more than 20 journal papers on reputed and indexed journals in the field of Renewable energy system and power electronics converters design. She also filed and published 2 patents. Her research area of interests are Renewable energy sources, electric vehicles, energy management, design of power electronic converters etc. She has been working as an Assistant Professor in the Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Kattankulathur since Feb 2007. She is a member of various professional societies like IEEE, ISCA, and MISTE. She can be contacted at email: anuradhc@srmist.edu.in.

**Dr. Rathinam Anantha Raman** (D) **S S** is an Associate Professor in the Department of Computer Science and Engineering at K L University-Vijayawada, where he has been since March, 2023. From 2017 to Feb, 2023, he served as Department Head in Malla Reddy Institute of Engineering and Technology, Hyderabad. During 2009 to 2017 he served as Associate professor in the Department of Computer Science and Engineering, Adhiyamaan College of Engineering, Hosur. He received IASTE best director award in 2018, and an he Appointed as Indian Examiner for Ph.D. VIVA VOCE by Anna University from last 6 Years. He worked as research coordinator for Ph.D. Part time Research Scholar by SRM University and he appointed as the boards of studies (BoS) member for various Engineering colleges from 2019 onwards. His research interests span both computer networking and cloud computing. He can be contacted at email: granantha.raman@gmail.com.

**D** 25

**Dr. Ganesan Arunsankar b X c** received his B.E. Degree in EEE from University of Madras, M.E. Degree in Power Systems Engineering from College of Engineering, Guindy, Anna University, Chennai. He completed his Doctorate from Department of Electrical Engineering, Anna University, Chennai, Tamilnadu, India. His research interests include soft computing application in power quality improvement. He is currently working as Associate Professor inthe department of ECE, Gojan School of Business and Technology, Chennai. He has published several papers in National and International journals. He can be contacted at g.arunsankar@gmail.com.

**Maharajan Robinson Joel B X S** received the Doctorate Ph.D. degree in Computer and Information Technology from the Manonmaniam Sundaranar University, Tirunelveli in March 2019. He completed his M.Tech. and MCA from the same university year 2008 and 2002 respectively. He is currently working as an Associate Professor in the Department of Information Technology, at Kings Engineering College, Chennai. He has 16 years of teaching experience. He can be contacted at joelnazareth@gmail.com.

**Pitchamuthu Sathyanathan D SI Solution b** working as an Assistant Professor in the Electrical and Electronics Engineering Department at Vel Tech Rangarajan Dr.Sagunthala R&D Institute of Science and Technology. He graduated in Electrical and Electronics Engineering at National Engineering College, Kovilpatti, Tamilnadu, India. He secured Master of Engineering in Power Electronics and Drives at Jerusalem College of Engineering Department at Anna University, Tamilnadu, India. He is in the field of EEE Power Electronics Domain at Vel Tech Rangarajan Dr.Sagunthala R&D Institute of Science and Technology, Chennai, Tamilnadu, India. He is in teaching profession for more than 10 years. He has presented and published many papers in National and International Journals, Conference and Symposiums. He has 7 Scopus Indexed International conferences and journals. His main area of interest includes Power Electronics, Solid State Drives and Electrical Machines. He can be contacted at sathyaeee88@gmail.com.

**Hanumaji Kantari b K s** is an educator, and researcher with over 12 years of experience. In addition to the teaching responsibilities, actively involved in research, with interests spanning Power Electronics and wind energy systems. Published numerous papers in top-tier conferences and journals, contributing valuable insights to the field. His research has addressed persistent challenges, and has been recognized with awards and honors from the academic community. In addition to the research endeavors, Hanumaji Kantari is dedicated to mentorship, education and have supervised numerous graduate students. Many of whom have gone on to successful careers in academia and industry. He can be contacted at email: hanumaji208@gmail.com.

**Subbiah Murugan (b) (S) (c)** is an Adjunct Professor, Saveetha School of Engineering, Saveetha Institute of Medical and Technical Sciences, Chennai, Tamil Nadu, India. He published his research articles in many international and national conferences and journals. His research areas include network security and machine learning. He can be contacted at email: smuresjur@gmail.com.