# Field programmable gate array implementation of edge detection system based on an improved sobel edge detector

## Duong Huu Ai<sup>1</sup>, Cong Dat Vuong<sup>1</sup>, Khanh Ty Luong<sup>2</sup>, Viet Truong Le<sup>2</sup>

<sup>1</sup>Faculty of Electronics and Computer Engineering, The University of Danang - Vietnam-Korea University of Information and Communication Technology, Danang City, Vietnam

<sup>2</sup>Faculty of Computer Science, The University of Danang - Vietnam-Korea University of Information and Communication Technology, Danang City, Vietnam

## Article Info

## Article history:

Received Sep 1, 2023 Revised Sep 16, 2023 Accepted Oct 11, 2023

## Keywords:

Algorithm for image processing Design filter Field-programmable gate array Image edge detection Image processing

## ABSTRACT

Field programmable gate array (FPGA) is an integrated circuit consisting of internal hardware blocks with programmable link connections for users to customize operations for a particular application. Link connections can be easily reprogrammed, allowing the FPGA to adapt to changes to the design or even support a new application throughout the department's uptime. One of the important tasks in image processing is image edge detection image, with computer aided, image recognition is concerned with the recognition and classification of objects in an image, so edge detection is an important tool. In this paper, we design filter for edge detection in image processing using FPGA kit. We analysis and implementation of algorithm for image processing on FPGA, load the code and run the results. Comparative analysis with images processed by MATLAB software.

This is an open access article under the <u>CC BY-SA</u> license.

## **Corresponding Author:**

Duong Huu Ai

Faculty of Electronics and Computer Engineering, The University of Danang - Vietnam-Korea University of Information and Communication Technology Ngu Hanh Son District, Danang City, Vietnam Email: dhai@vku.udn.vn

## 1. INTRODUCTION

Image processing is a sub-discipline of digital signal processing where the processed signal is an image. This is a very developed new branch of science, image processing is increasingly popular and strongly developed with many practical applications in medicine, security, transportation, security systems, automation. Applications of image processing in medicine such as ultrasound, X-ray [1]–[7]. In security, it helps in motion detection and intrusion warning. In traffic, it helps to measure speed, warn of congestion, image edge detection is one of the important tasks in image processing. Image recognition with computer aided is concerned with the recognition and classification of objects in an image, so sobel edge detection is an important tool. Edge detection remove unnecessary information and will significantly reduce the amount of data to be processed while important structural properties of the image are preserved, this issue is mentioned and researched in [8]–[16].

Field programmable gate array (FPGA) is an integrated circuit that uses logical element array structure, FPGA has a fast-processing speed, which can provide low latency or defined latency for real time applications such as image and video processing by directly importing images or videos into the FPGA. FPGAs can also satisfy a variety of functions that provide high energy efficiency. An FPGA can use part of the FPGA for a function instead of the entire chip-allowing the FPGA to store or execute multiple functions in parallel [17]–[25].

In this paper, we design filter for edge detection in image processing using FPGA kit, we analysis and implementation of algorithm for image processing on FPGA. The remainder of the paper is organized as follows. In section 2, digital image filter methods are described. In section 3, we present the filter design. The numerical results and discussions are presented in section 4, and finally, we conclude the paper in section 5.

## 2. DIGITAL IMAGE FILTER METHODS

## 2.1. Edge detection

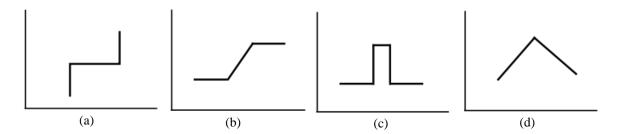

Edge detection is an technique to determine the boundaries of objects within images by detecting discontinuities of brightness, and it is an important tool in digital image processing, it is used for image segmentation and extraction of data. It significantly reduces the amount of data to be calculated, retaining only a handful of necessary information while preserving the critical structures in the image [2]. The boundary point is where adjacent pixels have a sudden change in intensity as shown in Figure 1, there are some types of borders is shown in Figure 1(a)-1(d). Borderline is a typical type of local characteristic in analysis, image recognition and helps segment the areas in the image [9].

Figure 1. Some types of borders: (a) step jump profile, (b) steep borders, (c) Square pulse borderline, and (d) cone border

## 2.2. The methods of edge detection

There are many methods of boundary detection being applied, but we can be divided into two basic groups: gradient detection and Laplacian method. Gradient detection method (using operator: Roberts, Prewitt, Sobel, Canny) is based on the maximum and maximum value of the image's top function. The Laplacian method will look for points of value 0 when taking the second-order derivative of the image [14].

Gradient-based methods, the core of gradient edge detection is, of course, the gradient operator, the first-order derivative in the horizontal and vertical direction is calculated and given by [15]:

$$\Delta f = \begin{bmatrix} G_x \\ G_y \end{bmatrix} = \begin{bmatrix} \frac{\partial f}{\partial x} \\ \frac{\partial f}{\partial y} \end{bmatrix}$$

(1)

to produce an edge detector, one may simply extend the case described earlier, the amplitude of the vector gradient or the total magnitude of the derivative value located at the boundary is a combination of both of these values according to the formula.

$$\Delta f = |\Delta f| = \sqrt{G_x^2 + G_y^2} \tag{2}$$

The direction of the vector gradient is angle of D, and is determined by (3). The direction of the boundary will be perpendicular to the direction of this vector gradient, the angle is expressed under the tang angle as follows:

angle of

$$\Delta f = \tan^{-1} \left(\frac{G_y}{G_y}\right)$$

(3)

the gradient method is only suitable for variable contrast image areas that are leap fly, which makes it difficult to detect straight lines. To overcome this weakness, we often use a second-order derivative. Laplacian method for [15].

Field programmable gate array implementation of edge detection system based on ... (Duong Huu Ai)

$$L(x,y) = \frac{\partial^2 I}{\partial x^2} + \frac{\partial^2 I}{\partial y^2}$$

(4)

Laplacian is combined with a photo smoothing filter to find the edge. If this function is performed with a picture to look for the edge, the result is that the image will be blurred, the degree of blurring depends on the value of the image. Laplacian of h i.e., order derivative of h according to r is given by [15].

$$\Delta^2 h(r) = -\left[\frac{r^2 - \sigma^2}{\sigma^4}\right] \exp\left(\frac{r^2}{2\sigma^2}\right) \tag{5}$$

In this method, the Gaussian filter is combined with Laplacian which allows the display of areas of rapidly changing image that increases the efficiency of marginal detection. It allows working with a wider area around the pixel being studied to more accurately detect the location of the boundary. The downside of this method is that the direction of the margin is not determined due to the use of two too different Laplacian filters.

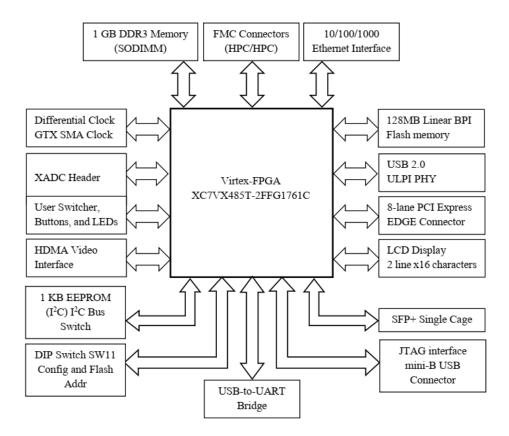

#### 2.3. Virtex-7 FPGA KIT

The Virtex-7 FPGA VC707 rating toolkit is a high-speed, flexible, fully functional serial platform of the Virtex-7 XC7VX485T-2FFG1761C, the board of Virtex-7 FPGA VC707 is shown in Figure 2. It includes the basic components of hardware, design tools, IP and preverified references designed for system designs that require high performance, serial connection and advanced memory communication. Pre-verified reference designs come with and FPGA (FMC) industry standards allow for expansion and customization with sub cards.

Figure 2. Board Virtex-7 VC707

The features of Virtex-7 FPGA VC707; 40Gb/s connectivity platform for high performance and high bandwidth applications using Virtex-7 VX485T FPGA; desigh tools, hardware, internet protocol and preverified reference designs; embedded processing support with RISC 32bit, Micro Blaze. It allows serial connections to SFP+ and SMA, PCIe Gen2x8, IIC pairs, UART; Advanced memory interface with 1GB DDR3 SODIM Memory up to 800 MHz/1600 Mbps; expand I/O with FPGA mezzanine card (FMC) interface. And it can develop network applications with 10 Mbps, 100 Mbps, 1000 Mbps Ethernet (GMII, RGMII, and SGMII).

#### 3. FILTER DESIGN

#### 3.1. Sobel edge detector

Use two masks of size  $[3 \times 3]$  where one is simply the rotation of the other by 90 degrees. These masks are designed to best outline the vertical and horizontal borders, when performing convolution between the image and these masks, we get vertical and horizontal gradients Gx, Gy. The gradient of image is a directional change of color or intensity in an image and that is one of the basic building blocks in image processing:

$$\begin{bmatrix} +1\\+2\\+1 \end{bmatrix} \times \begin{bmatrix} +1 & 0 & +1 \end{bmatrix} \rightarrow \begin{bmatrix} +1 & 0 & -1\\+2 & 0 & -2\\+1 & 0 & -1 \end{bmatrix} \text{ and } \begin{bmatrix} +1\\0\\-1 \end{bmatrix} \times \begin{bmatrix} +1 & +2 & +1 \end{bmatrix} \rightarrow \begin{bmatrix} +1 & +2 & +1\\0 & 0 & 0\\-1 & -2 & -1 \end{bmatrix}$$

(6)

$$G_{x} = \begin{bmatrix} +1 & 0 & -1 \\ +2 & 0 & -2 \\ +1 & 0 & -1 \end{bmatrix} * A \text{ and } G_{y} = \begin{bmatrix} +1 & +2 & +1 \\ 0 & 0 & 0 \\ -1 & -2 & -1 \end{bmatrix} * A$$

(7)

add the last result together.

$$\mathbf{B} = (\mathbf{A} * \mathbf{G}_{\mathbf{x}}) + (\mathbf{A} * \mathbf{G}_{\mathbf{v}}) \tag{8}$$

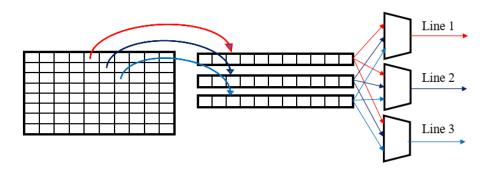

## 3.2. Line buffer

The line buffer is shown in Figure 3, an image is composed of 512\*512 pixels, that width is 512 and height is 512. With using FPGA for image processing, the pixel rows is cached and transformed in internal storage resources of FPGA, it is often necessary to open a window for the image. We design a 3-line cache for [3 x 3] window, the data of the most of image are row by row, first from left to right, and then from top to bottom output each pixel data. If we don't add processing, then we can't get the [3 x 3] image window, ultimate goal should be to make three lines of data, it is aligned and output at the same time, and then can get the [3 x 3] window of image.

Figure 3. Line buffer

In order, we need 3 FIFOs that to implement 3-Line cache, as shown in the Figure 3. Enter the first line (Line 1) of data in turn and write in to FIFO1. When the last data in the Line 1 is written, proceed to read the data from FIFO1 in turn, then write in to FIFO2. In this way, when the fourth line (Line 4) of data arrives, the three FIFOs will output data at the same time, and the output data of the three line (Line 3) is aligned.

#### 4. RESULTS AND DISCUSSION

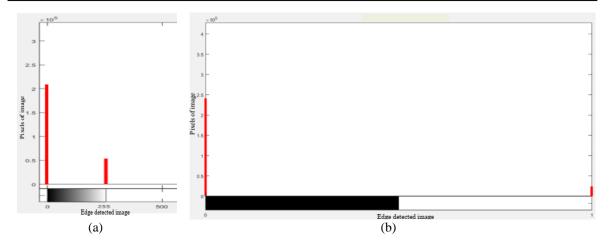

Using board of Virtex-7 FPGA VC707 (Figure 2) and perform edge detection with a grayscale image with Width of 512px and Height of 512px, a pixel count of 512' 512 equals 262,144 pixels. Then in these 262,144 pixels, there will be pixels with the same gray intensity. Let's say the bit range of that image is from 0 to 255, and bit 0 has 100 identical pixels, and bit 1 has 150 pixels. up to bit 255 is N identical pixels. And the sum of the pixels of these bits will be 262,144. Figure 4, illustrates the edge detection, with using Virtex-7 FPGA VC707 is shown in Figure 4(a) and using MATLAB is shown in Figure 4(b). As it is clearly shown, edge detection with Virtex-7 FPGA VC707 shows more detailed edges than MATLAB software.

Figure 4. Histogram edge detection (a) edge detection FPGA and (b) edge detection MATLAB

### 5. CONCLUSION

In this paper, we have presented FPGA implementation of edge detection system based on an improved Sobel edge detector. Design edge detection by FPGA to improve image processing speed and capacity and reduce intermediate process, the algorithm is mapped onto a Xilinx Virtex-7 FPGA platform. The proposed FPGA implementation takes only 0.721ms, including the SRAM read/write time and the computation time to detect edges of 512×512 images in the USC SIPI database when clocked at 50 MHz. Thus, the proposed implementation is capable of supporting fast real-time edge detection of images.

#### REFERENCES

- J. Stowers, M. Hayes, and A. Bainbridge-Smith, "Beyond optical flow biomimetic UAV altitude control using horizontal edge information," in *ICARA 2011 - Proceedings of the 5th International Conference on Automation, Robotics and Applications*, Dec. 2011, pp. 372–377, doi: 10.1109/ICARA.2011.6144912.

- [2] M. Juneja and P. S. Sandhu, "Performance evaluation of edge detection techniques for images in spatial domain," *International Journal of Computer Theory and Engineering*, pp. 614–621, 2009, doi: 10.7763/ijcte.2009.v1.100.

- [3] L. Guo and S. Wu, "FPGA implementation of a real-time edge detection system based on an improved canny algorithm," *Applied Sciences (Switzerland)*, vol. 13, no. 2, Sep. 2023, doi: 10.3390/app13020870.

- [4] D. Alghurair and S. S. Al-Rawi, "Design of sobel operator using field programmable gate arrays," in 2013 The International Conference on Technological Advances in Electrical, Electronics and Computer Engineering, TAEECE 2013, May 2013, pp. 589– 594, doi: 10.1109/TAEECE.2013.6557341.

- [5] Altera Corperation, Logic elements and logic array blocks in cyclone IV devices in cyclone IV device handbook. Cyclone IV Device Handbook, 2009.

- [6] Altera Corperation, Cyclone IV FPGA device family overview. Cyclone IV Device Handbook, 2013.

- [7] C. Wei, J. Wu, M. K. Law, P. I. Mak, and R. P. Martins, "Low complexity illumination-invariant motion vector detection based on logarithmic edge detection and edge difference," in *Proceedings - IEEE International Symposium on Circuits and Systems*, Oct. 2020, vol. 2020-October, doi: 10.1109/iscas45731.2020.9180935.

- [8] B. Du, Z. Hao, and X. Wei, "Roundness detection of end face for shaft workpiece based on canny-zernike sub pixel edge detection and improved hough transform," in *ICEIEC 2021 - Proceedings of 2021 IEEE 11th International Conference on Electronics Information and Emergency Communication*, Jun. 2021, pp. 40–43, doi: 10.1109/ICEIEC51955.2021.9463822.

- [9] C. Hui, B. Xingcan, and L. Mingqi, "Research on image edge detection method based on multi-sensor data fusion," in *Proceedings of 2020 IEEE International Conference on Artificial Intelligence and Computer Applications, ICAICA 2020*, Jun. 2020, pp. 789–792, doi: 10.1109/ICAICA50127.2020.9182548.

- [10] P. Kanchanatripop and D. Zhang, "Adaptive image edge extraction based on discrete algorithm and classical canny operator," Symmetry, vol. 12, no. 11, pp. 1–15, Oct. 2020, doi: 10.3390/sym12111749.

- [11] R. Ramya and P. S. Babu, "Automatic tuberculosis screening using canny edge detection method," in 2nd International Conference on Electronics and Communication Systems, ICECS 2015, Feb. 2015, pp. 282–285, doi: 10.1109/ECS.2015.7124909.

- [12] S. Zheng, J. Guo, H. Yue, and X. Liu, "Cross domain edge detection based label decoupling salient object detection," in International Conference on Communication Technology Proceedings, ICCT, Oct. 2021, vol. 2021-Octob, pp. 1143–1147, doi: 10.1109/ICCT52962.2021.9657871.

- [13] P. Li, D. J. Lilja, W. Qian, K. Bazargan, and M. D. Riedel, "Computation on stochastic bit streams digital image processing case studies," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 22, no. 3, pp. 449–462, Mar. 2014, doi: 10.1109/TVLSI.2013.2247429.

- [14] Q. Xu, S. Varadarajan, C. Chakrabarti, and L. J. Karam, "A distributed canny edge detector: Algorithm and FPGA implementation," *IEEE Transactions on Image Processing*, vol. 23, no. 7, pp. 2944–2960, Jul. 2014, doi: 10.1109/TIP.2014.2311656.

- [15] J. D. Owens et al., "A survey of general-purpose computation on graphics hardware," Computer Graphics Forum, vol. 26, no. 1, pp. 80–113, Mar. 2007, doi: 10.1111/j.1467-8659.2007.01012.x.

- [16] D. Sangeetha and P. Deepa, "FPGA implementation of cost-effective robust canny edge detection algorithm," *Journal of Real-Time Image Processing*, vol. 16, no. 4, pp. 957–970, Mar. 2019, doi: 10.1007/s11554-016-0582-2.

- [17] I. K. Park, N. Singhal, M. H. Lee, S. Cho, and C. Kim, "Design and performance evaluation of image processing algorithms on GPUs," *IEEE Transactions on Parallel and Distributed Systems*, vol. 23, no. 1, pp. 91–104, Jan. 2011, doi: 10.1109/TPDS.2010.115.

- [18] L. H. A. Lourenço, D. Weingaertner, and E. Todt, "Efficient implementation of canny edge detection filter for ITK using CUDA," in *Proceedings - 13th Symposium on Computing Systems*, WSCAD-SSC 2012, Oct. 2012, pp. 33–40, doi: 10.1109/WSCAD-SSC.2012.21.

- [19] J. G. Pandey, A. Karmakar, C. Shekhar, and S. Gurunarayanan, "A novel architecture for FPGA implementation of Otsu's global automatic image thresholding algorithm," in *Proceedings of the IEEE International Conference on VLSI Design*, Jan. 2014, pp. 300–305, doi: 10.1109/VLSID.2014.58.

- [20] A. F. Torres-Monsalve and J. Velasco-Medina, "Hardware implementation of ISODATA and Otsu thresholding algorithms," Aug. 2016, doi: 10.1109/STSIVA.2016.7743329.

- [21] N. Tariq, R. A. Hamzah, T. F. Ng, S. L. Wang, and H. Ibrahim, "Quality assessment methods to evaluate the performance of edge detection algorithms for digital image: a systematic literature review," *IEEE Access*, vol. 9, pp. 87763–87776, 2021, doi: 10.1109/ACCESS.2021.3089210.

- [22] J. Sun, Z. Wang, and Z. Li, "Implementation of sobel edge detection algorithm and VGA display based on FPGA," in *Proceedings of 2019 IEEE 4th Advanced Information Technology, Electronic and Automation Control Conference, IAEAC 2019*, Dec. 2019, pp. 2305–2310, doi: 10.1109/IAEAC47372.2019.8997533.

- [23] H. T. Ngo and V. K. Asari, "A pipelined architecture for real-time correction of barrel distortion in wide-angle camera images," *IEEE Transactions on Circuits and Systems for Video Technology*, vol. 15, no. 3, pp. 436–444, Mar. 2005, doi: 10.1109/TCSVT.2004.842609.

- [24] H. Kim, B. G. Nam, J. H. Sohn, J. H. Woo, and H. J. Yoo, "A 231-MHz, 2.18-mW 32-bit logarithmic arithmetic unit for fixed-point 3-D graphics system," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 11, pp. 2373–2380, Nov. 2006, doi: 10.1109/JSSC.2006.882887.

- [25] K. H. Abed and R. E. Siferd, "CMOS VLSI implementation of 16-bit logarithm and anti-logarithm converters," in *Midwest Symposium on Circuits and Systems*, 2000, vol. 2, pp. 776–779, doi: 10.1109/mwscas.2000.952871.

## **BIOGRAPHIES OF AUTHORS**

**Duong Huu Ai** <sup>[D]</sup> **S**<sup>[]</sup> **I**<sup>[C]</sup> he received the Master of Electronic Engineering from Danang University of Technology, Vietnam, in 2011, and the Ph.D. degree in Electronics and Telecommunications from Hanoi University of Technology, Vietnam, in 2018. Currently, he is a lecturer at The University of Danang - Vietnam-Korea University of Information and Communication Technology, Danang City, Vietnam. His research interests include optical wireless communications, optical and quantum electronics, 5G wireless communications, broadband networks, and IoT. He can be contacted at email: dhai@vku.udn.vn.

**Cong Dat Vuong C X S C** he received the Master of Telecommunication and Electronic from Sheffield Hallam University, Sheffield, U.K, in 2013. He got his Ph.D. degree from the school of Electronic Engineering, Soongsil University, South Korea, in 2018. His research interests include wireless communication, visible light communication, and antenna communication. He is currently a lecturer at The University of Danang - Vietnam-Korea University of Information and Communication Technology, Danang City, Vietnam. He can be contacted at email: vcdat@vku.udn.vn.

**Khanh Ty Luong b S c** he received his Master of Engineering in Computer Science from the University of Danang, Vietnam in 2012. Currently, he is a lecturer at The University of Danang - Vietnam-Korea University of Information and Communication Technology, Danang City, Vietnam. His research interests include database, artificial intelligence, IoT, and optical wireless communications. He can be contacted email: ktluong@vku.udn.vn.

**Viet Truong Le Solution X Solution C** he received his Master of Science in Informatics from Hue University, Vietnam in 2005. Currently, he is a lecturer at The University of Danang - Vietnam-Korea University of Information and Communication Technology, Danang City, Vietnam. His research interests include database, data warehouse, data mining, system analysis and design. He can be contacted at email: lvtruong@vku.udn.vn.