# Design of matrix, distributive round robin, ping pong and enhanced ping lock arbiter for shared resources systems

#### Nagaiyanallur Lakshminarayanan Venkataraman, Subramanian Sumithra, Ramaiah Purushothaman, Subramani Suresh Kumar, Kathiresan Kokulavani, Velankanni Gowri Department of Electronics and Communication Engineering, J.J. College of Engineering and Technology, Tiruchirapplli, India

# Article Info ABSTRACT Article history: Arbiter is one of the main core elements in the network scheduler. The

Received Jul 6, 2023 Revised Jul 21, 2023 Accepted Oct 11, 2023

#### Keywords:

Distributive round-robin arbiter Enhanced ping lock arbiter Matrix arbiter NoC router and verilog HDL Ping pong arbiter Arbiter is one of the main core elements in the network scheduler. The significant goal of this work is to design a high-speed and low execution-time arbiter with lock free and fair arbitration scheme. In this work, four types of arbiters such as matrix arbiter (MA), ping pong arbiter (PPA), distributive round-robin arbiter (DRRA) and enhanced ping lock arbiter (EPLA) are designed and analyzed area, delay, and speed of arbiters. MA is worked in square matrix format and matrix transition is performed for effective routing. The DRRA is designed by using a multiplexer and counter. Hence an, effective scheduling is carried out in DRRA. Binary tree format is used in PPA. The PPA provides low chip size and high speed than existing MA and DRRA. The PPA limits fair arbitration during uniformly distributed active request patterns. To overcome this problem, PPA is improved with some lock systems to create an EPLA. A new ping lock arbiter (PLA) leaf and PLA inter structure is proposed at the gate level to reduce the execution delay, improve the speed and achieve fair arbitration over all other existing arbiters. Resource allocation, execution delay, and speed are analyzed using the Xilinx integrated software environment (ISE) tool.

This is an open access article under the <u>CC BY-SA</u> license.

#### **Corresponding Author:**

Nagaiyanallur Lakshminarayanan Venkataraman Department of Electronics and Communication Engineering, J.J. College of Engineering and Technology Tiruchirapplli, Tamil Nadu, India Email: venkat.altera@gmail.com

## 1. INTRODUCTION

Currently, a common resource can be accessed by many requestors in several systems. This common resource can be shared memory, specific finite state machines, networking fabric switches, and optimized computational elements. It leads to scaling problems due to integrating many of the integrated circuits into a single core. Arbiter identifies which type of scheduling scheme can be used by requestors to achieve an effective resource allocation policy. A suitable size between the requestors and arbiters must be created by creating an interface between them. The synthesized results will be affected by how the code is written for a specific module. A cyclic scheduling scheme is achieved to avoid repeated routing from the same input channel. The verilog hardware description language (HDL) is used to model these arbiters' designs. Also, logical verification of these arbiters is carried out in Verilog HDL. Once modeling it in Verilog, the Xilinx software calculates the resource utilization, speed, and power utilization.

Problem formulation: initially, the normal bus arbitration scheme is followed in round robin arbiter (RRA). The equal resource allocation scheme is achieved by using a token. Every user has an individual token to make a grant signal at a particular time. One of the users gets grant signals at a specific interval in each clock cycle. An efficient resource utilization scheme will be introduced in recent days. A fast crossbar scheduler

is used for resource allocation policy [1]. In the crossbar switch, multiplexer and de-multiplexer operations are carried out. Initially, the n numbers of the input channel send the request at a time. But only one input channel gets a grant signal first based on the highest priority in the queue. After that, all other input channels are processed cyclically. Also, pipelined implementation is included to improve the speed of a scheduler. But the chip size and power consumption are very high. Previously [2], the programmable priority encoder (PPE) based RRA was used, which requires the highest gate delay. Hence, binary tree structure-based parallel round-robin arbiter (PRRA) is introduced easily and quickly. The die size and power utilization are very high in parallel processing. But the gate delay is low when compared to the crossbar scheduler.

Work contribution: this paper presents a design of four types of RRA, such as MA, distributive distributive round-robin arbiter (DRRA), ping pong arbiter (PPA), and extended ping lock arbiter (PLA) are presented with a fair scheduling policy. A new PLA leaf and PLA inter structure is proposed at the gate level to reduce the execution delay, improve the speed and achieve fair arbitration over all other existing arbiters. Resource allocation, execution delay, and speed are analyzed using the Xilinx ISE tool. Also, these results are compared with all existing other arbitres. The highest priority requestors must be routed first than any other requestor. This paper is structured as follows: in section 2, explains design of matrix, distributive round robin, ping pong and enhanced PLA for shared resources systems. We present the results and discussion in section 3 and conclude this paper in section 4.

In system-on-chip (SoC) implementations, the transaction buses are split by designing a dual RRA [3]. A non-multiplexed rip-transaction bus is constructed using an address bus arbiter and data bus arbiter for SoC implementation. The dual arbiters make certain bounded waiting times for each request. The distributed scheduler-based crossbar switch and proposed distributed arbiter are designed, and the results are analyzed [4]. The fair crossbar switch is designed by using a tiny scheduler and mask circuit. The fair crossbar switch reduces the hardware cost, critical delay, power consumption, and scheduling delay. Also, fairness is predictable. Further, to improve fairness, some other arbiters are introduced nowadays. A programmable priority arbiter is designed using a new bit-level algorithm and parallel prefix adder logic [5]. Hence the delay is reduced and consumes less energy. Also, speed is high in the new programmable priority arbiter with thermo code is designed by using two fixed priority encoders (FPE) and edge detectors (ED) [6]. Four parallel prefix adders are used, such as brent kung, han carison, kogge stone, and ladner fischer structures. Carry generation and carry propagation are carried out in three stages to make a carry look-ahead adder (CLA). AND gate operation is used in carry generation. Also, OR gate operation is included in the carry propagation term. The number of stages is reduced in parallel prefix adder. Hence the speed is very high, and the area is low.

A merged arbiter and multiplexer (MARX) structure and sorting-based arbitration algorithm are designed and included in the proposed merge switch allocation and traversal in network operations center (NoC) switches [7]. This switch is used in easy and very difficult arbitration strategies beneath generic structural design. Also, provide efficient area, delay, and energy utilization. An RRA is designed with an index that functions on the index format of key switches [8]. Logarithmic scaling operation is carried out in a number of input ports when compared to all other existing RRA. Hence the index based round robin arbiter (IRRA) IRRA offers high speed, low chip size, and low power consumption. But fairness is limited. Parallel pseudo-RRA is designed to enable multiple requests simultaneously through concurrent operation [9]. So, speed is high, but chip size and power utilization are high. A generic algorithm-based optimization is applied in weighted RRA. An appropriate weight is allocated for every input port [10]. The input channel which has the highest weight is granted first. So, the delay is minimized. But complexity is increased. Clock gating-based RRA is designed to achieve low power and low delay by reducing the switching activity of the clock signal [11]. The clock signal will be generated when the enable and clock are high. So, the number of clock cycles is reduced; hence power is low. The pipelined structure of radix-2, 4, and 8-based multipath delay commutator fast fourier transform (FFT) is introduced to improve the throughput and speed [12]. A kalman filter is used with a madgwicks filter together to suit the fading issues. It involves a priori evaluation of autoregressive parameters [13]. A programmable logic controller provides the accuracy and validity of this model [14]. Median-based, root mean square-based, and P84-based procedures were implemented and investigated in a full comparison between them to find their advantage and disadvantage and the suitability of each method for a specific application [15]. Fusion of computed tomography lung image and positron emission tomography lung image using their structural similarity [16]. The two levels of the energy storage system are used as the battery at the source side and the transformer at the load side [17]. A complete review of the ongoing advances of finite impulse response (FIR) filter plan procedures in multicarrier modulation based correspondence frameworks. Initially, the essential issues are tried, considering the presentation of available data signal applicants and the FIR filter design concept [18]. A single pole double throw discrete switch design is introduced using switchable substrate integrated waveguide resonators. It is designed for the millimeter to wave multiple input multiple output transceivers [19]. It uses a multi-layered array of cells known as a

superstrate multi-layer metasurface. It is identified in front of a patch of microstrip antenna to absorb surface waves and prevent them from passing during the insulating material that minimizes the permeability of the insulator. Therefore, it enhances the antenna properties [20]. Hybrid time-power splitting relaying approach in a full-duplex decode-and-forward battery-energized relaying network [21].

The matrix arbiter (MA) resource utilization is less compared to RRA [22]. RRA, MA, and indexbased round robin (IRR) arbiter is explained in [23]. Low-latency communication improves inter processing elements communication by utilizing a circuit switching method with negligible adaptive routing and a fair path resolution method to enhance bandwidth utilization [24]. The improved PPA is optimized to provide lesser delay [25]. The pipelined architecture of multi path delay commutator fast fourier transform is applied for dissimilar length system by investing the data stream of Ns at the input. It improving speed and throughput [26]. The espressif systems 8,266 node micro-controller unit is selected because it may be used as a sensor node and has the arbiter-physical unclonable function. The adoption of an artificial neural network with a resilient backpropagation training technique allows for highly accurate modeling of the non-linearity [27]. Dynamic congestion mechanism proposed forwarding rule that can be applied to select high-priority from the cloud service [28]. The role-mapping algorithm strategy reaches more saving in the amount of stored role-mapping rules that reduces the size of rule-store also minimizes the response time [29]–[31].

## 2. PROPOSED METHOD

#### 2.1. Matrix arbiter

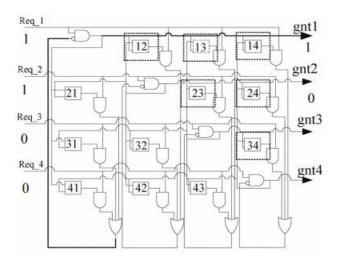

The MA produces the desired matrix for the input and output port, while every input port requests the same output port with the same priority. In that MA, locate the equivalent morsel, which is demanded the same output port. If assume the first states in the upper triangle of the MA are put to one. The diagram of the 4-bit MA is shown in Figure 1.

Figure 1. Matrix arbiter for 4-bit

Similarly, the elements in the lower triangle must be 0 based on the complementary principle. In the unique MA, the request 1(Req\_1) has the highest priority, then request 2(Req\_2), request 3(Req\_3) and request 4(Req\_4) has lowest precedence. MA produces control signals; hence meticulous choose line is selected, and input data is sent to the output port. The priority matrix of the arbiter is given:

$$\begin{bmatrix} X & W_{1,2} & W_{1,3} & W_{1,4} \\ W_{2,1} & X & W_{2,3} & W_{2,4} \\ W_{3,1} & W_{3,2} & X & W4 \\ W_{4,1} & W_{4,2} & W_{4,3} & X \end{bmatrix}$$

In Figure 1, every block numbered 01, 02, 03, 12, 13, and 23 illustrate set-reset (SR) latch. Also, the position is continued in these SR latches in the higher triangular section of the matrix. All of the blocks numbered 10, 20, 30, 21, 31 and 32 in the subordinate triangular section of the matrix represent the complementary output of the transversely symmetric firm box.

#### 2.2. Ping pong arbiter

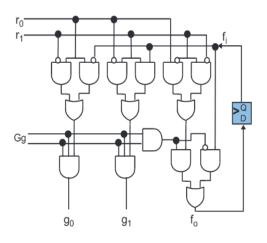

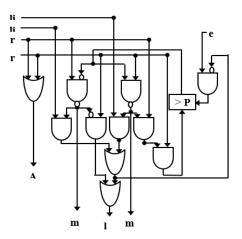

The PPA is designed by connecting small arbiters in binary tree format. The 2-bit PPA consists of a number of AND, OR gates, and D flip-flops, as shown in Figure 2. Also, internal feedback flag signal fi gives the past output as present input through the feedback process.

Initially, the 2-bit PPA gets a grant signal in the subsequent level; after that receives a valid grant signal in 2-bit PPA. The four-bit ping pong arbiter is created by using a three 2-bit PPA with some gates, as shown in Figure 3. So the arbiter gets a grant signal in each layer covered based on the parent arbiter's grant signal. Total arbitration time is very low in PPA.

Figure 2. The 2-bit PPA

Figure 3. The 4-bit PPA

#### 2.3. Distributive round robin arbiter

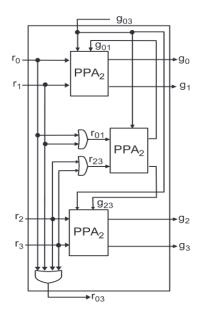

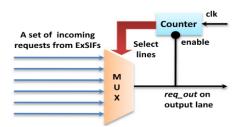

The DRRA consists of multiplexer (MUX) and counter unit, as shown in Figure 4. The selection line of the MUX is taken from the counter output. Also, the MUX output is given as enable signal of the counter. The MUX and counter size depend upon the number of input and output lanes. N number of input channels gives the request at a time. But only one input data is transmitted into the destination port based on the MUX's counter output or selection line. It provides low latency during the channel setup time when evaluated by all other classic arbiters. Only two components are used to construct the DRRA.

Figure 4. Circuit diagram of DRRA

#### 2.4. Enhanced ping lock arbiter

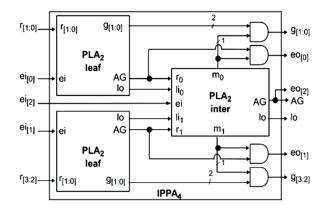

The priority updating policy is altered in PPA and extended PPA to achieve fair arbitration. Restructure the superior level of arbitr in order to get the priority earlier than each input is processed in one round of arbitration. The uppermost index-based request is processed first to set the grant signal in order to achieve fair arbitration by conforming to the priority vector of the intermediate arbitre needs to be modernized. This work introduces novel 4-bit RRA architecture by combing a two-bit arbitr, also called enhanced ping lock arbiter (EPLA), as shown in Figure 5. The new grant updating policy is incorporated in EPLA for fair arbitration. The 2-bit PLA produces three outputs: grant signal (g), AG, eo, and lock output (lo).

This arbiter produces one extra output (i.e.) lo. Lo with AG signal is given to the parent arbiter. The grant signal is given to the parent arbiter when the AG signal is declared for lo. The priority register value is not changed in the next clock cycle. The lo signal of the 2-bit arbiter is declared to set the grant signal for any input request of the arbiter. The four-bit EPLA is constructed using two PLA2 leaf, shown in Figure 6.

Figure 5. Circuit diagram of 4-bit extended PLA

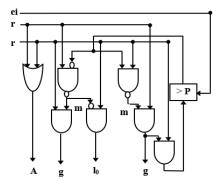

Figure 6. Circuit diagram of PLA2 inter

But the request of the next level arbiter is not granted. Because the feedback path is used in P register to control the output of EPLA. One PLA2inter is demonstrated in Figure 7 structure with four and gates. The proposed EPLA arbiter provides high speed, fair arbitration, low power, and compact chip size.

Figure 7. Circuit diagram of PLA2 leaf

## 3. RESULTS AND DISCUSSION

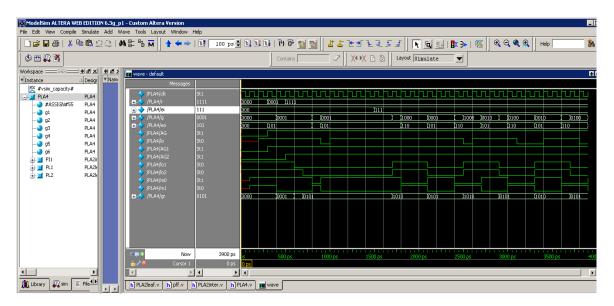

In this work, four types of arbiters, such as MA, DRRA, PPA, and EPLA, are constructed using Verilog HDL to check the functionality of all arbiters. Also, synthesized results are taken to analyze the area and delay product (ADP). The simulation output of EPLA is shown in Figure 8.

Figure 8. Simulation output of 4-bit extended PLA

From the output, clock, request (r), and input enable (ei) are inputs, and g, enable output (eo), AG, and lo are outputs. The clock signal is generated. When the entire request (r=0000) is zero, the corresponding grant is zero, and during ei is zero. After that, r=0001, and after one clock cycle, the corresponding g=0001. Finally, when the entire request is one (r=1111), and ei is one, the corresponding g is generated one by one sequentially (i.e.,) g=1000 for the first clock cycle, g=0001 for the third clock cycle, g=0010 for the fifth clock cycle and g=0100 at seventh clock cycle. Hence there is fair arbitration is achieved in EPLA. The synthesized results are evaluated to estimate the area, delay, and frequency of four types of arbiters and performance analysis is carried out based on the obtained result, as shown in Table 1. The analysis shows that the DRRA provides a smaller chip size than all other arbiters like PPA, MA and EPLA. But the speed is lower than PPA and EPLA. Furthermore, the DRRA arbiter has a lower delay compared to the EPLA and PPA arbiters. But the MA has a lower delay compared to all other arbiters.

| Table 1. Comparison of four types of arbiters |                          |                                                                                            |                                                                                                                                                                                  |

|-----------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                    |                          |                                                                                            |                                                                                                                                                                                  |

| Slices                                        | LUT                      | Delay                                                                                      | Frequency                                                                                                                                                                        |

| 11                                            | 21                       | 3,897 ns                                                                                   | 790,952 MHz                                                                                                                                                                      |

| 23                                            | 27                       | 4,120 ns                                                                                   | 910,345 MHz                                                                                                                                                                      |

| 28                                            | 49                       | 3,793 ns                                                                                   | -                                                                                                                                                                                |

| 19                                            | 24                       | 4,481 ns                                                                                   | 855,918 MHz                                                                                                                                                                      |

|                                               | Slices<br>11<br>23<br>28 | Slices         LUT           11         21           23         27           28         49 | Parameters           Slices         LUT         Delay           11         21         3,897 ns           23         27         4,120 ns           28         49         3,793 ns |

The PPA offers high speed than all other states of art arbiters. Anyhow area is higher than DRRA and EPLA. Also, fair arbitration is limited. Matrix arbiter provides low delay, but the chip size is large. Finally, the EPLA requires a lower area than the matrix arbiter and PPA. But the chip size is more significant than DRRA. Fair arbitration (non-starvation) is fully achieved in EPLA. Also, performance is very high when compared to DRRA and MA.

#### 4. CONCLUSION

In this paper, the high-speed compact arbiter is designed to attain fair arbitration. Several types of arbiters are studied for the common resource-sharing process. Four different kinds of arbiters MA, DRRA, PPA, and EPLA, are constructed to estimate the chip size, execution delay and speed of the arbiter. The arbitres are designed using Verilog HDL based on register transfer level implementation. The functionality of all kinds of arbiters is verified through ModelSim software. The Xilinx synthesized results calculate the area, delay, and speed. The DRRA is best for compact chip-size applications. PPA is used for high speed with fairness arbitration. MA is suited for low execution delay-based arbiter design. The EPLA is used for fair arbitration, small chip size, and high-speed applications. The ping lock RRA is incooperated with wireless network will be design in future.

#### REFERENCES

- P. Gupta and N. McKeown, "Designing and implementing a fast crossbar scheduler," *IEEE Micro*, vol. 19, no. 1, pp. 20–28, 1999, doi: 10.1109/40.748793.

- [2] S. Q. Zheng, M. Yang, J. Blanton, P. Golla, and D. Verchere, "A simple and fast parallel round-robin arbiter for high-speed switch control and scheduling," in *The 2002 45th Midwest Symposium on Circuits and Systems, 2002. MWSCAS-2002.*, 2002, vol. 2, pp. II-671-II–674, doi: 10.1109/MWSCAS.2002.1186951.

- [3] J. Reed and N. Manjikian, "A dual round-robin arbiter for split-transaction buses in system-on-chip implementations," in *Canadian Conference on Electrical and Computer Engineering 2004 (IEEE Cat. No.04CH37513)*, 2004, vol. 2, pp. 835–840, doi: 10.1109/CCECE.2004.1345244.

- [4] S. W. Yang, M. H. Sheu, C. K. Yeh, C. Y. Wen, C. C. Lin, and W. K. Tsai, "Fast fair crossbar scheduler for on-chip router," in 2007 IEEE International Symposium on Circuits and Systems, May 2007, pp. 385–388, doi: 10.1109/ISCAS.2007.378470.

- [5] G. Dimitrakopoulos, N. Chrysos, and K. Galanopoulos, "Fast arbiters for on-chip network switches," in 2008 IEEE International Conference on Computer Design, Oct. 2008, pp. 664–670, doi: 10.1109/ICCD.2008.4751932.

- [6] H. F. Ugurdag and O. Baskirt, "Fast parallel prefix logic circuits for n2n round-robin arbitration," *Microelectronics Journal*, vol. 43, no. 8, pp. 573–581, Aug. 2012, doi: 10.1016/j.mejo.2012.04.005.

- [7] G. Dimitrakopoulos, E. Kalligeros, and K. Galanopoulos, "Merged switch allocation and traversal in network-on-chip switches," *IEEE Transactions on Computers*, vol. 62, no. 10, pp. 2001–2012, Oct. 2013, doi: 10.1109/TC.2012.116.

- [8] M. Oveis-Gharan and G. N. Khan, "Index-based round-robin arbiter for NoC routers," in 2015 IEEE Computer Society Annual Symposium on VLSI, Jul. 2015, vol. 07-10-July, pp. 62–67, doi: 10.1109/ISVLSI.2015.27.

- [9] R. Bashizade and H. Sarbazi-Azad, "P2R2: parallel pseudo-round-robin arbiter for high performance NoCs," *Integration*, vol. 50, pp. 173–182, Jun. 2015, doi: 10.1016/j.vlsi.2014.11.002.

- [10] F. Jafari, A. Jantsch, and Z. Lu, "Weighted round robin configuration for worst-case delay optimization in network-on-chip," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 12, pp. 3387–3400, Dec. 2016, doi: 10.1109/TVLSI.2016.2556007.

- [11] B. Debbarma and J. Debbarma, "Clock gated round robin arbiter for noc router," MATTER: International Journal of Science and Technology, vol. 3, no. 3, pp. 113–124, Nov. 2017, doi: 10.20319/mijst.2017.33.113124.

- [12] M. M. Ismail, M. Subbiah, and S. Chelliah, "Design of pipelined radix-2, 4 and 8 based multipath delay commutator (MDC) FFT," *Indian Journal of Public Health Research and Development*, vol. 9, no. 3, pp. 765–768, 2018, doi: 10.5958/0976-5506.2018.00380.7.

- [13] N. A. Kadhim, A. J. Alrubaie, and A. Al-Khaykan, "Two cross coupled and Madgwicks filter for estimation of multi-channel dividing systems," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 27, no. 1, p. 262, Jul. 2022, doi: 10.11591/ijeecs.v27.i1.pp262-270.

- [14] I. H. A. Al-Had, F. M. Mohammed, and J. A. K. Mohammed, "Modeling and simulation of electro-hydraulic telescopic elevator system controlled by programmable logic controller," *Indonesian Journal of Electrical Engineering and Computer Science* (*IJEECS*), vol. 27, no. 1, p. 71, Jul. 2022, doi: 10.11591/ijeecs.v27.i1.pp71-78.

- [15] S. A. Bamerni and A. K. Al-Sulaifanie, "Field programmable gate arrays implementation of different standard deviation estimation techniques," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 27, no. 1, p. 118, Jul. 2022, doi: 10.11591/ijeecs.v27.i1.pp118-130.

- [16] R. M. Priya, and P. Venkatesan, "Image fusion based lung nodule detection using structural similarity and max rule," *International Journal of Advances in Signal and Image Sciences*, vol. 5, no. 1, p. 29, Jun. 2019, doi: 10.29284/IJASIS.5.1.2019.29-35.

- [17] M. A. Prasanna, P.S. Rajan and G. Praveenraj, "Energy storage in battery for remote area using wind DFIG generation," *International Journal of Advances in Signal and Image Sciences*, vol. 5, no. 1, p. 22, 2019, doi: 10.29284/ijasis.5.1.2019.22-28.

- [18] O. N. Kadhim, K. T. Khudhair, F. H. Najjar, and H. M. Al-Jawahry, "Digital filters windowing for data transmission enhancement in communication channel," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 24, no. 3, p. 1454, Dec. 2021, doi: 10.11591/ijeecs.v24.i3.pp1454-1468.

- [19] A. A. Zolkefli et al., "SPDT discrete switch design using switchable SIW resonators for millimeter wave MIMO transceiver," Indonesian Journal of Electrical Engineering and Computer Science (IJEECS), vol. 24, no. 3, p. 1542, Dec. 2021, doi: 10.11591/ijeecs.v24.i3.pp1542-1549.

- [20] A. K. Jassim, M. J. Farhan, and F. N. H. Al-Nuaimy, "Enhancement of gain using a multilayer superstrate metasurface cell array with a microstrip patch antenna," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 24, no. 3, p. 1564, Dec. 2021, doi: 10.11591/ijeecs.v24.i3.pp1564-1570.

- [21] H. P. Van and H. S. Nguyen, "Throughput performance for full-duplex DF relaying protocol in hybrid wireless power transfer systems," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 24, no. 3, p. 1571, Dec. 2021, doi: 10.11591/ijeecs.v24.i3.pp1571-1577.

- [22] T. Kavitha, S. Shiyamala, and P. Nagarajan, "FPGA implementation of arbiters algorithm for network-on-chip," ARPN Journal of Engineering and Applied Sciences, vol. 11, no. 19, pp. 11451–11456, 2016.

- [23] S. Mahalakshmi, "A survey on arbitration techniques for SoC design," Cammillus International Journal of Engineering Technology Science and Research, vol. 4, no. 8, 2017.

- [24] R. Kumar and A. Gordon-Ross, "MACS: a highly customizable low-latency communication architecture," *IEEE Transactions on Parallel and Distributed Systems*, vol. 27, no. 1, pp. 237–249, Jan. 2016, doi: 10.1109/TPDS.2015.2390631.

- [25] A. Monemi, C. Y. Ooi, M. Palesi, and M. N. Marsono, "Ping-lock round robin arbiter," *Microelectronics Journal*, vol. 63, pp. 81–93, May 2017, doi: 10.1016/j.mejo.2017.03.004.

- [26] A. Balaji, V. P. Srinivasan, J. Rangarajan, V. Nagaraju, B. Bharathi, and S. Murugan, "Smart technique to prevent flood disaster due to high rainfall in coastal areas using IoT," in 2023 International Conference on Intelligent and Innovative Technologies in Computing, Electrical and Electronics (IITCEE), Jan. 2023, pp. 1252–1256, doi: 10.1109/IITCEE57236.2023.10090999.

- [27] M. S. Mispan, A. Z. Jidin, H. M. Nasir, N. M. A. Brahin, and I. M. Nawi, "Modeling arbiter-PUF in NodeMCU ESP8266 using artificial neural network," *International Journal of Reconfigurable and Embedded Systems (IJRES)*, vol. 11, no. 3, p. 233, Nov. 2022, doi: 10.11591/ijres.v11.i3.pp233-239.

- [28] T. Alwada'n, A.-K. Al-Tamimi, A. H. Mohammad, M. Salem, and Y. Muhammad, "Dynamic congestion management system for cloud service broker," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 13, no. 1, p. 872, Feb. 2023, doi: 10.11591/ijece.v13i1.pp872-883.

- [29] D. Abdelfattah, H. A. Hassan, and F. A. Omara, "Enhancing highly-collaborative access control system using a new role-mapping algorithm," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 12, no. 3, p. 2765, Jun. 2022, doi: 10.11591/ijece.v12i3.pp2765-2782.

- [30] S. Ahmad and A. Shahada, "Multilayer neural network based fall alert system using IoT," International Journal of MC Square Scientific Research, vol. 10, no. 4, 2019.

- [31] P. Arul, M. Meenakumari, L. Saravanan, N. Revathi, S. Jayaprakash, and S. Murugan, "Intelligent power control models for the IoT wearable devices in BAN networks," in *Proceedings of the International Conference on Intelligent and Innovative Technologies in Computing, Electrical and Electronics, ICIITCEE 2023*, Jan. 2023, pp. 820–824, doi: 10.1109/IITCEE57236.2023.10090918.

#### **BIOGRAPHIES OF AUTHORS**

**Dr. Nagaiyanallur Lakshminarayanan Venkataraman D S S C** received his B.E. in Electronics and Communication Engineering from Saranathan College of Engineering, Tiruchirappalli in 2007, M.E. in VLSI Design from Oxford Engineering College, Tiruchirappalli in 2012 and Ph.D. from National Institute of Technology, Nagaland in 2020. He is presently working as Associate Professor in J.J. College of Engineering and Technology, Tiruchirappalli. He has more than 13 years of experience both in teaching and research field. His field of research includes FPGA based design, optimization of VLSI circuits and digital circuit design. He has published more than 10 research papers in SCI/SCIE, SCOPUS indexed journals. Also, he has authored 01 book. He has published 01 patent. He can be contacted at email: venkat.altera@gmail.com.

**Dr. Subramanian Sumithra b S s c** received her B.E. in Electronics and Communication Engineering from Madurai Kamaraj University in 1998, M.E. from Vinayaka Mission University. She completed Ph.D. degree from Anna University in 2015. At present; she is working as a Professor and HOD in J.J College of Engineering and Technology, Trichy. She has having more than 24 years of experience both in teaching and research field. Her fields of research include wireless sensor networks, signal processing, wireless communication, and digital image processing. She has 30 papers in national/international conference and 20 papers in international journals. She can be contacted at email: drsumithra30@gmail.com.

Ramaiah Purushothaman 💿 😵 👓 received his B.E. at J.J. College of Engineering and Technology, M.E. at Pavendhar Bharathidasan College of Engineering and Technology, Tiruchirappalli and currently pursuing Ph.D. at Sathyabama University, Chennai. He is presently working as Assistant Professor in J.J. College of Engineering and Technology, Tiruchirappalli. He has more than 15 years of teaching experience. His field of research He includes wireless sensor networks. can be contacted at email: purushoth8419@gmail.com.

Subramani Sureshkumar (D) 🛐 🖾 🗭 received his B.E. in Electronics and Communication Engineering from Christian College of Engineering and Technology, Oddanchatram (Anna University-Chennai) in 2008, M.E. in Applied Electronics from Bannari Amman Institute of Technology, Sathyamangalam (Anna University-Coimbatore) in 2010. He is presently working as Assistant Professor in J.J. College of Engineering and Technology, Tiruchirappalli. He has 12 years of teaching experience. His field of research includes VLSI technology, adhoc networks, photovoltaic cells and digital system design. He can be contacted at email: sureshkumars@jjcet.ac.in.

Kathiresan Kokulavani (D) 🕄 SC C received her B.E in Electronics and Communication Engineering from Mohamed Sathak Engineering College in 2004, M.E in VLSI Design from Sri Eashwar Engineering College, Coimbatore in 2014. She is currently registered her Ph.D in Anna University, Chennai. She is presently working as Assistant Professor in J.J.College of Engineering and Technology, Tiruchirappalli. The author has more than 5 years of teaching experience. Her field of research includes Digital Image Processing and Low Power. VLSI. She can be contacted at email: kokulavani1982@gmail.com.

**Velankanni Gowri**  Kelexie Content in the second s