# D flip-flop design by adiabatic technique for low power applications

## Minakshi Sanadhya, Devendra Kumar Sharma

Department of Electronics and Communication Engineering, Faculty of Engineering and Technology, SRM Institute of Science and Technology, Ghaziabad, India

#### ABSTRACT **Article Info** Article history: Indigital circuits, energy reduction is the most important parameter in the design of handy and battery-operated devices. Flip- flop is an important Received Apr 11, 2022 component in any digital system. By improving the performance of flip-flop, Revised Sep 16, 2022 complete system performance is better. This paper addresses the design of D Accepted Sep 30, 2022 flip-flop using direct current diode-based positive feedback adiabatic logic (DC-DB PFAL) at various frequencies at 45nm technology node. Further, the layout for the proposed design is also presented. The performance analysis is Keywords: carried out for delay, power dissipation, power delay product and transistor count. Circuit simulation is done by using cadence virtuoso tool at 10 MHz Adiabatic circuits and 100 MHz frequencies. The results show an improvement in power Delav dissipation of 18% with less transistors count compared to exiting designs in Flip-flop the literature. Low power This is an open access article under the <u>CC BY-SA</u> license. Power dissipation (ງ **Corresponding Author:** Minakshi Sanadhya

Department of Electronics and Communication Engineering, Faculty of Engineering and Technology SRM Institute of Science and Technology Ghaziabad, UttarPradesh, India Email: minakshisandhya@gmail.com

## 1. INTRODUCTION

As battery-powered devices become smaller, the size of the devices also shrinks. Low-power very large scale integration design has been progressively increasing due to speedy and inventive development [1]. Because of the rapid advancement of personal devices, high-performance digital signal processors and the internet of things, low power, fault tolerance, and high-performance devices are in greater demand [2], [3]. Alam *et al.* [4] have presented the low-power, small, and modular complementary metal -oxide semiconductor amplifier for modern radio frequency receivers, showing the improvement in power dissipation and gain range. Sulaiman [5] have presented multi-objective Pareto front and particle swarm optimization techniques to minimize energy consumption and delay in microprocessors.

The adiabatic technique is one of the innovative approaches for minimum power dissipation at the circuit logic level if the time constraint is not critical. The most optimum approach is adiabatic-logic, which stores energy in the capacitor rather than discharging it to the ground. Adiabatic is a thermodynamic term that describes a procedure in which energy is not shared with the environment, hence, there is no energy dissipation [6]. Chaudhary *et al.* [7] presented a low-power memory cell using the adiabatic technique. Sharma and Noor [8] designed a semi-adiabatic positive feedback adiabatic logic (PFAL) based dual-rail D flip-flop. A positive-edge flip-flop is implemented in a master-slave configuration. The primary inverter/buffer setup is utilized to regulate the operation of the D flip-flop after adding additional transistors. Sharma and Noor [9] implemented asynchronous reset capability in a complementary pass transistor logic based adiabatic gated (CPLAG) XOR gate. It may be made synchronous with the count of an extra transistor and the reference clock

signal. Ghatole and Gaikwad [10] designed a low-power flip-flop with an innovative resettable method based on signal feed-through adiabatic buffers. It has a variety of pulse-triggered flip-flop devices. The problem of a long discharge path is solved, and improved power and speed are obtained. Hu et al. [11] designed and implemented complementary pass-transistor logic in low-power adiabatic sequential circuits. Sharma and Noor [9] developed a different type of flip flop using the conventional technique and the efficient charge recovery logic adiabatic logic technique. Bhutada [12] designed a low-voltage flip-flop circuit and the powergating using the complementary pass-transistor adiabatic logic (CPAL) approach. Kiran and Raju [13] have presented the realization of energy-efficient combinational and sequential circuits using different adiabatic techniques. Dhoble and Kale [14] presented the design of a positive edge triggered D flip-flop and it is increase the counter's speed in a phase-locked loop using VLSI technology. It consumes low power and provides high speed. Lin et al. [15] presented a low-voltage adiabatic flip-flop which is designed using the CPAL powergating with DTCMOS (dual threshold complementary metal-oxide-semiconductor) approach. Sharma and Noor [16] designed modified PFAL adiabatic logic circuits with a reconfigurable CPLAG approach. Xin et al. [17] designed a 2-phase adiabatic CPAL flip-flop circuit and optimized the power dissipation promptly. Sundar [18] have presented an adiabatic logic method to demonstrate an ultra-low-power sequential logic circuit. Garg and Niranjan [19] presented the logic circuits designs like inverter, NAND, NOR, half adder, and positive edge triggered Dflip-flop using a new cascade adiabatic logic technique. Bharathi et al. [20] presented energy- efficient D flip-flop, half adder, and full adder circuit designs and implemented them using sub-threshold adiabatic logic with two-phase clocking.

Now days, many researches has been reported on the design of adders [20]-[24], subtractors [25], comparators [26]-[28], memory [29] and some other combinational and sequential circuits. The schematic and layout design of the presented circuit is unreported in the literature as of yet. This paper presents a design of a D flip-flop based on the DC-DB PFAL adiabatic approach. The proposed design layout is also drawn and discussed for the process feasibility.

The remaining part of this paper is structured as follows. The preliminaries are discussed in section 2. The design and implementation along with layout of D flip-flop are depicted in section 3. The results and discussion are included in section 4. Finally, this paper is concluded in section 5.

## 2. PRELIMINARIES

An adiabatic circuit is a part of low-power technology that employs reversible logic to save energy [30]. The term adiabatic is refers to thermodynamic process in which no energy is exchanged with the environment and hence no energy is lost in the form of energy consumption [31]. For energy usage in the adiabatic circuit, there are three rules [32], [33]:

i) If the drain and source terminals have a considerable voltage difference, the transistor must be turned off.

- ii) While current flows over the transistor, it must be switch on.

- iii) Never let current flow over a diode.

In place of a steady power source, an adiabatic logic uses the trapezoidal power clock. A 4-stage power supply clock is used in adiabatic logic, that contains ideal, evaluate, hold, and recover phases. In evaluation phase, supply voltage is increased from 0 V to Vdd, i.e. Supply voltage is going up. In hold phase, supply voltage is constant to Vdd and retaining the values for outputs. In recovery phase, energy is recovered, the supply voltage is decreasing from Vdd to 0 V and the power supply recovers the accumulated charge from the capacitors. In wait phase, supply voltage is 0 V.

## 3. DESIGN AND IMPLEMENTATION

In this section, the DC-DB PFAL adiabatic technique is used to design the proposed D flip-flop using cadence virtuoso tool at 45 nm node and at different frequencies of 10 MHz and 100 MHz. DC- DB PFAL adiabatic approach is the modified in modified positive feedback adiabatic logic (MPFAL) logic circuit. The proposed design provides nearly complete charge recovery, which has been previously impossible. Proposed design is implemented and analyzed in terms of latency, power dissipation and power delay product and results are compared with the existing adiabatic techniques and conventional technique.

### 3.1. DC-DB PFAL based D flip-flop

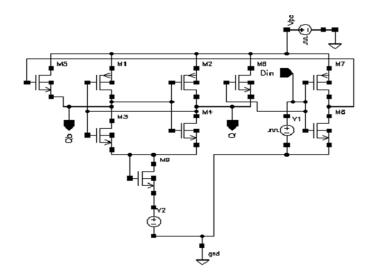

DC-DB PFAL D flip-flop circuit is depicted in Figure 1. MPFAL logic has been modified in this circuit. The proposed design provides nearly complete charge recovery, which has been previously impossible. High impedance path to the power clock is provided by the diode attached at the bottom of N-type metal-oxide-semiconductor (NMOS) tree and it acts as an active load. By reducing the rate of discharge of internal nodes of the logic circuit and it can controls the discharging path. The positive source of direct current voltage is

connected between the diode and the ground to further incorporate the advantage of level shifting technique in the proposed logic circuit. Level shifting technique reduces the gate to source voltage at the output transistors and thus reduces the leakage and gate current, in turn reduces the energy consumption. It is more effective than the other adiabatic logic techniques used earlier for reduction in power dissipation. Simulations are carried out at 10 MHz and 100 MHz frequencies, at 45 nm technology node and the results are obtained for power dissipations and delay. A comparative analysis for performance parameters is shown in Table 1.

Figure 1. D flip-flop based on DC-DB PFAL

## 3.2. Layout design of proposed D flip-flop

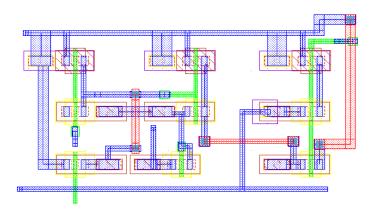

Apart from schematic design, layout design is the most critical step in very large scale integration (VLSI) design flow. Here, the layout design of proposed D flip has been presented. The layout shown here is simulated on the virtuoso tool at 45 nm technology node with design rule check (DRC) and layout versus schematic (LVS) check. It is noteworthy to mention here that this is the first attempt to present the schematic and layout design of D flip-flop utilizing DC-DB PFAL adiabatic technique and thus, can give significant contribution in the low power VLSI domain. Figure 2 depicts the present circuit layout design.

Figure 2. Proposed D flip-flop layout design

## 4. **RESULTS AND DISCUSSION**

This article presents the design of D flip- flop using DC-DB PFAL adiabatic approach. The diode at the bottom of the PFAL latch allows for easy control of the discharge path by lowering the discharge rate of the circuit's internal nodes, as well as level shifting. The leakage current of the output transistor and the gate to source voltage are reduced, because of the level shifting. The proposed circuit minimizes the power consumption.

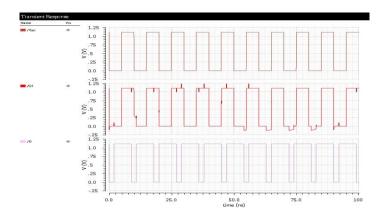

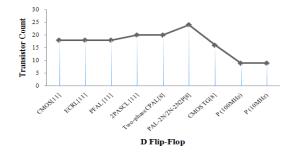

For analysis, the cadence virtuoso tool is used to simulate the present circuit at 45 nm technology node. The D flip-flop circuit parameters like delay, energy consumption, transistor count, and power delay product are investigated. The power dissipation in D flip-flop is one of the most important metrics. When compared to the other existing adiabatic approaches and conventional technique, the energy consumption in proposed design using DC-DB PFAL is the smallest at 10MHz. A Comparative analysis of present circuit design with the existing designs at various frequencies is carried out in Table 1. In this table, at some places the '-' is marked, where the data is not available in the literature. The simulation waveform is depicted in Figure 3. Finally, in Figure 4, the graphs have been plotted, showing the comparison of transistors count for the existing designs with the present design.

The proposed circuit is simulated using 1 V trapezoidal power supply. In Figure 3, the output waveform of the present circuit is represented. In which the output (Q) waveform is obtained corresponding to input (D) and power clock (Vpc) combinations. It is found from the simulation waveform that the output swing is equal to the input swing. In other words, the, output logic level in proposed D flip-flop is nearly the same as that of input logic levels i.e, 0V for logic '0' and 1 V for logic '1'.

The power dissipation of the present circuit design is compared with the existing designs at different frequencies. It is found that the proposed circuit shows improvement in power dissipation by 33% and 18% respectively as compared to RCPLAG based D flip-flop circuit [16] and Sub-threshold adiabatic logic based D flip-flop [20]. In CMOS circuits chip density is the another parameter and it is calculated by the number of transistors. The transistor count of the presented design compared to the other existing techniques is illustrated in Figure 4, wherein 'P' instance for proposed design. It is observed that the present circuit uses fewer transistors compared to the standard adiabatic approaches. Moreover, latency is one of the important performance parameter when it comes to speed. In comparison to the certain designs, it shows improved performance in terms of latency as shown in Table 1.

| SI.No. | D flip-flop references                   | Delay | Power dissipation | Transistor | Frequency |

|--------|------------------------------------------|-------|-------------------|------------|-----------|

|        |                                          | (ps)  | (mW)              | count      | (MHz)     |

| 1      | CMOS [13]                                | 72    | 0.798             | 18         | -         |

| 2      | CMOS [20]                                | -     | 0.0582            | -          | -         |

| 3      | ECRL [13]                                | 15    | 15.08             | 18         | -         |

| 4      | ECRL [16]                                | -     | 0.0591            | -          | -         |

| 5      | PFAL [13]                                | 15    | 4.83              | 18         | -         |

| 6      | PFAL [16]                                | -     | 0.0747            | -          | -         |

| 7      | 2PASCL [13]                              | 17    | 17.98             | 20         | -         |

| 8      | Master-slave [7]                         | -     | 13.4              | -          | -         |

| 9      | Sub-threshold adiabatic logic [20]       | -     | 0.032             | -          | -         |

| 10     | Reconfigurable complementary pass        | -     | 0.039             | -          | -         |

|        | transistor adiabatic logic gated [16]    |       |                   |            |           |

| 11     | CMOS [19]                                | -     | 0.141             | -          | -         |

| 12     | Adiabatic logic [19]                     | -     | 0.084             | -          | -         |

| 13     | Two-phase CPAL [11]                      | -     | -                 | 20         | 100       |

| 14     | Proposed adiabatic logic-2N/2N-2N2P [11] | -     | -                 | 24         | 100       |

| 15     | CMOS TG [11]                             | -     | -                 | 16         | 100       |

| 16     | Proposed design (100 MHz)                | 50.01 | 0.419             | 9          | 100       |

| 17     | Proposed design (10 MHz)                 | 30.0  | 0.026             | 9          | 10        |

Table 1. Comparative analysis of the existing designs with proposed D flip-flop

Figure 3. Output waveforms of the proposed circuit

Figure 4. Transistor count of proposed design with existing designs

#### 5. CONCLUSION

This paper presents the design of D flip-flop using DC-DB PFAL adiabatic technique. Proposed circuit is implemented on virtuoso tool at 45 nm technology node. Comprehensive analysis is carried out for the performance parameters like transistor count, power delay product, delay and energy consumption. The results are compared to the earlier existing designs with the present design. It is observed that the presented circuit design outperforms over the existing designs. Moreover, the layout design for the proposed DC-DB PFAL technique is also presented with DRC and LVS check to prove compatibility in the chip design. The proposed circuit consumes 26  $\mu$ W power, which results in power reduction by 18% and transistors count by 43% compared to the available designs. The present circuit shows superior performance in terms of area and power dissipation at the cost of delay. The comprehensive investigation shows that the presented design can contribute significantly towards low power VLSI applications

#### REFERENCES

- [1] T. Suguna and M. J. Rani, "Analysis of adiabatic hybrid full adder and 32-bit adders for portable mobile applications," *International Journal of Interactive Mobile Technologies*, vol. 14, no. 5, pp. 73-94, 2020, doi: 10.3991/IJIM.V14I05.13343.

- [2] Y. N. S. Kumar and P. Dinesha, "TFI-FTS: an efficient transient fault injection and fault-tolerant system for asynchronous circuits on FPGA platform," *International Journal of Electrical and Computer Engineering*, vol. 11, no. 3, pp. 2704-2710, 2021, doi: 10.11591/ijece.v11i3.pp2704-2710.

- [3] Z. Yuejun, D. Dailu, P. Zhao, W. Pengjun, and Y. Qiaoyan, "An ultra-low power multiplier using multi-valued adiabatic logic in 65 nm CMOS process," *Microelectronics Journal*, vol. 78, no. 818, pp. 26–34, 2018, doi: 10.1016/j.mejo.2018.05.016.

- [4] M. J. Alam, M. A. S. Bhuiyan, M. T. I. Badal, M. B. I. Reaz, and N. Kamal, "Design of a low-power compact CMOS variable gain amplifier for modern RF receivers," *Bulletin of Electrical Engineering and Informatics*, vol. 9, no. 1, pp. 87-93, 2020, doi: 10.11591/eei.v9i1.1468.

- [5] D. R. Sulaiman, "Multi-objective pareto front and particle swarm optimization algorithms for power dissipation reduction in microprocessors," *International Journal of Electrical and Computer Engineering*, vol. 10, no. 6, pp. 6549-6557, 2020, doi: 10.11591/ijece.v10i6.pp6549-6557.

- [6] P. Sasipriya and V. S. K. Bhaaskaran, "Design of low power VLSI circuits using two phase adiabatic dynamic logic (2PADL)," Journal of Circuits, Systems, and Computers, vol. 27, no. 04, p. 1850052, 2018, doi: 10.1142/s0218126618500524.

- [7] P. Chaudhary, B. K. Das, and S. Ahuja, "Design of low power memory cell using D flip flop under adiabatic reduction," 2016 3rd International Conference on Signal Processing and Integrated Networks (SPIN), 2016, pp. 20-23, doi: 10.1109/SPIN.2016.7566655.

- [8] M. Sharma and A. Noor, "Positive feed back adiabatic logic: PFAL single edge triggered semi-adiabatic D flip flop," *African Journal of Basic & Applied Science*, vol. 5, no. 1, pp. 42-46, 2013, doi: 10.5829/idosi.ajbas.2013.5.1.1118.

- [9] M. Sharma and A. Noor, "CPL-adiabatic gated logic (CPLAG) XOR gate," 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), 2013, pp. 575-579, doi: 10.1109/ICACCI.2013.6637236.

- [10] M. D. Ghatole and M. A. Gaikwad, "Design a low power flip-flop based on a signal feed-through scheme," *Internatinal Research Journal of Engineering and Technology*, vol. 03, no. 1, pp. 868–873, 2016.

- [11] J. Hu, T. Xu, and Y. Xia, "Low-power adiabatic sequential circuits with complementary pass-transistor logic," 48th Midwest Symposium on Circuits and Systems, 2005, pp. 1398-1401, vol. 2, doi: 10.1109/MWSCAS.2005.1594372.

- [12] D. S. Bhutada, "Design of low voltage flip-flop based on complementary pass-transistor adiabatic logic circuit," 2016 World Conference on Futuristic Trends in Research and Innovation for Social Welfare (Startup Conclave), 2016, pp. 1-5, doi: 10.1109/STARTUP.2016.7583922.

- [13] S. S. Kiran and D. P. Raju, "Realization of energy efficient logic circuits using adiabatic technique," *International Journal of Computer Science information and Engineering Technologies*, vol. E3, no.4, pp. 1-13, 2015.

- [14] P. G. Dhoble and A. D. Kale, "A review paper on design of positive edge triggered D flip-flop using VLSI technology," *International Journal of Engineering Research & Technology*, vol. 3, no. 2, pp. 1512-1515, 2014.

- [15] J. Lin, J. Hu, and Q. Chen, "Low voltage adiabatic flip-flops based on power-gating CPAL circuits," *Procedia Engineering*, vol. 15, pp. 3144-3148, 2011, doi: 10.1016/j.proeng.2011.08.590.

- [16] M. Sharma and A. Noor, "Reconfigurable CPLAG and modified PFAL adiabatic logic circuits," Advances in Electronics, vol. 2015, p. 202131, 2015, doi: 10.1155/2015/202131.

- [17] Z. Xin, J. Hu, and Q. Chen, "Adiabatic two-phase CPAL flip-flops operating on near-threshold and super-threshold regions," *Procedia Environmental Sciences*, vol. 11, pp. 339-345, 2011, doi: 10.1016/j.proenv.2011.12.054.

- [18] M. S. Sundar, "Ultra low power design of combinational logic circuits," *International Journal of Science and Research*, vol. 5, no. 9, pp. 1554-1558, 2016.

- [19] S. Garg and V. Niranjan, "A new cascadable adiabatic logic technique," *Electrical and Electronics Engineering: An International Journal*, vol. 5, no. 1, pp. 21-36, 2016, doi: 10.14810/elelij.2016.5102.

- [20] M. Bharathi, N. Padmaja, and D. Leela Rani, "Energy efficient digital circuits using two phase clocking sub-threshold adiabatic logic," *International Journal of Recent Technology and Engineering*, vol. 8, no. 2, pp. 101-106, 2019, doi: 10.35940/ijrte.B1692.078219.

- [21] D. Kumar and M. Kumar, "Implementation of parallel computing and adiabatic logic in full adder design for ultra low power applications," *SN Applied Science*, vol. 2, p. 1388, 2020, doi: 10.1007/s42452-020-3188-z.

- [22] T. R. Daram, B. N. Sri, D. Indhuja, G. Manisha, and A. K. Rao, "Low power design of carry look ahead adder by using adiabatic logic," *International Journal of Advanced Science and Technology*, vol. 29, no. 7, pp. 5271–5282, 2020.

- [23] S. M. Dadgar, R. Farazkish, and A. Sahafi, "Presentation of a fault tolerance algorithm for design of quantum-dot cellular automata circuits," *International Journal of Electrical and Computer Engineering*, vol. 12, no. 5, pp. 4722-4733, 2022, doi: 10.11591/ijece.v12i5.pp4722-4733.

- [24] A. D. Abbas, "Review of high-speed phase accumulator for direct digital frequency synthesizer," *International Journal of Electrical and Computer Engineering*, vol. 10, no. 4, pp. 4008-4014, 2020, doi: 10.11591/ijece.v10i4.pp4008-4014.

- [25] M. Sanadhya and D. K. Sharma, "Design and implementation of full subtractor using different adiabatic techniques," 2020 IEEE International Women in Engineering (WIE) Conference on Electrical and Computer Engineering (WIECON-ECE), 2020, pp. 102-106, doi: 10.1109/WIECON-ECE52138.2020.9397967.

- [26] P. Singh and P. K. Jain, "Design and Analysis of Low Power, High Speed 4 Bit Magnitude Comparator," 2018 International Conference on Recent Innovations in Electrical, Electronics & Communication Engineering (ICRIEECE), 2018, pp. 1680-1683, doi: 10.1109/ICRIEECE44171.2018.9008504.

- [27] M. T. Mustaffa, "A low power comparator utilizing MTSCStack, DTTS, and bulk-driven techniques," *International Journal of Reconfigurable and Embedded System.*, vol. 10, no. 3, pp. 221-229, 2021, doi: 10.11591/ijres.v10.i3.pp221-229.

- [28] Z. A. Altarawneh and M. A. B. Al-Tarawneh, "Design and analysis of single layer quantum dot-cellular automata based 1- bit comparators," *Telkomnika Telecommunication Computing Electronics and Control*, vol. 20, no. 1, pp. 141-148, 2022, doi: 10.12928/telkomnika.v20i1.18434.

- [29] S. Alkurwy, S. H. Ali, M. S. Islam, and F. Idros, "An area efficient memory-less ROM design architecture for direct digital frequency synthesizer," *International Journal of Electrical and Computer Engineering*, vol. 11, no. 1, pp. 257-264, 2021, doi: 10.11591/ijece.v11i1.pp257-264.

- [30] T. Suguna and M. J. Rani, "Analysis of combinational circuits using positive feed back adiabatic logic," *International Journal of Innovative Technology and Exploring Engineering*, vol. 8, no. 8, pp. 3390-3399, 2019.

- [31] A. K. Kumar, D. Somasundareswari, V. Duraisamy, and T. S. Pradeepa, "Design of low power multiplier with energy efficient full adder using DPTAAL," VLSI Design, vol. 2013, p. 157872, 2013, doi: 10.1155/2013/157872.

- [32] T. S. A. Samuel, S. Darwin, and N. Arumugam, "Design of adiabatic logic based comparator for low power and high speed applications," *ICTACT Journal on Microelectronics*, vol. 3, no. 1, pp. 365-369, 2017, doi: 10.21917/ijme.2017.064.

- [33] Sneha, B. Dwijesh, S. Magadum, K Sagar, and H. K. Moorthy, "Design and implementation of low power efficient 8-bit carry look ahead adder using adiabatic technique," *International Journal for Research in Applied Science and Engineering Technology*, vol. 7, no. 5, pp. 2857-2862, 2019, doi: 10.22214/ijraset.2019.5471.

## **BIOGRAPHIES OF AUTHORS**

Minakshi Sanadhya **B** S received her B.Tech. in Applied Electronics and Instrumentation from M.I.T. Engineering College, Kota in 2008 and M.Tech. Degree from SRM University, Chennai in 2010.Currently, she is working in SRM Institute of Science and Technology, Delhi NCR Campus, Ghaziabad, India as Assistant Professor and pursuing Ph.D. Her research interests include Digital circuit design, VLSI. She can be contacted at email: minakshisanadhya@gmail.com.

**Devendra Kumar Sharma D E C** received his B.E degree in Electronics Engineering from M.N.R. Engineering College, Allahabad, M.E degree from University of Roorkee, and PhD degree from NIT Kurukshetra, India in 1989, 1992 and 2016 respectively. He served PSUs in different positions for more than 8 years in QA & Testing/R & D departments. Currently, he is working in SRM Institute of Science and Technology, Delhi NCR Campus, Ghaziabad, India as a Professor and Dean. His research interests include VLSI interconnects, Digital design, Testing and Signal processing. He can be contacted at email: d\_k\_s1970@yahoo.co.in.