# Comparative investigation of 15 level and 17 level cascaded H-Bridge MLI with cross H-Bridge MLI fed permanent magnet synchronous motor

J. Srinivas Rao<sup>1</sup>, Suresh Kumar Tummala<sup>2</sup>, Dr. Narasimha Raju Kuthuri<sup>3</sup>

<sup>1,3</sup>EEE Department, KLEF, India

<sup>2</sup>EEE Department, Gokaraju Rangaraju Institute of Engineering & Tehnology, Hyderabad, India

#### **Article Info**

# Article history:

Received Jul 24, 2020 Revised Aug 11, 2020 Accepted Sep 18, 2020

#### Keywords:

Cross h bridge

Permanent magnet

Switching devices

Synchronous motor (PMSM)

Total harmonic distortion

#### **ABSTRACT**

Multilevel inverters offers eminent solutions to high voltage high power applications due to the association of several devices in a series configuration. In this paper, a comparative investigation of both 15 and 17 level cascaded H-Bridge multi level inverter with cross H-Bridge fed permanent magnet synchronous motor are presented by appropriate simulations and mathematical analysis. Comparative analysis includes Inverter output voltage and current, number of switching devices, stator current and speed of PMSM and total harmonic distortion levels. Limitation of several switching devices, which can afford high voltage in the inverter is the major problems raised in this study. The advantage of this analysis is to figure out the appropriate inverter that can be used for real time application by considering the factors via. Harmonic distortion, output voltage, current, number of switching devices etc. Validation of the analysis is processed through Matlab/Simulink Platform.

This is an open access article under the CC BY-SA license.

723

#### Corresponding Author:

J. Srinivas Rao EEE Department

K L University/KLEF, India

Email: janigasrinivasrao@gmail.com

# 1. INTRODUCTION

Micro grids are increasing day by day, which is combination of many sources like Diesel Generators, Solar power, Wind power, Fuel cell etc. To integrate these sources with power grid or to supply power to local loads power electronic converters play an important role. The two-level inverter cannot supply the power to medium and high power loads with good efficiency but multilevel inverters can supply the power at good efficiency.

The primary principle of MLI is to share the operating voltage of inverter between switches connected in circuit. So switches with low rating can be used in high voltage/power rating applications, which reduce the cost of inverter. As level of output voltage increases level of harmonics decreases at low switching frequencies so cost of filters reduces [1, 2].

The major topologies of multilevel inverters are Diode clamped (NPC) multilevel inverter [3], Capacitor clamped (FC) multilevel inverter [4] and Cascaded H bridge (CHB) multilevel inverter [5]. The common problem among above topologies is number of switches required [6, 7] increases significantly with increase in output voltage level [8], which tends to increase in cost, size and complexity of switching and implementation of hardware circuit [9-11]. The NPC multilevel inverter and the FC multilevel inverter, the

724 🗖 ISSN: 2502-4752

capacitor voltage can be regulated using redundant switching states but as the level of voltage increase the number of capacitors and clamping diodes required and complexity in control scheme increases.

In cascaded H bridge multilevel inverter, the H-Bridge cells with DC source are connected in series. Based on the type of DC sources CHB multilevel inverter is classified as symmetrical (equal DC sources) [12-14] and asymmetrical (unequal DC sources) [15-17]. The symmetric topology gives good modularity and packaging due to the identical structure of each H – Bridge but number of switches increases rapidly with the increase in level of output voltage. With asymmetric topology the level of output voltage can be increased with less number of switches but the rating of some of the switches is nearly equal the maximum operating voltage and designing of hardware circuit is more challeging. The topologies discussed above are conventional. Many topologies are invented in recent years. The cross H bridge multilevel inverter [18] is connected with specific cross connections with DC sources as shown in Figure 2 and Figure 4. Due to enormous applications there is a huge attention on multilevel inverters. Multilevel output generated using multi winding transformer [19, 20] is not economical for high power/voltage applications.

In this paper, a comparative investigation of 15 and 17level MLI for both cascade and cross H-Bridge switching configurations are presented, for both cascaded & cross H-Bridge inverter level of harmonic content reduces with the increase in the level of voltage. The proposed 3-phase 15 & 17- level multilevel inverter is fed to PMSM and verified speed and stator current of the motor.

#### 2. SWITCHING PROFILE

# 2.1. The relation between level of output voltage, number of switches and number of voltage sources Cross H Bridge:

$$N_s = V_L + 1 \tag{1}$$

$$V_L = 2*V_S + 1 \tag{2}$$

$$N_s = 2(V_s + 1)$$

(3)

$$N_D = \frac{V_L + 1}{2} \tag{4}$$

Cascaded H Bridge:

$$N_s = 2*(V_L - 1)$$

(5)

$$V_L = 2*V_S + 1 \tag{6}$$

$$N_{\rm S}=4*V_{\rm S} \tag{7}$$

$$N_D = V_L - 1 \tag{8}$$

Where  $V_L$  is level of output voltage,  $N_s$  is number of switches,  $V_s$  is number of voltage sources,  $N_D$ =no. of switching devices in current path. Comparison of number of switches for the above two topologies is shown Table 3.

#### 2.2. Switches voltage rating

In cross H bridge MLI the standing voltage of switches  $S_1, S_2, S_{n-1}$  and  $S_n$  is  $V_{dc}$  and other switches standing voltage [21-23] is  $2V_{dc}$  and the standing voltage of all switches in cascaded H bridge is  $V_{dc}$ . The total standing Voltage of cross H brige MLI and cascaded H bridge is  $2*(V_L - 1)*V_{dc}$

Where  $V_L$  is level of output voltage.

#### 2.3. Switch losses

The major losses of the switches are conduction and switching losses [24-26]. Conduction losses occur due to on-state voltage drop and equivalent resistance. Switching losses occur due to non ideal operation of switches. The average conduction losses of a transistor  $(P_c, T(t))$  and diode  $(P_c, D(t))$  can be written as follows:

$$P_{c}, T = \frac{1}{2\pi} \int [V_T + R_T i^{\beta}(t)] i(t) d(\omega t)$$

$$\tag{9}$$

$$P_{c}, D = \frac{1}{2\pi} \int [V_{D} + R_{D}i(t)]i(t) d(\omega t)$$

(10)

The total conduction losses of multilevel inverter per cycle  $(P_c) = (P_c, T + P_c, D) * N_D$  (11)

The switching loss of the switches is given as  $P(sw) = f * (T_{on} * E_{on} + T_{off} * T_{off} * E_{off})$  (12)

Where  $V_T$  and  $V_D$  are transistor and diode voltage drop (on state) respectively.  $R_T$  and  $R_D$  are transistor and diode equivalent resistance respectively, f= frequency,  $T_{on}$ =no. of times switches on,  $T_{off}$ =no. of times switches off. Comparison of switching losses of discussed topologies are shown in Table 4.

#### 3. 15-LEVEL MULTILEVEL INVERTER

# 3.1. Cascaded H-Bridge

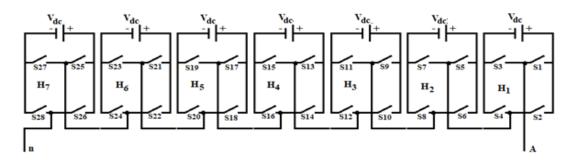

Figure 1 shows cascaded H-Bridge 15-level MLI with seven dc sources and 28 switches. Four switches comprise one leg and each leg is connected to one dc source of same voltage rating.

Figure 1. Single phase 15-level cascaded H-Bridge MLI

# 3.2. Cross H-Bridge

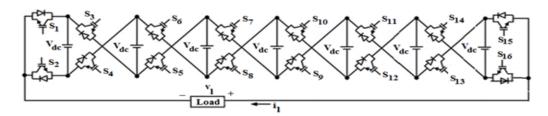

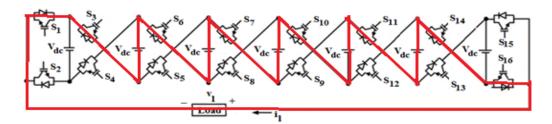

From (1) number of switches required in cross H-Bridge MLI is  $2(V_s+1) = 2*(7+1) = 16$  switches, the same can be seen from Figure 2. Where  $V_s$  is number of voltage sources. Switching configuration for Single Phase 15-level Cross H-Bridge MLI is shown in Table 1. For each output voltage there are various switching patterns as shown in Table 1. However for the complete analysis the highlited switching pattern (in bold) is considered. The conduction path for +5Vdc is shown in Figure 2(b).

Figure2(a). Single phase 15-level cross H-Bridge MLI

Figure 2(b). Conduction path for +5Vdc of 15-level cross H-Bridge MLI

| S.No. | O/P Voltage       | 1. Switching pattern of Switches ON    | S.No. | O/P Voltage         | Switches ON                                                                                                                |

|-------|-------------------|----------------------------------------|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1     | 7 V <sub>DC</sub> | $S_2S_3S_6S_7S_{10}S_{11}S_{14}S_{15}$ | 9     | - 7 V <sub>DC</sub> | S <sub>1</sub> S <sub>4</sub> S <sub>5</sub> S <sub>8</sub> S <sub>9</sub> S <sub>12</sub> S <sub>13</sub> S <sub>16</sub> |

| 2     | 637               | $S_1S_3S_6S_7S_{10}S_{11}S_{14}S_{15}$ | 10    | CV                  | $S_1S_4S_5S_8S_9S_{12}S_{13}S_{15}$                                                                                        |

| 2     | $6 V_{DC}$        | $S_2S_3S_6S_7S_{10}S_{11}S_{14}S_{16}$ | 10    | - 6 V <sub>DC</sub> | $S_2S_4S_5S_8S_9S_{12}S_{13}S_{16}$                                                                                        |

|       |                   | $S_1S_3S_6S_7S_{10}S_{11}S_{14}S_{16}$ |       |                     | $S_1S_4S_5S_8S_9S_{12}S_{14}S_{16}$                                                                                        |

| 3     | $5 V_{DC}$        | $S_2S_3S_6S_7S_{10}S_{11}S_{13}S_{15}$ | 11    | - 5 V <sub>DC</sub> | $S_1S_3S_5S_8S_9S_{12}S_{13}S_{16}$                                                                                        |

|       |                   | $S_2S_4S_6S_7S_{10}S_{11}S_{14}S_{15}$ |       |                     | $S_2S_4S_5S_8S_9S_{12}S_{13}S_{15}$                                                                                        |

|       |                   | $S_1S_3S_6S_7S_{10}S_{11}S_{13}S_{15}$ |       | - 4 V <sub>DC</sub> | $S_1S_4S_5S_8S_9S_{11}S_{13}S_{15}$                                                                                        |

| 4     | $4 V_{DC}$        | $S_1S_3S_6S_7S_{10}S_{11}S_{14}S_{15}$ | 12    |                     | $S_1S_3S_5S_8S_9S_{12}S_{13}S_{15}$                                                                                        |

| 4     | 4 V DC            | $S_2S_3S_6S_7S_{10}S_{12}S_{14}S_{16}$ | 12    |                     | $S_2S_4S_5S_8S_9S_{12}S_{14}S_{16}$                                                                                        |

|       |                   | $S_2S_4S_6S_7S_{10}S_{11}S_{14}S_{16}$ |       |                     | $S_2S_4S_6S_8S_9S_{12}S_{13}S_{16}$                                                                                        |

|       |                   | $S_1S_3S_6S_7S_{10}S_{12}S_{14}S_{16}$ |       |                     | $S_1S_3S_5S_8S_{10}S_{12}S_{14}S_{16}$                                                                                     |

|       |                   | $S_1S_3S_5S_7S_{10}S_{11}S_{14}S_{16}$ |       |                     | $S_1S_3S_5S_8S_9S_{12}S_{14}S_{16}$                                                                                        |

| 5     | $3 V_{DC}$        | $S_2S_3S_6S_7S_9S_{11}S_{13}S_{15}$    | 13    | - 3 V <sub>DC</sub> | $S_1S_3S_5S_7S_9S_{12}S_{13}S_{16}$                                                                                        |

|       |                   | $S_2S_4S_6S_7S_{10}S_{11}S_{13}S_{15}$ |       |                     | $S_2S_4S_5S_8S_9S_{11}S_{13}S_{15}$                                                                                        |

|       |                   | $S_2S_4S_6S_8S_{10}S_{11}S_{14}S_{15}$ |       |                     | $S_2S_4S_6S_8S_9S_{12}S_{13}S_{15}$                                                                                        |

|       |                   | $S_1S_3S_6S_7S_9S_{11}S_{13}S_{15}$    |       |                     | $S_1S_4S_5S_7S_9S_{11}S_{13}S_{15}$                                                                                        |

|       |                   | $S_1S_3S_5S_7S_{10}S_{11}S_{13}S_{15}$ |       |                     | $S_1S_3S_5S_8S_9S_{11}S_{13}S_{15}$                                                                                        |

| 6     | $2 V_{DC}$        | $S_1S_3S_5S_7S_9S_{11}S_{14}S_{15}$    | 14    | - 2 V <sub>DC</sub> | $S_1S_3S_5S_7S_9S_{12}S_{13}S_{15}$                                                                                        |

| U     | ∠ V DC            | $S_2S_3S_6S_8S_{10}S_{12}S_{14}S_{16}$ | 14    | - 2 <b>v</b> DC     | $S_2S_4S_5S_8S_{10}S_{12}S_{14}S_{16}$                                                                                     |

|       |                   | $S_2S_4S_6S_7S_{10}S_{12}S_{14}S_{16}$ |       |                     | $S_2S_4S_6S_8S_9S_{12}S_{14}S_{16}$                                                                                        |

|       |                   | $S_2S_4S_6S_8S_{10}S_{11}S_{14}S_{16}$ |       |                     | $S_2S_4S_6S_8S_{10}S_{12}S_{13}S_{16}$                                                                                     |

|       |                   | $S_1S_3S_6S_8S_{10}S_{12}S_{14}S_{16}$ |       |                     | $S_1S_4S_6S_8S_{10}S_{12}S_{14}S_{16}$                                                                                     |

|       |                   | $S_1S_3S_5S_7S_{10}S_{12}S_{14}S_{16}$ |       |                     | $S_1S_3S_5S_8S_{10}S_{12}S_{14}S_{16}$                                                                                     |

|       |                   | $S_1S_3S_5S_7S_9S_{11}S_{14}S_{16}$    |       |                     | $S_1S_3S_5S_7S_9S_{12}S_{14}S_{16}$                                                                                        |

| 7     | $V_{DC}$          | $S_2S_3S_5S_7S_9S_{11}S_{13}S_{15}$    | 15    | - $V_{DC}$          | $S_1S_3S_5S_7S_9S_{11}S_{13}S_{16}$                                                                                        |

|       |                   | $S_2S_4S_6S_7S_9S_{11}S_{13}S_{15}$    |       |                     | $S_2S_4S_5S_7S_9S_{11}S_{13}S_{15}$                                                                                        |

|       |                   | $S_2S_4S_6S_8S_{10}S_{12}S_{13}S_{15}$ |       |                     | $S_2S_4S_6S_8S_9S_{11}S_{13}S_{15}$                                                                                        |

|       |                   | $S_2S_4S_6S_8S_{10}S_{12}S_{14}S_{15}$ |       |                     | $S_2S_4S_6S_8S_{10}S_{12}S_{13}S_{15}$                                                                                     |

| 8     | 0                 | $S_1S_3S_5S_7S_9S_{11}S_{13}S_{15}$    |       |                     |                                                                                                                            |

| O     | U                 | $S_2S_4S_6S_8S_{10}S_{12}S_{14}S_{16}$ |       |                     |                                                                                                                            |

# 4. 17-LEVEL MULTILEVEL INVERTER

### 4.1. Cascaded H-Bridge

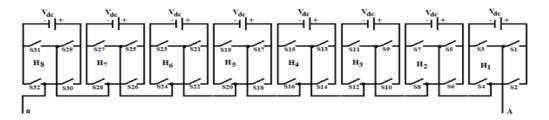

Figure 3 shows cascaded H-Bridge 17-level MLI with eight dc sources and 32 switches. Four switches comprise one leg and each leg is connected to one dc source of same voltage rating.

Figure 3. Single phase 17-level cascaded H-Bridge MLI

# 4.2. Cross H-Bridge

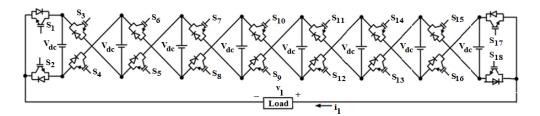

From (1) number of switches required in cross H-Bridge MLI is  $2(V_s+1) = 2*(8+1) = 18$  switches, the same can be seen from Figure 4. Where  $V_s$  is number of voltage sources.

Figure 4. Single phase 17-level cross H-Bridge MLI

| Table 2. Switching | nottorn of area | G H Dridge   | 17 lovel MI I   |

|--------------------|-----------------|--------------|-----------------|

| Table 2. Switching | dattern of cros | s H-Briage . | i /-ievei willi |

|       | Table 2. Switching pattern of cross H-Bridge 1/-level MLI |                                              |       |                     |                                              |  |  |

|-------|-----------------------------------------------------------|----------------------------------------------|-------|---------------------|----------------------------------------------|--|--|

| S.No. | O/P Voltage                                               | Switches ON                                  | S.No. | O/P Voltage         | Switches ON                                  |  |  |

| 1     | $8 V_{DC}$                                                | $S_2S_3S_6S_7S_{10}S_{11}S_{14}S_{15}S_{18}$ | 10    | - 8 V <sub>DC</sub> | $S_1S_4S_5S_8S_9S_{12}S_{13}S_{16}S_{17}$    |  |  |

| 2     | $7 V_{DC}$                                                | $S_2S_3S_6S_7S_{10}S_{11}S_{14}S_{15}S_{17}$ | 11    | - 7 V <sub>DC</sub> | $S_1S_4S_5S_8S_9S_{12}S_{13}S_{16}S_{18}$    |  |  |

| 2     | / <b>V</b> DC                                             | $S_1S_3S_6S_7S_{10}S_{11}S_{14}S_{15}S_{18}$ | 11    | - / <b>v</b> DC     | $S_2S_4S_5S_8S_9S_{12}S_{13}S_{16}S_{17}$    |  |  |

|       |                                                           | $S_2S_3S_6S_7S_{10}S_{11}S_{14}S_{16}S_{18}$ |       |                     | $S_1S_4S_5S_8S_9S_{12}S_{13}S_{15}S_{17}$    |  |  |

| 3     | $6 V_{DC}$                                                | $S_2S_4S_6S_7S_{10}S_{11}S_{14}S_{15}S_{18}$ | 12    | - 6 V <sub>DC</sub> | $S_1S_3S_5S_8S_9S_{12}S_{13}S_{16}S_{17}$    |  |  |

|       |                                                           | $S_1S_3S_6S_7S_{10}S_{11}S_{14}S_{15}S_{18}$ |       |                     | $S_2S_4S_5S_8S_9S_{12}S_{13}S_{16}S_{18}$    |  |  |

|       |                                                           | $S_2S_3S_6S_7S_{10}S_{11}S_{13}S_{15}S_{17}$ |       |                     | $S_1S_4S_5S_8S_9S_{12}S_{14}S_{16}S_{18}$    |  |  |

| 4     | $5 V_{DC}$                                                | $S_2S_4S_6S_7S_{10}S_{11}S_{14}S_{15}S_{17}$ | 13    | - 5 V <sub>DC</sub> | $S_1S_3S_5S_8S_9S_{12}S_{13}S_{16}S_{18}$    |  |  |

| 4     | J V DC                                                    | $S_1S_3S_6S_7S_{10}S_{11}S_{14}S_{16}S_{18}$ | 13    |                     | $S_2S_4S_5S_8S_9S_{12}S_{13}S_{15}S_{17}$    |  |  |

|       |                                                           | $S_1S_3S_5S_7S_{10}S_{11}S_{14}S_{15}S_{18}$ |       |                     | $S_2S_4S_5S_8S_{10}S_{12}S_{13}S_{16}S_{17}$ |  |  |

|       |                                                           | $S_2S_3S_6S_7S_{10}S_{12}S_{14}S_{16}S_{18}$ |       |                     | $S_1S_4S_5S_8S_9S_{11}S_{13}S_{15}S_{17}$    |  |  |

| 5     |                                                           | $S_2S_4S_6S_7S_{10}S_{11}S_{14}S_{16}S_{18}$ |       | - 4 V <sub>DC</sub> | $S_1S_3S_5S_8S_9S_{12}S_{13}S_{15}S_{17}$    |  |  |

|       | $4 V_{DC}$                                                | $S_2S_4S_6S_8S_{10}S_{11}S_{14}S_{15}S_{18}$ | 14    |                     | $S_1S_3S_5S_7S_9S_{12}S_{13}S_{16}S_{17}$    |  |  |

|       |                                                           | $S_1S_3S_6S_7S_{10}S_{11}S_{13}S_{15}S_{17}$ |       |                     | $S_2S_4S_5S_8S_9S_{12}S_{14}S_{16}S_{18}$    |  |  |

|       |                                                           | $S_1S_3S_5S_7S_{10}S_{11}S_{14}S_{15}S_{17}$ |       |                     | $S_2S_4S_6S_8S_9S_{12}S_{13}S_{16}S_{18}$    |  |  |

|       |                                                           | $S_2S_3S_6S_7S_9S_{11}S_{13}S_{15}S_{17}$    |       |                     | $S_1S_4S_5S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ |  |  |

|       |                                                           | $S_2S_4S_6S_7S_{10}S_{11}S_{13}S_{15}S_{17}$ |       |                     | $S_1S_3S_5S_8S_9S_{12}S_{14}S_{16}S_{18}$    |  |  |

| 6     | $3 V_{DC}$                                                | $S_2S_4S_6S_8S_{10}S_{11}S_{14}S_{15}S_{17}$ | 15    | - 3 V <sub>DC</sub> | $S_1S_3S_5S_7S_9S_{12}S_{13}S_{16}S_{18}$    |  |  |

| 6     | 3 V <sub>DC</sub>                                         | $S_1S_3S_6S_7S_{10}S_{12}S_{14}S_{16}S_{18}$ | 13    |                     | $S_2S_4S_5S_8S_9S_{12}S_{14}S_{16}S_{18}$    |  |  |

|       |                                                           | $S_1S_3S_5S_7S_{10}S_{11}S_{14}S_{16}S_{18}$ |       |                     | $S_2S_4S_6S_8S_9S_{12}S_{13}S_{15}S_{17}$    |  |  |

|       |                                                           | $S_1S_3S_5S_7S_9S_{11}S_{14}S_{15}S_{18}$    |       |                     | $S_2S_4S_6S_8S_{10}S_{12}S_{13}S_{16}S_{17}$ |  |  |

|       |                                                           | $S_2S_3S_6S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ |       |                     | $S_1S_4S_5S_7S_9S_{11}S_{13}S_{15}S_{17}$    |  |  |

|       |                                                           | $S_2S_4S_6S_7S_{10}S_{12}S_{14}S_{16}S_{18}$ |       |                     | $S_1S_3S_5S_8S_9S_{11}S_{13}S_{15}S_{17}$    |  |  |

|       |                                                           | $S_2S_4S_6S_8S_{10}S_{11}S_{14}S_{16}S_{18}$ |       |                     | $S_1S_3S_5S_7S_9S_{12}S_{13}S_{15}S_{17}$    |  |  |

| 7     | $2 V_{DC}$                                                | $S_2S_4S_6S_8S_{10}S_{12}S_{14}S_{15}S_{18}$ | 16    | - 2 V <sub>DC</sub> | $S_1S_3S_5S_7S_9S_{11}S_{13}S_{16}S_{17}$    |  |  |

|       |                                                           | $S_1S_3S_6S_7S_9S_{11}S_{13}S_{15}S_{17}$    |       |                     | $S_2S_4S_5S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ |  |  |

|       |                                                           | $S_1S_3S_5S_7S_{10}S_{11}S_{13}S_{15}S_{17}$ |       |                     | $S_2S_4S_6S_8S_9S_{12}S_{14}S_{16}S_{18}$    |  |  |

|       |                                                           | $S_1S_3S_5S_7S_9S_{11}S_{14}S_{15}S_{17}$    |       |                     | $S_2S_4S_6S_8S_{10}S_{12}S_{13}S_{16}S_{18}$ |  |  |

|       |                                                           | $S_1S_3S_5S_7S_9S_{11}S_{13}S_{15}S_{18}$    |       |                     | $S_1S_4S_6S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ |  |  |

|       | $V_{ m DC}$                                               | $S_1S_3S_5S_7S_9S_{11}S_{14}S_{16}S_{18}$    |       |                     | $S_1S_3S_5S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ |  |  |

|       |                                                           | $S_1S_3S_5S_7S_{10}S_{12}S_{14}S_{16}S_{18}$ |       |                     | $S_1S_3S_5S_7S_9S_{12}S_{14}S_{16}S_{18}$    |  |  |

| 8     |                                                           | $S_1S_3S_6S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ | 17    | V                   | $S_1S_3S_5S_7S_9S_{11}S_{13}S_{16}S_{18}$    |  |  |

| 0     |                                                           | $S_2S_3S_5S_7S_9S_{11}S_{13}S_{15}S_{17}$    | 1 /   | - V <sub>DC</sub>   | $S_2S_4S_5S_7S_9S_{11}S_{13}S_{15}S_{17}$    |  |  |

|       |                                                           | $S_2SS_4S_6S_7S_9S_{11}S_{13}S_{15}S_{17}$   |       |                     | $S_2S_4S_6S_8S_9S_{11}S_{13}S_{15}S_{17}$    |  |  |

|       |                                                           | $S_2S_4S_6S_8S_{10}S_{11}S_{13}S_{15}S_{17}$ |       |                     | $S_2S_4S_6S_8S_{10}S_{12}S_{13}S_{15}S_{17}$ |  |  |

|       |                                                           | $S_2S_4S_6S_8S_{10}S_{12}S_{14}S_{15}S_{17}$ |       |                     | $S_2S_4S_6S_8S_{10}S_{12}S_{14}S_{16}S_{17}$ |  |  |

| 9     | 0                                                         | $S_1S_3S_5S_7S_9S_{11}S_{13}S_{15}S_{17}$    |       |                     |                                              |  |  |

| 7     | U                                                         | $S_2S_4S_6S_8S_{10}S_{12}S_{14}S_{16}S_{18}$ |       |                     |                                              |  |  |

The number of switches required for 15-level cross H bridge is reduced by 42.8% per phase when compared to 15-level cascaded H bridge and number of switches required for 17-level cross H bridge is reduced by 43.7% when compared to 17-level cascaded H bridge per phase this can be observed from Table 3. The losse of 15-level cross H bridge is reduced by 24.1% per phase when compared to 15-level cascaded H bridge and the losse of 17-level cross H bridge is reduced by 24.8% per phase when compared to 17-level cascaded H bridge this can be observed from Table 4.

Table 3. Number of switching devices vs output voltage levels

|                       | No. of Switching Devices |         |                     |         |  |

|-----------------------|--------------------------|---------|---------------------|---------|--|

| OUTPUT VOLTAGE LEVELS | Cascaded H-Bridge MLI    |         | Cross H- Bridge MLI |         |  |

|                       | 1-Phase                  | 3-Phase | 1-Phase             | 3-Phase |  |

| 15 LEVEL              | 28                       | 84      | 16                  | 48      |  |

| 17 LEVEL              | 32                       | 96      | 18                  | 54      |  |

| ·                     |                          |         |                     |         |  |

Table 4. Total losses of switches vs output voltage levels

| Tuest Wilder to be a strained to a during the test |                       |             |                     |             |  |

|----------------------------------------------------|-----------------------|-------------|---------------------|-------------|--|

|                                                    | f switches(w)         | _           |                     |             |  |

| OUTPUT VOLTAGE LEVELS                              | Cascaded H-Bridge MLI |             | Cross H- Bridge MLI |             |  |

|                                                    | Single Phase          | Three Phase | Single Phase        | Three Phase |  |

| 15 LEVEL                                           | 17.13                 | 51.39       | 12.99               | 38.97       |  |

| 17 LEVEL                                           | 19.08                 | 57.24       | 14.33               | 42.99       |  |

#### 5. RESULTS

In this paper simulation of 15-level and 17-level cross H bridge and cascaded H bridge multilevel inverters is carried in MATALB/SIMULINK environment with seven and eight separate DC sources of 10V

to get 70V and 80V maximum output voltage respectively. The switch IGBT (FGA15N120ANTD) is considered for calculating the switch losses and the Permanent Magnet Synchronous Motor of rating of 0.5hp connected as load. Comparison of losses of cross H Bridge and Cascaded H bridge topologies is shown in Table 4.

# 5.1. 15-level cascaded H-Bridge inverter fed PMSM

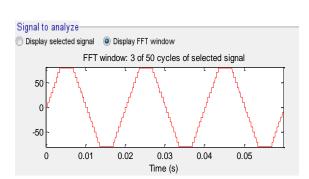

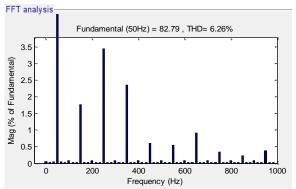

Figures 5-8 represents stator current Phase-A, three phse inverter voltage, speed of motor and THD of 15- Level Cascaded H-Bridge MLI respectively

Figure 5. Stator current of Phase-A

Figure 6. Three phase 15-level cascaded H-Bridge inverter output voltage

Figure 7. Speed of PMSM

Figure 8. Total harmonic distortion of 15- level cascaded H-Bridge MLI (Phase A)

# 5.2. 15-level cross H-Bridge inverter fed PMSM

Figures 9-12 represents stator current Phase-A, three phse inverter voltage, speed of motor and THD of 15- Level Cross H-Bridge MLI respectively. The Total Harmonic Distortion of 15- Level Cross H-Bridge is reduced by 3.48% when compared to 15-level cascaded H-Bridge the same can be observed from Figure 8 and Figure 12.

Figure 9. Stator current of Phase-A

Figure 10. Three phase 15-level cross H-Bridge inverter output voltage

Figure 11. Speed of PMSM

Figure 12. Total harmonic distortion of 15 level cross H-Bridge MLI (Phase A)

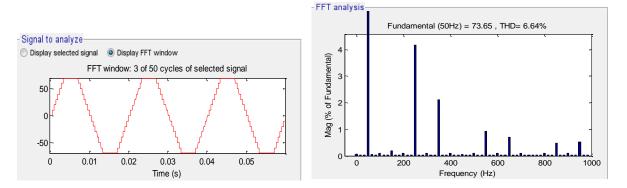

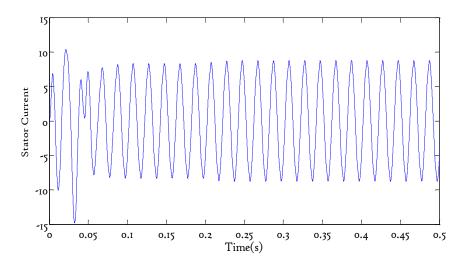

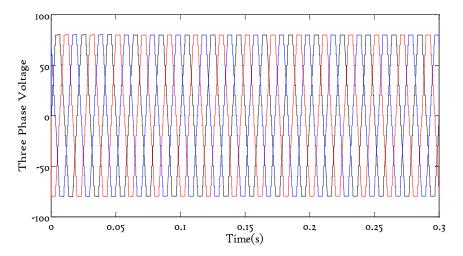

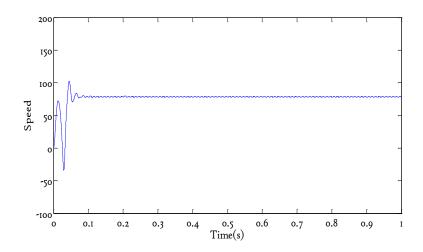

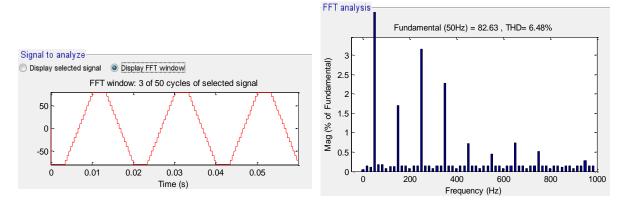

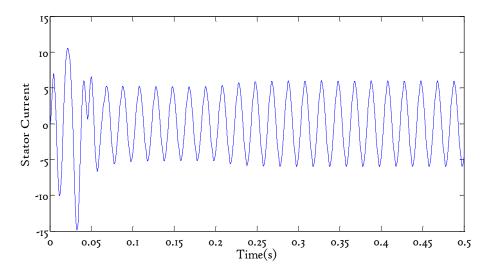

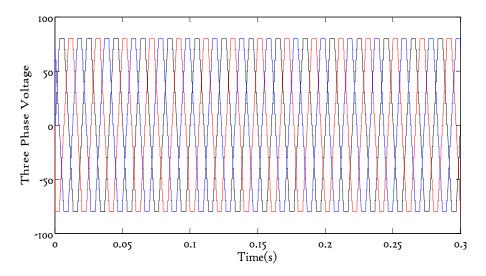

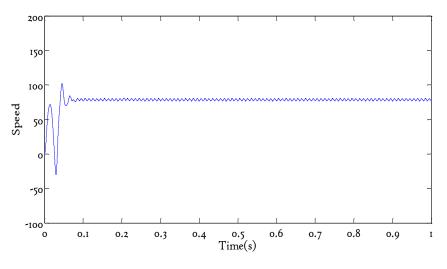

# 5.3. 17- level cascaded H-Bridge inverter fed PMSM

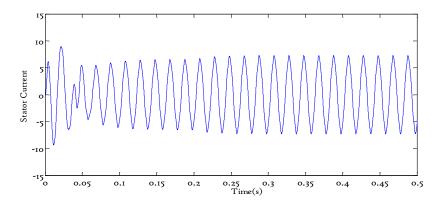

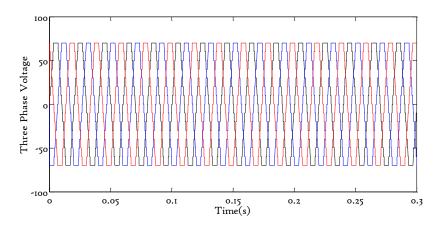

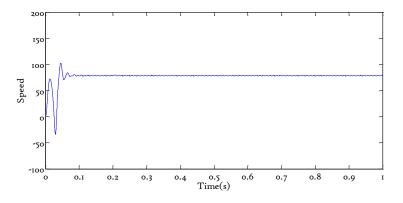

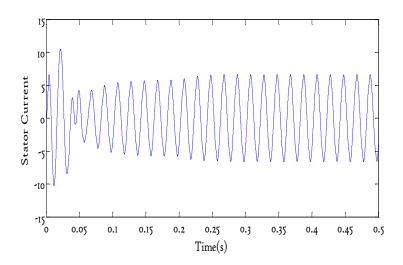

Figures 13-16 represents stator current Phase-A, three phse inverter voltage, speed of motor and THD of 17- Level Cascaded H-Bridge MLI respectively.

Figure 13. Stator current of Phase-A

Figure 14. Three phase 17-level cascaded H-Bridge inverter output voltage

Figure 15. Speed of PMSM

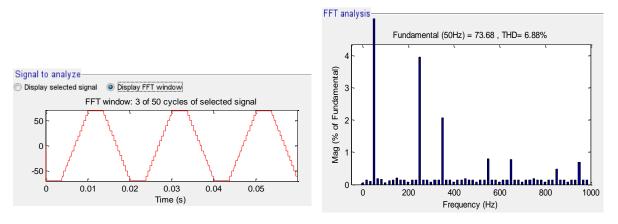

Figure 16. Total harmonic distortion of 17 level cascaded H-Bridge MLI (Phase A)

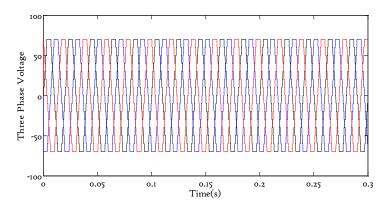

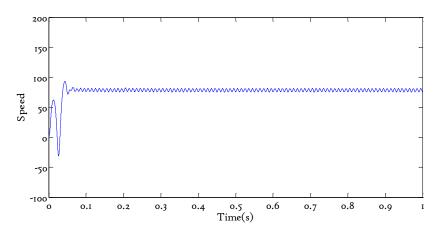

# 5.4. 17- level cross H-Bridge inverter fed PMSM

Figures 17-20 represents stator current Phase-A, three phse inverter voltage, speed of motor and THD of 17 Level Cross H-Bridge MLI respectively. The Total Harmonic Distortion of 17- Level Cross H-Bridge is reduced by 3.39% when compared to 17-level cascaded H-Bridge the same can be observed from Figure 16 and Figure 20.

Figure 17. Stator current of Phase-A

Figure 18. Three phase 17-level cross H-Bridge inverter output voltage

Figure 19. Speed of PMSM

Figure 20. Total harmonic distortion of 17 level cascaded H-Bridge MLI (Phase A)

#### 6. CONCLUSION

Nowadays, multilevel inverter topologies are best choice for many industrial applications owing to their advantages like low EMI, high efficiency and high reliability. This paper presented the comparative analysis of 15 and 17- level cascaded and cross H-Bridge multi-level inverter fed PMSM drive. The intention in this paper is to endow with superior quality of voltage (output) with little THD by evaluating the discussed multilevel converter topologies. From the analysis it is clear that the number of switches required, THD and switch losses of cross H-Bridge configured multilevel inverters is less when compared to cascaded H bridge configuration.

#### **ACKNOWLEDGEMENT**

Authors would like to thank All India Council for Technical Education (AICTE, New Delhi), INDIA for supporting this work under Research Promotion Scheme. File No.: 8-174/RIFD/RPS (Policy-1)/2018-19.

#### REFERENCES

- [1] P. Omer, J. Kumar and B. S. Surjan, "A Review on Reduced Switch Count Multilevel Inverter Topologies," *IEEE Access*, vol. 8, pp. 22281-22302, 2020.

- [2] E.Babaei, C. Buccella, M. Saeedifard. "Recent Advances in Multilevel Inverter and their Applications: Part I", *IEEE Trans. Ind. Electro.*, vol. 63, no. 11, pp 7145-7147, 2016.

- [3] J. Rodriguez, S. Bernet, P. Steimer, and I. Lizama, "A survey on neutral point clamped inverters," *IEEE Trans. Ind. Electro.*, vol. 57, no. 7, pp. 2219-2230, 2010.

- [4] M. M. Shobini, J. Kamala and R. Rathna, "Analysis and simulation of flying capacitor multilevel inverter using PDPWM strategy," 2017 ICIMIA, Bangalore, 2017.

- [5] M. Pamujula, A. Ohja, R. D. Kulkarni and P. Swarnkar, "Cascaded 'H' Bridge based Multilevel Inverter Topologies: A Review," 2020 INCET, Belgaum, India, pp. 1-7, 2020.

- [6] M. Sarbanzadeh, M. A. Hosseinzadeh, E. Sarbanzadeh, L. Yazdani, M. Rivera, and J. Riveros, "New fundamental multilevel inverter with reduced number of switching elements," *Proc. - 2017 IEEE South. Power Electron. Conf.* SPEC 2017, January, pp. 1-6, 2017.

- [7] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A New Multilevel Inverter Topology with Reduce Switch Count," *IEEE Access*, vol. 7, pp. 58584-58594, 2019.

- [8] V. V. Nagi Reddy, D. V. A. Kumar, and V. R. Kota, "A multilevel UPQC for voltage and current quality improvement in distribution system," *International Journal of Power Electronics and Drive System.*, vol. 10, no. 4, p. 1932, 2019.

- [9] C. L. Toh and P. C. Ooi, "Design a nine-level modular multilevel converter for DC railway electrification system," International Journal of Power Electronics and Drive System., vol. 11, no. 1, pp. 151-159, 2020.

- [10] E. Najafi and A. H. M. Yatim, "Design and implementation of a new multilevel inverter topology," *IEEE Trans. Ind. Electron.*, vol. 59, no. 11, pp. 4148-4154, 2012.

- [11] M. A. Hosseinzadeh, M. Sarbanzadeh, J. Munoz, M. Rivera, C. Munoz, and A. Villalon, "New reduced switched multilevel inverter for three-phase grid-connected pv system, performance evaluation," *Proc. IEEE Int. Conf. Ind. Technol.*, pp. 1488-1493, 2019.

- [12] S. S. Lee, M. Sidorov, N. R. N. Idris and Y. E. Heng, "A Symmetrical Cascaded Compact-Module Multilevel Inverter (CCM-MLI) with Pulse width Modulation," *IEEE Trans. Ind. Electro*, vol/ 65, no. 6, pp. 4631-4639, 2018.

- [13] L. Nanda, P. Bharti and A. Dasgupta, "Symmetrical and Asymmetrical Topology of Cascaded Multilevel Inverter With Reduced Number of Switches And DC Sources," 2019 IEEE ICSETS, Bhubaneswar, India, pp. 230-235, 2019.

734 🗖 ISSN: 2502-4752

[14] M. H. Yatim, A. Ponniran, M. A. Zaini, M. S. Shaili, N. A. S. Ngamidun, and A. N. Kasiran, "Symmetrical and Asymmetrical Multilevel Inverter Structures with Reduced Number of Switching Devices," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 11, no. 1, pp. 144-151, pp144-151, 2018.

- [15] K. Thakre, K. B. Mohanty, V. Kommukuri and R. N. Mishra, "Symmetrical and asymmetrical multilevel inverter using less number of switches," *IEEE TENCON Conference*, Penang, pp. 1032-1036, 2017.

- [16] B. Mahato, S. Mittal and P. k. Nayak, "Generalized Symmetrical/Asymmetrical Single-phase MLI Topology," 2018 RTECC, Malaysia, pp. 182-187, 2018.

- [17] D. A. B. Zambra, C. Rech and J. R. Pinheiro, "Comparison of Neutral-Point-Clamped, Symmetrical, and Hybrid Asymmetrical Multilevel Inverters," *IEEE Trans. Ind. Electro*, vol. 57, no. 7, pp. 2297-2306, 2010.

- [18] Mohammad Farhadi Kangarlu, Ebrahim Babaei "Cross-switched multilevel inverter: an innovative topology" *IET Power Electron.*, vol. 6, no. 4, pp. 642-651, 2013.

- [19] R. Teodorescu, F. Blaabjerg, J. K. Pedersen, E. Cengelci, and P. N. Enjeti, "Multilevel inverter by cascading industrial VSI," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 832-838, 2002.

- [20] D. A. B. Zambra, C. Rech, and J. R. Pinheiro, "A comparative analysis between the symmetric and the hybrid asymmetric nine-level series connected H-bridge cells inverter," *Proc. Eur. Conf. Power Electron. Appl.*, pp. 1-10, 2007

- [21] J. Srinivas Rao, P. Srinivasa Varma, T. Suresh Kumar, "Novel Switching Design Structure for Three Phase 21-Level Multilevel Inverter Fed BLDC Drive Application", *International Journal of Power Electronics and Drive System*, vol. 9, no. 3, pp. 1202-1213, 2018.

- [22] A. Anan, T. K. Chakraborty, and K. Sultan Mahmood, "A Single-Phase Cascaded H-Bridge Multilevel Inverter with Reduced Switching Devices and Harmonics," 2018 6th IEEE Int. Conf. Smart Energy Grid Eng., pp. 222-225, 2018.

- [23] K. Wei, C. Zhang, X. Gong, and T. Kang, "The IGBT Losses Analysis and Calculation of Inverter for Two-seat Electric Aircraft Application," *Energy Procedia*, vol. 105, pp. 2623-2628, 2017.

- [24] B. Alamri and M. Darwish, "Power loss investigation in HVDC for cascaded H-bridge multilevel inverters (CHB-MLI)," 2015 IEEE Eindhoven PowerTech, PowerTech 2015, vol. 2, no. 6, pp. 230-238, 2015.

- [25] B. Alamri and M. Darwish, "Precise modelling of switching and conduction losses in cascaded h-bridge multilevel inverters," *Proc. Univ. Power Eng. Conf.*, 2014.

- [26] Z. Boussada, O. Elbeji and M. Benhamed, "Different topologies and control techniques of multi level inverter: A literature survey," 2017 GECS, Hammamet, pp. 1-5, 2017.

#### **BIBLIOGRAPHY OF AUTHORS**

**Mr. Janiga Srinivasrao** completed his Bachelors and Masters in Electrical Engineering from JNTU, Hyderabad. Presently he is a research scholar at KLEF, Guntur, India and working as Assistant Professor at Anurag Engineering College, Kodad, India. His areas of interests include Multilevel converters and Electrical Machines.

**Dr. Suresh Kumar Tummala**, SMIEEE completed his Ph.D from JNTUA, INDIA. Presently he is working as Professor of Electrical Engineering Department at GRIET, Hydarabad. His areas of interests includes Power Electronics, Drives, Renewable Energy & Materials, Power System Reliability and Electrical Machines. To credit he has 22 Scopus Indexed publication and attended 14 International Conference with h-index of 8. Reviewer for IET Electric Power Applications & IEEE Transactions on Power Delivery Journals and various international conferences.

**Dr. Kuthuri Narasimha Raju**, has done his B.Tech from Sri Venkateswara Hindu college of Engineering, Machlipatnam in Electrical and Electronics Engineering in 2002, M.Tech in Power Electronics and Industrial Drives from JNTUH in 2012 and PhD from K L Deemed University in 2018. He has 17 years of teaching experience. Presently working as Professor of EEE Department and Associate Dean IQAC (Internal Quality Assurance Cell) at KL deemed University. He was the former Head of the Department. He has published 20 Scopus indexed journals and presented papers in 10 international conferences including, TENCON 2015 at Macau China. His research interests include PWM techniques for Switched mode converters, Novel Multilevel inverter topologies, DC-Microgrid and Algorithms for determination of SOC, SOH and SOL for Energy storage devices used in Electric Vehicles and power systems. Presently he is guiding 8 Research Scholars and has successfully supervised 8 PG thesis. He has been presented with Uttam Acharya Award for the year 2019 by Indian servers and received Best teacher award for Academic years 2012-13 and 2016-17 at KL Deemed University.