# Design and implementation of HDL remote controller for smart home system

I. H. Hamzah<sup>1</sup>, M. S. Z. Suhaimi<sup>2</sup>, A. A. Malik<sup>3</sup>, A. F. A. Rahim<sup>4</sup>

<sup>1,2,4</sup>Faculty of Electrical Engineering, Universiti Teknologi MARA, Malaysia <sup>3</sup>School of Engineering, Penang Skills Development Centre, Malaysia

# Article Info ABSTRACT

# Article history:

Received Feb 2, 2020 Revised Apr 3, 2020 Accepted Apr 17, 2020

#### Keywords:

Altera DE2-115 FPGA HDL Remote controller Verilog This work presents a design and development of a remote controller application using an Altera DE2-115 board. A remote controller lighting provides smart technologies make it viable to monitor, control and support users in which can enhance the quality life and promote independent living. Nowadays, to turn on the electrical devices, a user will go to the located switch. It is difficult and required more time to switch on the devices instead of staying at certain location while controlling the switching mode of the devices. Implementing this system, users do not need to have numerous switches in their home to turn on the lights as they can do this digitally from a switchless control located in one place or using a remote controller. The Altera board is built with eighteen slide switches which act as inputs and at the same time it will display the outputs on seven segments, LEDs and LCD display character. As a conclusion, the remote controller lighting system provides convenience and energy efficiency in order to allow the users to control the lighting system using smart devices.

> Copyright © 2020 Institute of Advanced Engineering and Science. All rights reserved.

# **Corresponding Author:**

Irni Hamiza Hamzah, Faculty of Electrical Engineering, Universiti Teknologi MARA, Cawangan Pulau Pinang, 13500, Permatang Pauh, Malaysia. Email: irnihami@uitm.edu.my

# 1. INTRODUCTION

Home automation system provides safety, convenience and energy efficient by allowing users or home owners to use the smart devices in order to control the electronic home appliances. In fact, every person needs a safety secure and having a comfortable life at home [1]. Thus, a smart home will ease the users with the helping of internet-connected devices to enable the remote monitoring and controlling the appliances and systems such as lighting and heating [2, 3]. An automatic controlling technology, communication technology and lighting power adjustment technology is the essence of most current intelligent lighting control system [4]. Commonly, lighting control system is applied into a house or building for the purpose to reduce the energy used and electricity bill. Six aspects that are mainly covered by the current digital home application are security monitoring, residence monitoring, health care, information appliances, central control system and energy saving [5]. Remote control and monitoring of machines is the key area of research these days [6].

Smart home is a combination of various subsystems linked to home life by advanced technologies such as fiber optic composite cable home [7]. According to Robles and Kim, Smart Home is the term for determining residence using the control system to integrate home automation system which integrating electronic devices controller with only a few buttons that are connected with the simple telecommunications system [5, 8]. Smart home can also be referred to as integrated buildings with installed detection and control devices such as heating and air conditioning, ventilation, lighting, hardware and security system [9].

For disabled and elderly person, home automation can be the substitute of institutional care [10]. With the energy saving concept, home automation or building automation makes life very simple nowadays [11]. It involves automatic controlling of all electrical or electronic devices in homes or even remotely control through wireless communication [12]. According to Balta-Ozkan, a smart home does not only provide benefits of efficient energy conservation, but also improves lifestyles, safety and security [13, 14]. Therefore, the objective on this project is to design, verify and implement remote controller lighting system for the application in smart home and FPGA is used in this project due to it is low cost, flexible, low power consumption and scalable [15-17].

FPGAs are a semiconductor device called "logic blocks" that includes programmable logic components and programmable interconnections [18]. The feature of fundamental logic gates like AND and XOR can be programmed for logic blocks or for more complex combination functions such as decoders or simple mathematical functions [19]. The general FPGA architecture consists of three types of modules. They are I/O blocks or Pads, Switch Matrix/ Interconnection Wires and Configurable logic blocks (CLB). The basic FPGA architecture has two dimensional arrays of logic blocks with a means for a user to arrange the interconnection between the logic blocks [20]. It also surrounded by programmable input/output (I/O) blocks which has been the interfaces to the external connections of the device [21]. One of the benefits of the FPGA in comparison to others is hardware resources in FPGA can be custom designed owned by users, which means that the user can design their personal circuit or processor structure, either a simple or complex [22]. The number of control and monitoring devices attached to the FPGA depend on the number of free input/output ports available on the FPGA [23]. FPGA is an excellent alternative design platform in the implementation of digital systems due to their ability to quickly process parallel hardware designs with minimal cost [24].

The paper is organized with the detail on the research method, software and hardware used in Section 2. Section 3 discussed on the detail on results and analysis of testbench timing diagram and Altera DE2-115 hardware implementation and end with conclusion on the whole objective of the project in Section 4.

## 2. RESEARCH METHOD

Quartus II 15.0 software is a tool that will be used to design a remote controller, the ISE Simulator software was used for the simulation on the timing diagram and for the hardware part, the Altera DE2-115 board was implemented. The Quartus II 15.0 Web Edition software and ISE Simulator software were used to write a Verilog HDL language and verified the functionality of the design. The seventeen slide switches have been used as an input while for the output in this system, the result will be displayed by seven segment, LEDs and LCD display. The overall flows for the remote controller design as shown in Figure 1. Verilog HDL will be used as programming code in this system in order to download the code into the Altera board to produces the expected outputs.

Figure 1. Overall flows for the remote controller lighting system design

## 2.1. Software and hardware

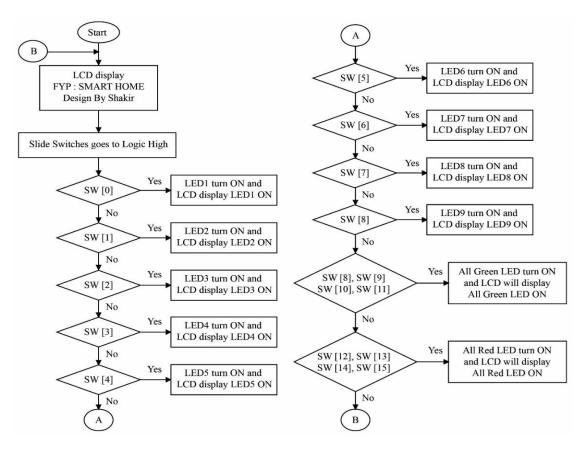

The graphical user interface and command-line interface for Quartus II 15.0 web edition software is as shown in Figure 2. Figure 3 shows the Altera DE2-115 board in which the verification process for the whole project was done. ISE simulator software for simulation is as shown in Figure 4. The whole process and flow for the remote controller lighting system is shown in Figure 5.

ISSN: 2502-4752

Figure 2. Quartus II 15.0 software environment

Figure 3. Altera DE2-115 board

| Name           | Value   | 0 ns            | 200 ns          | 400 ns          | 600 ns          | 800 ns          | 1,000 ns   |  |  |  |

|----------------|---------|-----------------|-----------------|-----------------|-----------------|-----------------|------------|--|--|--|

| 🕨 📷 SW[17:0]   | 0       | 0 1             | 2 4             | 8 16            | 32 64           | 128 256         | 3840 61440 |  |  |  |

| IED_GREEN[8:0] | 0       | 0 / 3           | 12 48           | 192             | 0               |                 | 255 0      |  |  |  |

| IED_RED[17:0]  | 0       |                 | 0               | 7               | 56 448          | 3584 28672      | 0 8191     |  |  |  |

| 🕨 駴 HEX3[6:0]  | 1000111 | (               |                 | 1000111         |                 |                 | 0001000    |  |  |  |

| ▶ 🔣 HEX2[6:0]  | 0000100 | (               |                 | 0000100         |                 |                 | 1000111    |  |  |  |

| 🕨 駴 HEX1[6:0]  | 0100001 | (               |                 | 0100001         |                 |                 | 1000111    |  |  |  |

| 🕨 😽 HEX0[6:0]  | 1110111 | 1110111 1111001 | 0100100 0110000 | 0011001 0010010 | 0000010 1111000 | 0000000 0011000 | 1110111    |  |  |  |

| 🕨 😽 HEX6[6:0]  | 1000000 | 1000000         |                 |                 | 1110111         |                 |            |  |  |  |

| ▶ 🔣 HEX5[6:0]  | 0001110 | 0001110         |                 |                 | 1000000         |                 |            |  |  |  |

| 🕨 駴 HEX4[6:0]  | 0001110 | 0001110         |                 |                 | 1001000         |                 |            |  |  |  |

| 🕨 😽 HEX7[6:0]  | 1110111 |                 |                 | 111             | 0111            |                 |            |  |  |  |

|                |         |                 |                 |                 |                 |                 |            |  |  |  |

Figure 4. Timing diagram for slide switches, LEDs and seven segment

Design and implementation of HDL remote controller for smart home system s (I. H. Hamzah)

119

# 3. RESULTS AND ANALYSIS

The results and analysis were presented in the form of timing diagram simulation and hardware implementation. Timing diagram simulation was done using ISE simulator and thus verified by hardware implementation using Altera DE2-115 board.

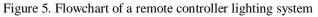

## 3.1. Testbench timing diagram

The testbench for slide switches, seven segments and LEDs that have been created before obtaining the timing diagram. In this testbench, all the inputs and outputs have been declared including UUT which is known as Unit Under Test [25]. This UUT needs to be instantiate in designing a testbench. This UUT acts as port mapping method which shows the connections of outputs and inputs from the main operation of Verilog coding that must be linked in the testbench module. Figure 6 explains the operation of switchless lighting system in test bench timing diagram.

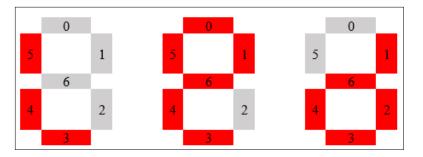

Seven segments 1, 2 and 3 were always displayed character 'Led' between 0 to 1000ns. Those seven segments are indicated with white signal colour as shown in this timing diagram. Seven segment 3 will display character 'L' while seven segment 2 display 'e' and the seven segment 1 will display 'd'. For example, the binary number for seven segment 3 is 7'b1000111 that display character 'L'. These seven segments were produced the outputs once those binary number are in logic low. Each segment in a display is identified by an index from 0 to 6 as shown in Figure 7. In order to display character 'L', the index 3, 4 and 5 are set as logic low.

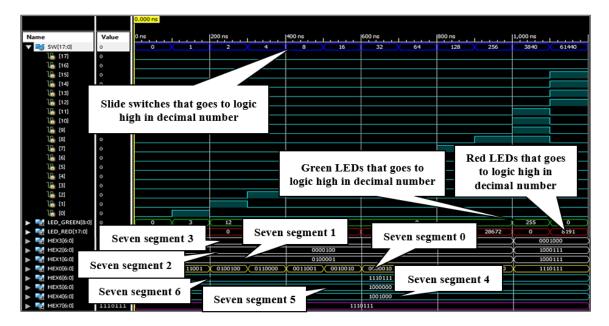

Figure 8 describes a timing diagram between input slide switches and LCD output character. At the beginning of this operation, the LCD output character will display 'FYP: SMART HOME' on the first line of the LCD while on the second line, it will display 'Design by Shakir'. These characters are displayed when there is no logic high towards the slide switch. Besides that, each line consists of 16 character that can be display according to the index input as shown in Table 1. The characters are displayed based on the hex value that have been shown earlier in Table 2. The hex value consists of low and high hex digit that need to be include with DDRAM address to display a certain character.

Figure 9 shows the result of LCD output character that display 'LED1 Will Turned On' once the first slide switch was at active high which is SW [0]. It was clearly seen through the white signal colour of hex1 which represented as the slide switch. On the white signal colour, it showed that the slide switch of SW [1] until SW [17] are at active low while the SW [0] is at active high. In a binary form, the timing diagram displayed 0000000000000000001 due to the number of bits that the slide switch required. The LCD output character showed the result according to the hex value that had been set. The hex value was determined on the green signal colour but need to be converted in hexadecimal number due to the binary form that have been set in this timing diagram. The hex value in a binary form can be obtained through the light blue box as shown in Figure 9.

Figure 6. Operation of switchless lighting system in timing diagram

2

3

4 5

6

7

SP

0

@

Ś

р

1

A Q

a

q

#

3 C S

с

s

2

В

R

b

r

\$

4 D T

d

t

% 5

E U

e

u

Figure 7. Seven segments of character 'led'

|          | Table 1. 2-Line by 16 character display |               |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|----------|-----------------------------------------|---------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| LCD Line |                                         | DDRAM address |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Line1    | 00                                      | 01            | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

| Line2    | 10                                      | 11            | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1C | 1D | 1E | 1F |

| Table 2. ASCII Hex table |                        |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

|--------------------------|------------------------|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|

|                          | Hex Value              |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| High Hex                 | High Hex Low Hex Digit |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| Digit                    | 0                      | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | `9 | Α | В | С | D | Е | F |

7

G

W

g

w

(

8

Н

X h

х

)

9

Ι

Y

i

v

+

;

Ŕ

[

k

{

J Z

j

z

,

<

L

1

=

Μ

]

m

}

· > N ^

n

~

?

0

\_ 0

DEL

&

6

F

V

f

v

| Name           | Value   | 0 ns  |       |     | 100 n | s     |        |    | 200 r | IS<br>I |       |       | 300        | ns   | 1.   |      | 400 | ns   |      |      |    | 500 | ns   |      |            | ,  | 600 ns |

|----------------|---------|-------|-------|-----|-------|-------|--------|----|-------|---------|-------|-------|------------|------|------|------|-----|------|------|------|----|-----|------|------|------------|----|--------|

| ▶ 📷 index[4:0] | 00      | 00/01 | 02/03 | 04  | 05)(0 | 6)(0) | 7)(08) | 09 | 0a)(  | )b)(00  | :)(Od | )(0e) | Of)        | (10) | 11/1 | 2/13 | 14  | (15) | (16) | (17) | 18 | 19) | (1a) | (1b) | 1c)(       | 1d | 1e/ 11 |

| ▶ 黬 hex1[17:0] | 0000000 |       |       |     |       |       |        |    |       |         | 00    | 0000  | 000        | 0000 | 0000 | )    |     |      |      |      |    |     |      |      |            |    | X      |

| 🔻 🔣 out[7:0]   |         | F     | YP    | x:k | S     | M X A | R      | T  |       | н       | ) (M  | )E    | $\bigcirc$ | D    | e (s | ; (i | g   | n    |      | B    | У  |     | S    | h    | <u>a (</u> | k  | ir     |

| 16 [7]         | 0       |       |       |     |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| 16             | 0       |       |       | ப   |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| [5]            | 1       |       |       |     |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| [4]            | 0       |       |       |     |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| Ца [3]         | 0       |       |       |     |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| [2]            | 0       |       |       |     |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| ີ 🔓 [1]        | 0       |       |       |     |       |       |        |    |       |         |       |       |            |      |      |      |     |      |      |      |    |     |      |      |            |    |        |

| 16 [0]         | 0       |       |       |     |       |       |        |    |       |         |       |       |            | Г    |      |      |     | 1    |      | - 1  |    |     |      |      |            |    |        |

| Name               | Value  700 ns  800 ns  900 ns  1,000 ns  1,000 ns  1,100 ns  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1,200 ns     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 🕨 📷 index[4:0]     | 07 \01\02\03\04\05\06\07\08\09\0a\0b\0c\0d\0e\0f\10\11\12\13\14\15\16\17\18\19\1a\1b\                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1c/1d/1e/ 1f |

| 🕨 🔜 hex1[17:0]     | 000000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X            |

| 🔻 式 out[7:0]       | z (L E D)1/W1/Tu/r/n/e/d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 n          |

| U <sub>0</sub> [7] | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

| 16                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| 16 [5]             | • Hex value in <b>Hex value in Hex value in He</b> |              |

| Line [4]           | • binary form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| 16 [3]             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| 16 [2]             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| L. [1]             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| ٥]                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

## 3.2. Altera DE2-115 hardware implementation

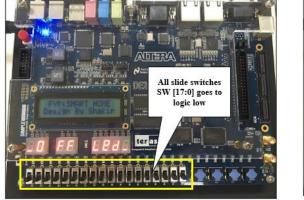

The testbench timing diagram as shown in Figure 8 is reflected in Figure 10. Figure 10 shows the result when no logic high were applied to the slide switches. At this time, no LEDs turn on but the LCD display characters of 'FYP: SMART HOME' on the first line and 'Design By Shakir' on the second line. Then, the seven segments produced an output which notify the user that the LEDs are in Off mode. It used all the seven segments that has built in the Altera board to display '\_OFF LED\_'.

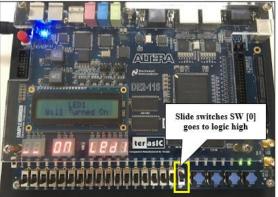

The testbench timing diagram as shown in Figure 9 is reflected in Figure 11. In this case, the LCD will be changed to display 'LED1 Will Turned On' once the SW [0] is active high. Another outputs will be produced which is the seven segments will show '\_\_ ON LED1' and the first two of green LEDs will turns on which are LED\_GREEN [0] and LED\_GREEN [1].

Figure 10. All LEDs are in off mode

Figure 11. LED1 turned on

## 4. CONCLUSION

As a conclusion, the remote controller lighting system has successfully implemented into the Altera DE2-115 board using Verilog HDL code as its design entry in Quartus software. The timing diagram have been obtained through the testbench module which is designed using ISE simulator in order to verify the functionality of the system design. Furthermore, slide switches have been used as the input for the Altera board while the 16x2 LCD module will display a character according to the inputs that are selected. Therefore, the implementation on this project will improve the user's quality life and promote independent living style.

Moreover, users do not need to have numerous switches in their home to switch on the lights as they can do this digitally from a switchless control located in one place or by using a remote controller. It means that, users just need to key in a certain number, and if the number matches the pre - setting codes in the programming code for certain light, it will turn on. The remote controller lighting system also provides convenience and energy efficiency allowing the users to control the lighting system using a smart device. Thus, electricity bill can also be reduced with the help of this remote controller system.

#### ACKNOWLEDGEMENTS

This work is sponsored by the Ministry of Higher Education (MOHE) fund from Fundamental Research Grant Scheme (FRGS) with reference no FRGS/1/2018/TK0 4/UiTM/02/35 and Universiti Teknologi MARA (UiTM) Cawangan Pulau Pinang with filing no 600-IRMI/FRGS 5/3 (156/2019). The financial support is gratefully appreciated.

#### REFERENCES

- P. Kumar and U. C. Pati, "IoT Based Monitoring and Control of Appliances for Smart Home," IEEE 2016 Inf. Commun. Technol. Recent Trends Inf. Technol. Conf. Proc., vol. 769008, pp. 1145–1150, 2016.

- [2] S. M. Shaheed, M. S. Bin Ilyas, J. A. Sheikh, and J. Ahamed, "Effective Smart Home System Based on Flexible Cost in Pakistan," *ITT 2017 - Inf. Technol. Trends Explor. Curr. Trends Inf. Technol. Conf. Proc.*, vol. 2018, pp. 35–38, 2018.

- [3] Charlie Wilson, Tom Hargreaves, and Richard Hauxwell-Baldwin, "Benefits and risks of smart home technologies," *Energy Policy*, vol. 103, pp. 72-83, 2017.

- [4] J. Wang and W. R. Chen, "Research and Design of Intelligent Lighting Control System Based on Industrial Wireless Technology," *Key Eng. Mater.*, vol. 467, pp. 620–624, 2011.

- [5] R. J. Robles, and T. Kim, "Applications, systems and methods in smart home technology: a review," Int. J. Adv. Sci. Technol., vol. 15, pp. 37-48, 2010.

- [6] A. Alheraish, W. Alomar, and M. Abu-Al-Ela, "Programmable logic controller system for controlling and monitoring home application using mobile network," *Conf. Rec. - IEEE Instrum. Meas. Technol. Conf.*, pp. 469–472, 2006.

- [7] M. Li et al., "Smart Home : Architecture, Technologies and Systems," *Procedia Comput. Sci.*, vol. 131, pp. 393–400, 2018.

- [8] A. Adriansyah and A. W. Dani, "Design of small smart home system based on arduino," Proc. 2014 Electr. Power, Electron. Commun. Control Informatics Semin. EECCIS 2014. conjunction with 1st Jt. Conf. UB-UTHM, no. August 2014, pp. 121–125, 2014.

- [9] Chee-Pun. Ooi, Wooi-Haw. Tan, Soon-Nyean. Cheong, Yee-Lien. Lee, V. M. Baskaran, Yeong-Liang. Low, "FPGA-based embedded architecture for IoT home automation application," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 14, no. 2, pp. 646-652, 2019.

- [10] Sumit Majumder, Emad Aghayi, Moein Noferesti, Hamidreza Memarzadeh-Tehran, Tapas Mondal, Zhibo Pang, and M. Jamal Deen, "Smart Homes for Elderly Healthcare—Recent Advances and Research Challenges," *Sensors* (*Basel*), vol. 17, no. 11, pp. 1-32, 2017.

- [11] Christian Reinisch, MarioJ Kofler, Félix Iglesias, and Wolfgang Kastner, "ThinkHome Energy Efficiency in Future Smart Homes," *EURASIP Journal on Embedded Systems*, vol. 2011, no. 1, p. 104617, 2011.

- [12] M. Naing and N. N. S. Hlaing, "Arduino Based Smart Home Automation System," Int. J. Trend Sci. Res. Dev., vol. 3, no. 4, pp. 276–280, 2019.

- [13] A. Bhati, M. Hansen, and C. M. Chan, "Energy conservation through smart homes in a smart city: A lesson for Singapore households," *Energy Policy*, vol. 104, pp. 230–239, 2017.

- [14] N. Balta-Ozkan, R. Davidson, M. Bicket, L. Whitmarsh, "Social barriers to the adoption of smart homes," *Energy Policy*, vol. 63, pp. 363-374, 2013.

- [15] Yang, H., Zhang, J., Sun, J., and Yu, L, "Review of advanced FPGA architectures and technologies," J. Electron. (China), vol. 31, pp. 371–393, 2014.

- [16] E. Ahmed and J. Rose, "The effect of LUT and cluster size on deep-submicron FPGA performance and density. IEEE Transactions on Very Large-Scale Integration (VLSI) Systems," vol. 12, no. 3, pp. 288–298, 2004.

- [17] Ow Hui Nee, Muataz H. Salih, Chin Beng Lim, "Design and implementation of laser based intelligent embedded dual modes cruise control system using FPGA," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 13, no. 3, pp. 2014-1021, 2019.

- [18] H. R. Radi, W. W. K. Caleb, M. N. S. Zainudin, and M. M. Ismail, "The Design and Implementation of VGA Controller on FPGA," Int. J. Electr. Comput. Sci. IJECS-IJENS, vol. 12, no. 5, 2012.

- [19] A. D. E. Board, "FPGA-based Implementation of Digital Logic Design using," Int. J. Comput. Sci. Netw. Secur. IJCSNS 2009, vol. 9, no. 8, pp. 186–194, 2009.

- [20] U. Farooq, Z. Marrakchi, and H. Mehrez, "Tree-based heterogeneous FPGA architectures: Application specific exploration and optimization," *Springer Science & Business Media*, 2012.

- [21] I. Kuon, R. Tessier, and J. Rose, "FPGA architecture: Survey and challenges," Found. Trends Electron. Des. Autom., vol. 2, no. 2, pp. 135–253, 2007.

- [22] S. Sharma and R. Deokar, "FPGA Based Cost Effective Smart Home Systems," 2018 Int. Conf. Adv. Commun. Comput. Technol. ICACCT 2018, pp. 397–402, 2018.

- [23] K. N. Sweatha, M. Poornima, and M. H. Vinutha, "Advance Home Automation Using Fpga Controller," Int. J. Adv. Res. Comput. Commun. Eng. IJARCCE 2013, vol. 2, no. 7, pp. 2680–2682, 2013.

- [24] R. K. Mohammed, H. A. Abdullah, "Implementation of digital and analog modulation systems using FPGA," Indonesian Journal of Electrical Engineering and Computer Science (IJEECS), vol. 18, no.1, pp. 485-493, 2020.

- [25] Diego F. Larios, Julio Barbancho, Félix Biscarri, and Iñigo Monedero, "A Research Study for the Design of a Portable and Configurable Ground Test System for the A400M Aircraft," *International Journal of Aerospace Engineering*, vol. 2019, 5167575, 2019.

#### **BIOGRAPHIES OF AUTHORS**

**Irni Hamiza Hamzah** was born in Machang, Kelantan on 6th December 1974. She obtained her B. Eng (Hons) in Electrical and Electronic Engineering in 1998, MSc. Electronics System and Design Engineering in 2005 and PhD in BioMEMs Sensors in 2013, which all had been obtained from School of of Electrical and Electronic Engineering, Universiti Sains Malaysia, Malaysia. She is currently a Senior Lecturer in Electronic Engineering Department, Faculty of Electrical Engineering, Universiti Teknologi MARA, Penang Branch Campus, Malaysia. Her research interests include Biosensors, BioMEMs, Neural Networks and Renewable Energy. She is a registered Board of Engineers Malaysia (BEM) Professional Engineer.

**Muhammad Shakir Zufayri Suhaimi** was born in Kuala Lumpur on 7<sup>th</sup> October 1996. He obtained his Diploma in Electrical Engineering (Electronic) in 2015. He will be graduated in February 2020 majoring B. Eng (Hons) in Electrical and Electronic Engineering for the specialization in Electronic Engineering discipline. His Final Year Project focused on the design, development and verification on the remote controller for smart home application-based using Verilog Hardware Description Language (HDL). His current research interests include software development which involved machine language and HDL, hardware troubleshooting and debugging.

**Azman Ab Malik Azman Ab Malik** was born in Melaka on 12 October 2018. He obtained his Diploma in Electronic Technology from KKTM Pasir Mas in 2007, Bachelor in Electrical Engineering and Technology from UNIKL BMI, Master in Electrical and Electronic Engineering from USM and Phd in Electrical Engineering from UITM. His interest in innovation towards electrical and electronic and cross multi-disciplinary area to identify a new model or method in engineering. His research interest include electrical power, power system, renewable energy, hybrid system, embedded system, wireless power transfer and energy storage. He is currently a Senior Lecturer in School of Engineering, Penang Skill Development Centre, Pulau Pinang, Malaysia.

Alhan Farhanah Abd Rahim obtained her B. Eng Hons in Electronics Engineering from University of Southampton in 1998, MSc and PhD in Solid State Physics from Universiti Sains Malaysia in 2003 and 2014 respectively. She is currently senior lecturer at the Faculty of Electrical Engineering, Universiti Teknologi MARA, Malaysia. Her research interests are in synthesizing and fabricating advance semiconductor materials (group IV, III-V)) and devices utilizing low cost techniques. Her PhD research work entittle: Studies of Ge nanostructures Studies of Si and Ge Nanostructures Synthesized by Electrochemical and Plasma Assisted Techniques for Sensing Applications. She is author and co-author of over 20 scientific publications in this field. She is a companion member of Institute of Engineer's Malaysia (IEM) and a registered Board of Engineers Malaysia (BEM) Professional Engineer.