### Analysis of a switching angle calculation by ANN for nine level inverter apply into experimental case study with elimination of lower and higher order harmonics

Mohammed Rasheed, Rosli Omar, Marizan Sulaiman, Wahidah Abd Halim, Moataz M.A. Alakkad Universiti Teknikal Malaysia Melaka, Faculty of Electrical Engineering, Malaysia

# Article Info ABSTRACT Article history: This paper confers an investigation of a Selective Harmonic

Received Feb 22, 2020 Revised Apr 24, 2020 Accepted May 8, 2020

#### Keywords:

ANN Digital signal processor DSP Harmonics Modified multilevel inverters

This paper confers an investigation of a Selective Harmonic Elimination (SHE) technique has gained wide acceptance for many AC drive applications, due to a higher DC bus voltage utilization (higher output voltage compared with the Sinusoidal Pulse Width Modulation (SPWM), lower harmonic distortions and easy digital realization." In recent years, the SHE technique was extensively adopted in multilevel inverters since it offers greater numbers of switching for obtaining further improvements of AC drive performances. "Nevertheless, the use of SHE-associated multilevel inverters will optimize the switching angles based on Artificial Neural Networks (ANN) compared with Particle Swarm Optimization (PSO) to reduce the Total Harmonic Distortion (THD) of the modified CHB-MLI output voltage within permissible limits. The main objectives of this paper are the design and testing of the CHB-MLI modified topology laboratory for a nine-level single-phase prototype." Also demonstrated were the experimental effects of using Digital Signal Processing (DSP) TMS320F2812 into a prototype. The controls were applied to the modified multilevel inverter, based on ANN and PSO. The proposed controller was then coded onto a board of DSP TMS320F2812. Compared with the PSO method, the inverter gives fewer THD using ANN scheme

Copyright © 2020 Institute of Advanced Engineering and Science. All rights reserved.

#### **Corresponding Author:**

Mohammed Rasheed, Universiti Teknikal Malaysia Melaka, Faculty of Electrical Engineering, Industrial Power, 76100 Hang Tuah Jaya, Durian Tunggal, Melaka, Malaysia. Email: rasheed@utem.edu.my

#### 1. INTRODUCTION

The Multilevel inverter can be reducing the switching angle and cost for components. The control strategy technique applies in multilevel inverter have been optimized the switching angle based on Artificial Neural Network (ANN), Particle Swarm Optimization (PSO) and Genetic Algorithm (GA) in order to reduce total harmonic distortion (THD) with high quality system [1-5]. The voltage source inverter discussed above restricts the output voltage to two stages, i.e. (+ V dc)/2 and (-V dc)/2, so that it is considered a two-level inverter. Due to the limited voltage blocking capacity of the power switching devices, two-level inverters present certain disadvantages, especially for high-power medium voltage applications. Additionally, in the two-level inverter, the rate of change in output voltage creates substantially higher stress on the switching devices. The most frequent approach to this downside is the use of multilevel inverters where many power switches are attached in series. Many attractive features can be provided by using multilevel inverters such as higher voltage power, lower dvdt, smaller filter or even no output filter, and better output voltage waveform quality with lower THD compared to a two-level output.

For certain cases, multi-level usage offers a transformer-less solution, reducing power loss, which is an essential requirement particularly for high-power applications. Because of its advantages the literature has suggested many topologies of multilevel inverters. The most popular types of multilevel inverters, however, are: Diode Clamped or Neutral point clamped multilevel inverters; Capacitor clamped or flying multilevel inverters; Cascaded multilevel H-bridge inverters [3-10]. The topologies of multilevel inverters above, the neutral point topology utilizes diodes, while the flying capacitor topologies utilizes capacitors for clamping the voltage levels. These topologies have a major drawback known as imbalance capacitors voltages (i.e. voltages of capacitors C1 and C2) due to inappropriate switching states of voltage vectors. Moreover, the flying capacitor type requires a starting procedure to charge up the clamping capacitors at appropriate voltage level. Among these three topologies, the Cascaded H-Bridge type is configured into modular unit with series connection to avoid balancing problem. However, the major problem with this type is that the requirement of complex transformer to provide isolated DC voltage supply for each H-Bridge Inverter circuit as present in [11-14].

A three-phase voltage source inverter (VSI) is an energy converter which is widely used in many electrical drive systems for changing a DC voltage to desired AC voltages. For example, the applications of inverter are adjustable speed motor drive, uninterruptible power supplies (UPS), grid-connected system, high voltage direct current (HVDC) power transmission and etc. In general, the inverter can be classified into two categories which are voltage source inverter (VSI) and current source inverter (CSI) was implemented in [15-17]. A 7-level inverter was simulated to minimize total harmonic distortion (THD) through the implementation of PWM technique. Therefore, there will be an increase for high voltage inverters with decrees number of gate drivers in the circuit as present in [18-20].

This paper has been verified the advantage of multilevel inverter in producing lower harmonic distortion of output voltage and current, via experimental results. The switching angle for nine-levels embedded in DSP TMS320F2812 has been designed to modified CHB-MLIs using ANN and PSO techniques. Some of researchers implemented ANN technique in the single phase of conventional CHB-MLIs. The techniques of ANN and PSO are used to calculate the switching angles with the ability to reduce harmonics of CHB-MLI output. Finally, this paper approach is tested and verified by experimental results .

#### 2. LEVELS SWITCHING OPERATION MODES FOR MODIFIED CHB-MLIS

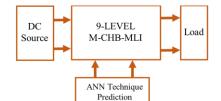

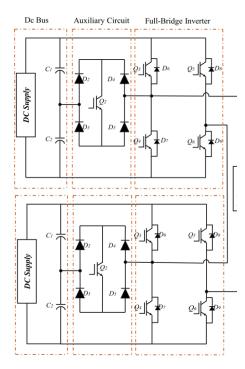

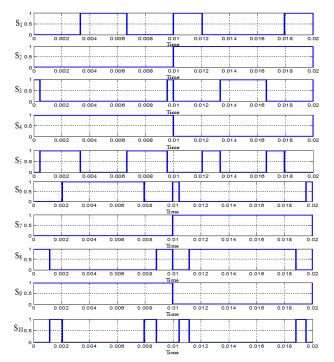

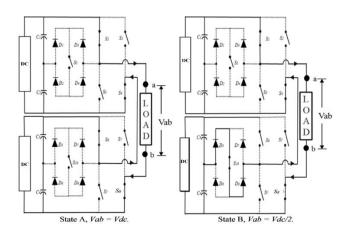

The control ANN algorithm can be applying into modified CHB-MLIs as shown the block diagram in Figure 1. The proposed CHB-MLIs modified for the nine-level operating switching model can be demonstrated in Figure 2. As previously stated, the proposed topology adopts a full-bridge configuration with an auxiliary circuit consisting of four diodes, a switch and generating half-level DC bus stress. In this timing diagram of the modified CHB-MLIs can be represent the switching pattern of each switch as shown in Figure 3. The output voltages for nine levels of modified CHB-MLIs can be summed up as described in Table 1.The solution of this work is a nine-level PWM inverter with output voltages Vdc, Vdc/2, Vdc/3, Vdc/4, zero,- Vdc/4,-Vdc/3,-Vdc/2 and-Vdc. improved output levels reduce harmonic content.

Figure 1. CHB-MLIs block diagram modified using an ANN algorithm

Table 1. Switches for nine-level output voltage On=1-Off=0 condition

| On=1-Off=0 condition |    |            |    |    |    |            |            |    |     |        |  |

|----------------------|----|------------|----|----|----|------------|------------|----|-----|--------|--|

| S1                   | S2 | <b>S</b> 3 | S4 | S5 | S6 | <b>S</b> 7 | <b>S</b> 8 | S9 | S10 | V0     |  |

| 1                    | 0  | 0          | 1  | 0  | 1  | 0          | 0          | 1  | 0   | Vdc    |  |

| 1                    | 0  | 0          | 1  | 0  | 0  | 0          | 0          | 1  | 1   | Vdc/2  |  |

| 0                    | 0  | 0          | 1  | 1  | 0  | 0          | 0          | 1  | 1   | Vdc/3  |  |

| 0                    | 0  | 0          | 1  | 1  | 0  | 0          | 1          | 1  | 0   | Vdc/4  |  |

| 0                    | 0  | 1          | 1  | 0  | 0  | 0          | 1          | 1  | 0   | 0      |  |

| 1                    | 1  | 0          | 0  | 0  | 1  | 1          | 0          | 0  | 0   | 0*     |  |

| 0                    | 1  | 0          | 0  | 1  | 1  | 1          | 0          | 0  | 0   | -Vdc/4 |  |

| 0                    | 1  | 0          | 0  | 1  | 0  | 1          | 0          | 0  | 1   | -Vdc/3 |  |

| 0                    | 1  | 1          | 0  | 0  | 0  | 1          | 0          | 0  | 1   | -Vdc/2 |  |

| 0                    | 1  | 1          | 0  | 0  | 0  | 1          | 1          | 0  | 0   | -Vdc   |  |

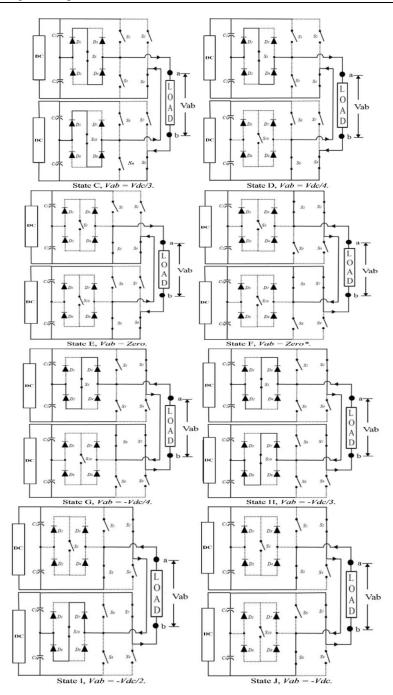

This section discussed the Modified CHB-MLI switching operation modes for topology at nine levels. The switching operation modes are in State A, B, C, D, E, F, G, H, I, and State J, as can be seen in Figure 4, State A, Figure 4, the equivalent power circuit of the proposed modified CHBMLIs to generate the Vdc output voltage level. To achieve the Vdc voltage level switches S1, S4, S6, and S9 must be in either state 1 or ON conditions. Power switches S1, S4, S9 and S10 are in State 1 to generate Vdc/2 output voltage as indicated in State B of Figure 4. S1 power switches. In Figure 4, State C shows the power circuit equivalent of the proposed modified CHBMLIs to generate the Vdc/3 output voltage level. To achieve voltage level Vdc/3, the power switch of Figure 6 S4, S5, S9, and S10 is at state 1.State D in Figure 4 shows the proposed

inverter's equivalent power circuit for generating the output voltage level Vdc/4.To achieve a Vdc/4 voltage level, the power switches S4, S5, S8, and S9 are in state 1. In Figure 4, State E shows the proposed inverter's equivalent power circuit for generating the zero level of output voltage. S3, S4, S8, and S9 are in state 1 to achieve zero level power switches. State F shows another possibility to get zero voltage level in Figure 4. To generate the zero level the power switches S1, S2, S6 and S7 are in state 1. State G in Figure 4 shows the proposed inverter's equivalent power circuit for generating the output voltage level-Vdc/4. To achieve a voltage level of -Vdc/4, the power switches S2, S5, S6, and S7 are in state 1. State H in Figure 4 shows the proposed inverter's equivalent power circuit for generating the output voltage level -Vdc/3. To achieve a voltage level of -Vdc/3, the power switches S2, S5, S7, and S10 are in state 1. In Figure 4, State I shows the proposed inverter's equivalent power circuit for generating the level of output voltage -Vdc/2. To obtain - Vdc/2 voltage level, the power switches S2, S3, S7 and S10 are at state 1. Ultimately, in Figure 4, State J shows the proposed inverter's equivalent power circuit to produce the degree of output voltage -Vdc. To achieve -Vdc voltage point, the power switches S2, S3, S7, and S8 are in state 1.

Figure 2. Proposal modified topology of a CHB-MLI, single-phase nine-level

Figure 3. Switching the modified CHB-MLIs pattern for nine-levels

Figure 4. Switching operating modes access of the modified CHB-MLIs for nine-levels

## 3. FOURIER SERIES ANALYSIS OF THE PROPOSED CHB-MLIS TOPOLOGIES FOR NINE LEVELS

The Fourier series equations for 9-levels are described below [21]:

$$f(t) = f_{\theta_1}(t) + f_{\theta_2}(t) + f_{\theta_3}(t) + f_{\theta_4}(t) = \sum_{n=1,2,5}^{\infty} \frac{2Vdc}{n\pi} (V_{dc1} \cos(1\alpha_1) + V_{dc2} \cos(3\alpha_2) + V_{dc2} \cos(5\alpha_2) + V_{dc4} \cos(7\alpha_4)) \sin(nwt)$$

(1)

Where: *Vdc:* Voltage of each voltsge source  $\theta_i$ : Switching angle From (2-1), the 5<sup>th</sup> harmonic was removed from four equation.

$$b_{n} = \frac{2V_{dc}}{\pi} \begin{cases} \cos(n\alpha_{1}) + \cos(n\alpha_{2}) + \\ \cos(n\alpha_{3}) + \cos(n\alpha_{4}) \end{cases} n = 1, 2, 3, 4$$

(2)

As shown in (2) has s variables ( $\theta_1$ ,  $\theta_2$ ,  $\theta_3$  and  $\theta_4$ ), where  $0 < \theta_1 < \theta_2 < \theta_3 < \theta_4 < \pi/2$ , and a solution set is obtained by assigning a specific value to the fundamental component, Vf, and equating s-1 harmonics to zero as given below:

$$V_{1}cos(\theta_{1}) + V_{2}cos(\theta_{2}) + V_{3}cos(\theta_{3}) + V_{4}cos(\theta_{4}) = 4m$$

$$V_{1}cos(3\theta_{1}) + V_{2}cos(3\theta_{2}) + V_{3}cos(3\theta_{3}) + V_{4}cos(3\theta_{4}) = 0$$

$$V_{1}cos(5\theta_{1}) + V_{2}cos(5\theta_{2}) + V_{3}cos(5\theta_{3}) + V_{4}cos(5\theta_{4}) = 0$$

$$V_{1}cos(7\theta_{1}) + V_{2}cos(7\theta_{2}) + V_{3}cos(7\theta_{3}) + V_{4}cos(7\theta_{4}) = 0$$

(3)

where  $m = Vf / (2Vdc / \pi)$ , and it is related to the modulation index mi by mi = m/s, where 0 < mi < 1.

An objective function is then needed for the optimisation procedure selected as a measure of effectiveness of eliminating selected order of harmonics while maintaining the fundamental component at a pre-specified value. Therefore, this objective function is defined as:

$$F(\theta_1, \theta_2, \dots, \theta_s) = \left[\sum_{n=1}^{s} V_1 \cos(\theta_n) - m\right]^2 + \left[\sum_{n=1}^{s} V_2 \cos(3\theta_n)\right]^2 + \left[\sum_{n=1}^{s} V_s \cos(2s - 1)\theta_s\right]^2$$

(4)

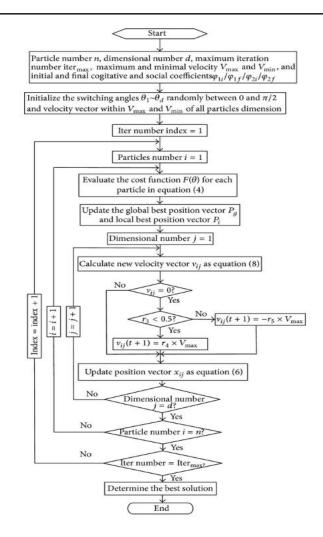

The optimal switching angles are achieved by minimizing Eq. (4) subject to the constraint  $0 < \theta_1 < \theta_2 < \theta_3 < \theta_4 < \pi/2$ , As a result it achieves the requisite harmonic profile. The primary problem is the Eq's non-linearity. (3) transcendental set, since the majority of iterative techniques with nine levels of modified CHB-MLIs can be used as shown in Figure 8.

#### 3.1. ANN performance evaluation

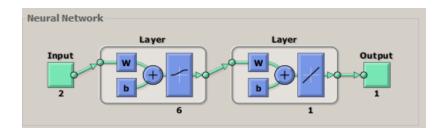

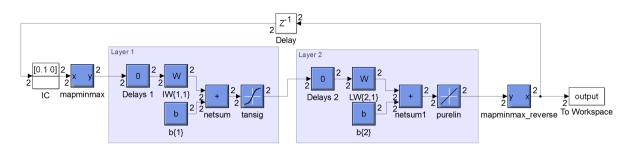

ANN is a powerful tool for controlling a very complex in nature, nonlinear structure. Use a well-designed ANN to replace the look-up table and to produce optimal switching angles in real time [22]. A standard two-layer feed-forward network shown in Figure 5 with hidden sigmoid neurons and linear output neurons will arbitrarily fit well with multidimensional mapping problems. An input layer includes n inputs and vectors P, t1 sigmoid hidden neurons in the hidden layer and t2 linear output neurons in the output layer. Figure 5 demonstrates the ANN architecture including an input layer with two inputs, a hidden layer with two hidden neurons and a two-output output layer. A Simulink Model with delayed feedback loop is created using the ANN as shown in Figure 6.

Figure 5. ANN controller block diagram

Figure 6. Simulink model for ANN-based henon map chaotic system

ANN controllers ' network structure is defined by the number of neurons in the respective input layer, hidden layer and output layer. To generate the proposed M-CHBMI switching signal, the first output layer neuron is used as the input to feed the PWM generator.

The connections weight parameter between jth and ith neuron at mth layer is given by wmij, while bias parameter of this layer at ith neuron is given by bmi. Transfer function of the network at ith neuron in mth layer is defined by:

$$n_i^m = \sum_{j=1}^{S^{m-1}} W_{ij}^m a_j^{m-1} + b_i^m$$

Neuron's output function at the mth layer is given by:

$$a_i^m = f^m \left( n_i^m \right) \tag{5}$$

Where f is neuron activation function. The activation function of the output layer is unity in this design and a tangent hyperbolic function for the hidden layer is given by:

$$f^{m}(n_{i}^{m}) = \frac{2}{1+e^{-2n_{i}^{m}}} - 1$$

(6)

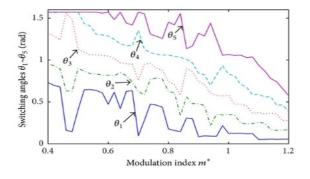

Applying ANN to the harmonic minimization problem described in the section below the procedure is shown in Figure 9. The results of the optimum switching angles are shown in Figure 7.

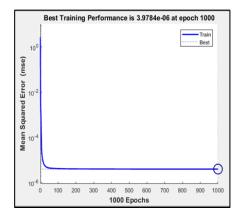

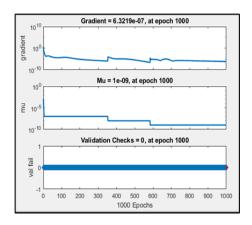

For the three training functions of the chosen architecture with 2 hidden neurons, the training outputs and training states are shown in Figure 8(a). As shown in Figure 8(b), the mean squared error for gradient below 10-7, for Mu 10-9 and validation 0 for iteration 1000 is shown. While overall performance is rising with an increasing number of secret neurons, it is difficult to predict exactly whether the performance can be increased by introducing one more neuron to the individual iteration.

Figure 7. Calculated switching angles  $\theta_1$  and  $\theta_5$  for one cell

Figure 8(a). ANN training performance with 2 hidden neurons

Figure 8(b). ANN training performance with 2 hidden neurons

Figure 9. Flow chart of ANN applying to harmonic minimization problem

#### 3.2. PSO Technique"

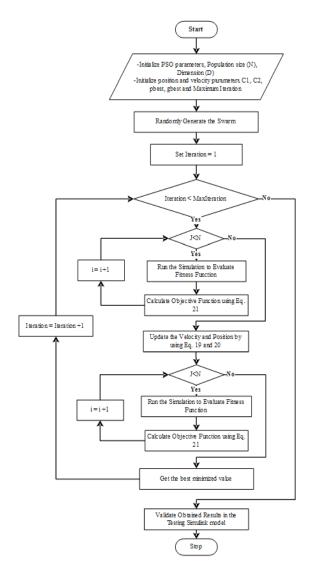

PSO has become a very popular technique for solving problems of non-linear optimization [23-26]. To optimize best switching angles, the PSO algorithm is needed to solve nonlinear SHE algorithm-based equations to resolve transcendental equations; MATLAB coding is used to solve the number of iteration algorithms to get better angles and harmonics. From PSO algorithm number of iterations.

**Step 1:** Initialize parameters of the method such as velocity vector Vi, position vector Xi, personal best particle vector Pi, particle inertia weight C0, and global best vector Pg. Assign generative values to 100, population size to 40 and cognitive parameter C1 to 0.5, as well as social parameter C2 to 1.25.

**Step 2:** Check for the case 0 < (C1+C2) < 2 and (C1+C2)/2 < C0 < 1, if the two cases are satisfied then the system will be guaranteed to coverage to a stable equilibrium point. If flase, go to step 1. **Step 3:** Update the Velocity, Vi(t+1).

$$Vij(t+1) = Vi(t) + \gamma_{1i}(Pi - xi(t)) + \gamma_{1i}(Gi - xi(t))$$

(7)

Step 4: Update the Position, Xi(t+1).

$$Xij(t+1)=Xij(t)+Vij(t+1)$$

(8)

If I is the particle index, j is the index of the parameter of interest to be improved, x is the location of the ith particle and jth parameter, k is the discrete time index, v is the velocity of the ith particle and jth parameter, P is the best position for the ith particle and jth parameter (personal best), G is the best position found by the swarm (global best), c is the random uniform number between [0,1] applied to the ith particle, u is the inertia function, a is the acceleration constant

Indonesian J Elec Eng & Comp Sci, Vol. 20, No. 2, November 2020: 948 - 959

Step 5: Now, use the Fitness function to evaluate the particle,

$$THD_V = \frac{\sqrt{\sum_{n=1}^{\infty} v_n^2}}{v_1} \tag{9}$$

For harmonic reduction elimination. For switching angles 9-level  $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$ , and  $\alpha_4$  are selected in order to selective harmonic 1<sup>st</sup>, 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup> eliminated.

$$F(1) = (\cos(\alpha_1) + \cos(\alpha_2) + \cos(\alpha_4) + \cos(\alpha_4)) - ma;$$

$$F(2) = (\cos(3 * \alpha_1) + \cos(3 * \alpha_2) + \cos(3 * \alpha_3) + \cos(3 * \alpha_4));$$

$$F(3) = (\cos(5 * \alpha_1) + \cos(5 * \alpha_2) + \cos(5 * \alpha_3) + \cos(5 * \alpha_4));$$

$$F(4) = (\cos(7 * \alpha_1) + \cos(7 * \alpha_2) + \cos(7 * \alpha_3) + \cos(7 * \alpha_4));$$

(10)

**Step 6:** Check the constraints  $0 \le \alpha_1 \le \alpha_2 \le \alpha_3 \le \alpha_4 \le \mathbb{I}/2$

**Step 7:** Check for the case P(xi) < P(Pi), if i=i+1 not satisfied then execute to Step 3.

**Step 8:** If the particle position generated is the right one, then change it by adjusting the previous location as Pi = Xi. **Step 9:** Adjust the best global position as Pg = min (neighbor to P).

**Step 10:** The most optimized switching angles. Complete the problem with solution. Figure 10 shows the general PSO flow chart of a modified CHB-MLIs, and each step is discussed below:

Figure 10. general flow chart of PSO of a modified CHB-MLIs

#### 4. EXPERIMENTAL RESULTS OF CHB-MLIS (MI=0.81) USING PSO AND ANN TECHNIQUES

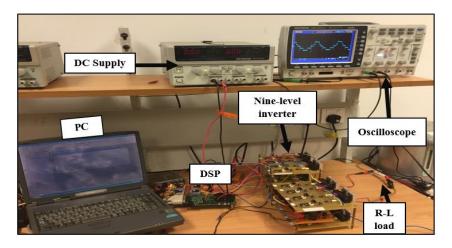

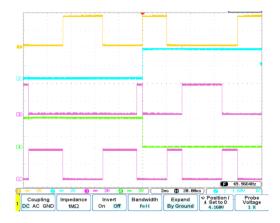

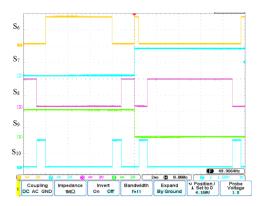

A source code for optimization using C language based on the ANN and PSO techniques has been developed to optimize the performance of a modified nine-level CHB-MLIs. Then, the source code produced was embedded in DSP-TMS320F2812. Figure 12 and Figure 13 display a timing diagram of nine-level updated CHB-MLIs. In the configuration of nine-level modified CHB-MLIs, as shown in the methodology, two cells operate.

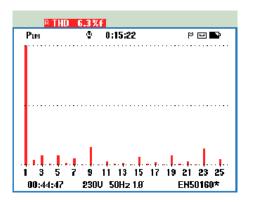

That cell consists of five switches including bi-directional switches, namely S1, S2, S3, and S4 and bi-directional switches S5. It is noted from these figures that the 10 switches have the same switching times using a switching frequency of 2500Hz. The switching angles of nine-level modified CHB-MLIs were determined using the ANN method, and the values of the switching angles obtained are equal to  $\theta_1$ =5.57,  $\theta_2$ =18.27,  $\theta_3$ =33.37, and  $\theta_4$ =51.59.

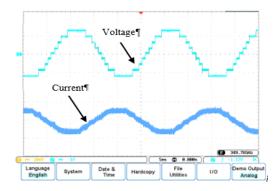

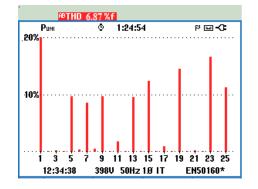

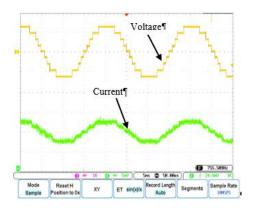

Such switching angles have been encoded into the source code and then inserted in the DSP-TMS320F2812 to produce the output of the inverter waveform. One cycle with an MI value of 0.81, has a duration of 0.02s in the programming of source code. The optimisation of the output voltage and current waveform of a nine-level modified CHB-MLI using the ANN technique was developed on the basis of the timing diagrams obtained, as shown in Figure 14. The SHE technique of the fundamental switching frequency scheme is used to eliminate the specific order harmonics of the inverter output. A modified CHB-MLI with equal DC sources is used in this research. SHE-PWM is the modulation technique used here, involving the nonlinear equations. The ANN and PSO approaches are used to achieve optimal switching angles for low-order harmonics. The output voltage harmonics of a modified CHB-MLI using ANN have been calculated as shown in Figure 15 and its THD values are equal to 9.4%.

Figure 11. Design of a single-phase modified CHB-MLI for nine-level applications

Coupling Impedance Nivert Bandvidth Expand Station/ Probe ttm2 On Or Will ByGround Station Station 1 1000 EX DC AC GAD Impedance On Or Bandvidth Expand Voltage 1 000 EXC 1 1000 EX 10

Figure 12. Timing diagram of nine levels modified CHB-MLIs for cell one comprising  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ , and  $S_5$  switches with MI=0.81 using ANN technique

Figure 13. Timing diagram of nine levels modified CHB-MLIs for cell one comprising  $S_6$ ,  $S_7$ ,  $S_8$ ,  $S_9$ , and  $S_{10}$  switches with MI=0.81 using ANN technique

Figure 14. Optimisation of nine-level modified CHB-MLIs output voltage and current waveform with MI=0.81 using ANN technique

Figure 16. Optimisation of the harmonic output current waveform spectrum of the modified CHB-MLIs with MI=0.81 using ANN technique

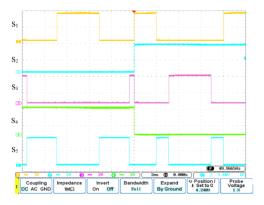

Figure 18. Timing diagram of nine levels modified CHB-MLIs for cell one comprising S<sub>6</sub>, S<sub>7</sub>, S<sub>8</sub>, S<sub>9</sub>, and S<sub>10</sub> switches with MI=0.81 using PSO technique

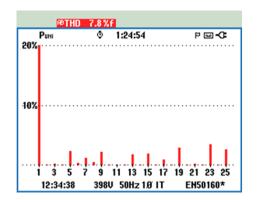

Figure 15. Optimisation of the harmonic output voltage waveform spectrum of the modified CHB-MLIs with MI=0.81 using ANN technique

Figure 17. Timing diagram of nine levels modified CHB-MLIs for cell one comprising  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ , and  $S_5$  switches with MI=0.81 using PSO technique

Figure 19. Optimisation of nine-level modified CHB-MLIs output voltage and current waveform with MI=0.81 using PSO technique

The results of the timing diagram of the modified CHB-MLIs of nine levels based on the PSO technique are presented in Figure 17 and Figure 18. The optimized angle of switching achieved is equal to  $\theta 1 = 7.23$ ,  $\theta 2 = 21.08$ ,  $\theta 3 = 35.92$ , and  $\theta 4 = 55.91$ . Figure 19 shows the optimization of a modified CHB-MLI's output voltage waveform using PSO technique. Due to the incorrect estimation of the switching angles, optimization of output voltage waveforms of a modified CHB-MLIs was smoother than optimization for the ANN technique.

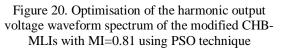

Figure 21. Optimisation of the harmonic output current waveform spectrum of the modified CHB-MLIs with MI=0.81 using PSO technique

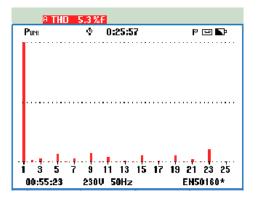

Figure 20 and Figure 21 shows the optimization of the harmonic spectrum of a modified CHB-MLI output voltage and current waveform using PSO with 7.8 % and 6.3% respectively THD values. The overall values of MI, switching angles and THD for voltage of modified CHB-MLI for nine-level based on PSO and ANN techniques are shown in Table 2. Figure 22 the excel switching angle plotting output and the voltage and current THD values based on PSO and ANN techniques.

Table 2. Overall values of MI, switching angles and THD for voltage of modified CHB-MLI for nine-levels based on PSO and ANN techniques

| bused on 150 and 71 (1) teeningues |      |      |       |       |       |             |             |  |  |  |

|------------------------------------|------|------|-------|-------|-------|-------------|-------------|--|--|--|

| Nine-Level                         | Mi   | θ1   | θ2    | θ3    | θ4    | THD phase V | THD phase I |  |  |  |

| PSO                                | 0.81 | 7.23 | 21.08 | 35.92 | 55.91 | 7.8%        | 6.3%        |  |  |  |

| ANN                                | 0.81 | 5.57 | 18.27 | 33.37 | 51.59 | 6.87%       | 5.3%        |  |  |  |

|                                    |      |      |       |       |       |             |             |  |  |  |

Figure 22. Overall values of MI, versus the switching angles and the value of THD for voltage and current of modified CHB-MLIs of 9-levels based on PSO and ANN

#### 5. CONCLUSIONS

The experimental results showed that using both methods, the higher level of the inverter it will produce lower harmonic content of modified CHB-MLIs. However, due to the switching angles of the ANN technique, ANN technique produces lower THD content of the modified CHB-MLIs output voltage waveform compared with PSO technique is simple and efficient The coding was then processed in DSP-TMS320F2812 based upon PSO and ANN techniques. However, the ANN technique produces a lower THD content of the modified CHB-MLI output voltage and current waveform compared to the PSO technique because the switching angles of the ANN technique are simple and efficient.

**D** 959

#### 6. ACKNOWLEDGMENT

This research is sponsored by the grant Penyelidikan Jangka Pendek (PJP) which the number is PJP/2019/FKE(2A)/S01668. The authors would also like to thank the Centre for Research and Innovation Management Universiti Teknikal Malaysia Melaka (CRIM-UTeM) for the funding to support this project to providing the facilities and research environment.

#### REFERENCES

- E. Babaei, M. F. Kangarlu, M. Sabahi, and M. R. A. Pahlavani, "Cascaded multilevel inverter using sub-multilevel cells," *Electr. Power Syst. Res.*, vol. 96, pp. 101–110, Mar. 2013.

- [2] H. Rashid, Power electronics: circuits, devices, and applications. Pearson/Prentice Hall, 2004.

- [3] M. Jones and I. N. W. Satiawan, "A simple multi-level space vector modulation algorithm for five-phase open-end winding drives," *Math. Comput. Simul.*, vol. 90, pp. 74–85, Apr. 2013, doi: 10.1016/j.matcom.2012.05.007.

- [4] S. K. Mondal, B. K. Bose, L. Fellow, and V. Oleschuk, "Space Vector Pulse Width Modulation of Three-Level Inverter Extending Operation Into Overmodulation Region," vol. 18, no. 2, pp. 604–611, 2003.

- [5] R. N. A. Krismadinata, H. W. Ping, and J. Selvaraj, "Elimination of Harmonics in Photovoltaic Seven-level Inverter with Newton-raphson Optimization," *Procedia Environ. Sci.*, vol. 17, pp. 519–528, 2013, doi: 10.1016/j.proenv.2013.02.067.

- [6] A. Pradesh, "Harmonic orientation of pulse width modulation," Power Eng. Electr. Eng., vol. 9, no.1, pp. 29–34, 2011.

- [7] A. Fri, R. El Bachtiri, and A. El Ghzizal, "A Comparative Study of Three Topologies of Three-phase (5L) Inverter for a PV System," *Energy Procedia*, vol. 42, pp. 436–445, 2013.

- [8] O. Abdel-Rahim, H. Abu-Rub, and A. Kouzou, "Nine-to-Three Phase Direct Matrix Converter with Model Predictive Control for Wind Generation System," *Energy Proceedia*, vol. 42, pp. 173–182, 2013, doi: 10.1016/j.egypro.2013.11.017.

- [9] B. Boost, V. Current, S. Inverter, Q. Lei, S. Member, and F. Z. Peng, "Space Vector Pulsewidth Amplitude Modulation for a," vol. 29, no. 1, pp. 266–274, 2014.

- [10] J. Sabarad and G. H. Kulkarni, "Novel switching technique for five leg inverter in dual motor control," vol. 19, no. 2, pp. 644–651, 2020.

- [11] E. Babaei, M. F. Kangarlu, and F. N. Mazgar, "Symmetric and asymmetric multilevel inverter topologies with reduced switching devices," *Electr. Power Syst. Res.*, vol. 86, pp. 122–130, May 2012, doi: 10.1016/j.epsr.2011.12.013.

- [12] R. a Ahmed and S. Mekhilef, "New multilevel inverter topology with minimum number of switches," TENCON 2010 - 2010 IEEE Reg. 10 Conf., pp. 1862–1867, Nov. 2010.

- [13] S. H. H. Ebrahim Babaei, "New multilevel inverter topology with minimum number of switches," IEEE Reg. 10 Annu. Int. Conf. Proceedings/TENCON, vol. 50, no. 11, pp. 1862–1867, 2010.

- [14] H. A. Mohamed and H. M. D. Habbi, "Power quality of dual two-level inverter fed open end winding induction motor," *Indones. J. Electr. Eng. Comput. Sci.*, vol. 18, no. 2, pp. 688–697, 2020.

- [15] S. H. Hosseini, M. F. Kangarlu, and A. K. Sadigh, "A New Topology for Multilevel Current Source Inverter with Reduced Number of Switches," *Electr. Electron. Eng. 2009. ELECO 2009. Int. Conf. on. IEEE*, pp. 273–277, 2009.

- [16] W. A. Halim and N. A. Rahim, "FPGA-based pulse-width modulation control for single-phase multilevel inverter," 2011 IEEE 1st Conf. Clean Energy Technol. CET 2011, pp. 57–62, 2011, doi: 10.1109/CET.2011.6041436.

- [17] R. G. Omar, "Modified FCS-MPC algorithm for five-leg voltage source inverter," *Indones. J. Electr. Eng. Comput. Sci.*, vol. 19, no. 1, pp. 47–57, 2020.

- [18] J. J. Nedumgatt, D. V. Kumar, A. Kirubakaran, and S. Umashankar, "A multilevel inverter with reduced number of switches," 2012 IEEE Students' Conf. Electr. Electron. Comput. Sci. Innov. Humanit. SCEECS 2012, vol. 1, 2012.

- [19] V. Sridhar and S. Umashankar, "A comprehensive review on CHB MLI based PV inverter and feasibility study of CHB MLI based PV-STATCOM," *Renew. Sustain. Energy Rev.*, vol. 78, no. March, pp. 138–156, 2017.

- [20] H. Sardar Kamil, D. M. Said, M. W. Mustafa, M. R. Miveh, and N. Ahmad, "Recent advances in phase-locked loop based synchronization methods for inverter-based renewable energy sources," *Indones. J. Electr. Eng. Comput. Sci.*, vol. 18, no. 1, p. 1, 2020.

- [21] R. Vijayakumar, "Selective Harmonic Elimination PWM Method using Seven Level Inverters by Genetic Algorithm Optimization Technique," *Int. J. Eng. Res. Technol.*, vol. 4, no. 02, pp. 812–818, 2015.

- [22] L. Zhang, "Design and Implementation of Neural Network Based Chaotic System Model for the Dynamical Control of Brain Stimulation," *Second Int. Conf. Neurosci. Cogn. Brain Inf.*, no. c, pp. 14–21, 2017.

- [23] A. K. Al-Othman and T. H. Abdelhamid, "Elimination of harmonics in multilevel inverters with non-equal dc sources using PSO," *Energy Convers. Manag.*, vol. 50, no. 3, pp. 756–764, 2009, doi: 10.1016/j.enconman.2008.09.047.

- [24] S. Sudha Letha, T. Thakur, and J. Kumar, "Harmonic elimination of a photo-voltaic based cascaded H-bridge multilevel inverter using PSO (particle swarm optimization) for induction motor drive," *Energy*, vol. 107, pp. 335–346, 2016.

- [25] V. K. Gupta and R. Mahanty, "Optimized switching scheme of cascaded H-bridge multilevel inverter using PSO," *Int. J. Electr. Power Energy Syst.*, vol. 64, pp. 699–707, 2015.

- [26] B. Alamri, A. Sallama, and M. Darwish, "Optimum SHE for Cascaded H-Bridge Multilevel Inverters Using: NR-GA-PSO, Comparative Study," pp. 1–10, 2015.