# FPGA-based embedded architecture for IoT home automation application

Chee-Pun. Ooi, Wooi-Haw. Tan, Soon-Nyean. Cheong, Yee-Lien. Lee, V. M. Baskaran, Yeong-Liang. Low

Faculty of Engineering, Multimedia University, Malaysia

| Article Info                                                                                                                         | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Article history:                                                                                                                     | An Internet of Things (IoT) FPGA-based home hub to automate control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Received Jul 27, 2018<br>Revised Nov 25, 2018<br>Accepted Jan 18, 2019                                                               | operations in a home environment was designed and built. The proposed<br>system uses an FPGA home hub as its local analytic engine with an IoT<br>platform to store the sensory data. The FPGA was programmed in Verilog<br>HDL using Quartus II provided by Altera. The WiFi capability of the FPGA<br>was extended through an ESP8266 chip to ease the interfacing with various                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Keywords:                                                                                                                            | sensors connected to it. The system can be configured and monitored through<br>a web application coded in JavaScript. Various test cases were carried out or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Embedded system<br>FPGA<br>Home automation<br>Internet of things<br>Open-source platform                                             | the implemented system at Multimedia University (MMU) Digital Home<br>Lab. The results verified the functionality of the system in triggering real<br>home appliances (i.e. air conditioning unit and lighting) based on multiple<br>sensor nodes without conflicting each other. The ability to allow user to<br>configure the control rules based on the sensory data via web interface hosted<br>using ThingSpeak Plugins is also presented and demonstrated in this project.<br>The base design is utilizing Altera Cyclone IV EP4CE22F17C6N FPGA with<br>153 I/O pins, which is highly scalable and adaptable to the requirements of<br>home environments. This shows promising application of FPGA in<br>supporting scalable IoT home automation system. |  |  |  |

|                                                                                                                                      | Copyright © 2019 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Corresponding Author:                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Ooi Chee-Pun,<br>Faculty of Engineering,<br>Multimedia University,<br>63100, Cyberjaya, Selangor, Malaysi<br>Email: cpooi@mmu.edu.my | a.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

# 1. INTRODUCTION

People are continually working towards enhancing the quality of life. As technology advances, the ambition of building a smart home with scheduled and automated home devices to create a more comfortable living environment becomes achievable. A survey conducted by TNS on behalf of Intel Corporation found that 68% of Americans believe that smart homes will be as popular as smartphones within 10 years [1], and Internet of Things (IoT) will be the core technology of these smart homes as well as smart city. [2,3,4]. IoT is an emerging technology trend in which objects such as sensors and actuators are given networking and computing capability, so that they can communicate and generate data among themselves with minimal human intervention [5]. The generated data can be analysed to provide valuable functions to the users. IHS predicts that by 2020, there will be more than 30 billion devices in the IoT market, impacting the areas of automation, integration and servitization (service-oriented business models) [6]. Currently available IoT platforms for home automation, however, are still limited [5], and the use of Field-programmable Gate Array (FPGA) is still relatively uncommon in these platforms. FPGAs have the potential to achieve higher performance than the more commonly-used embedded computers such as Raspberry Pi in many area. [7,8,9]. The FPGA chips are well-suited for home automation for they have longer lifecycle, more than 100 general-purpose input and output (GPIO) pins (e.g. 150 GPIO for cyclone IV device). This project

designs and develops an embedded architecture to take advantage of the hardware parallelism in FPGAs to serve as a local analytic engine in IoT application for home automation using Verilog Hardware Description Language (HDL) and explores the potential of FPGA in IoT applications.

# 2. RELATED WORK

Debono and Abela reported a home automation system in which FPGA was used as the central controller with a Bluetooth module, various sensors and actuators interfaced to it [10]. The controlling and monitoring was realized by using the application in the mobile phone. However, the required Bluetooth connection between the module and the phone limits the operation range of the system. Sharma et. al. reported a similar FPGA-based monitoring system [11], both of these projects are controlling the home appliances based on single sensor mode, i.e., one sensory data to trigger one home appliance, without analyzing the status of multiple sensory data.

In contrast, Chinchansure and Kulkarni developed a home automation system that interfaced with a Global System for Mobile communication (GSM) modem that allows users to communicate with the system using Short Messaging Service (SMS) [12]. Although the operation range is greater than that of the Bluetooth, every control operation invoked by users via SMS incurs charges.

Kumar and Rao developed a secure home automation system that uses an FPGA to perform encryption and decryption to the data that are transmitted wirelessly between components of the system [13]. This project highlighted the advantages of FPGA in terms of scalability, configurability and security.

Rusu and Duka proposed and implemented a system in which FPGA boards are used to connect to and control household appliances [14]. A Raspberry Pi enables communication with the FPGA and a web application which can be accessed from a computer or mobile device. The system is designed to be flexible, scalable and adaptable to various communication protocol. The inclusion of a web technology provides for control of household appliances remotely through the Internet and also control of appliances in more than one home is reported in this paper. However, the embedded ARM Cortex M0 IP core of FPGA instead of Verilog HDL is used, which might not truly reflect the advantages of the FPGA in terms of configurability and scalability.

The IoT framework proposed by Laubhan consists of multiple sensor nodes which collect data from the sensors and sends them wirelessly to a regional hub which acts as a local analytic engine [15]. Raspberry Pi 2 was used as the regional hub. On top of that, a cloud portal is used to store the data from all regional hubs, provide user accessibility, and achieve more comprehensive analytical functions. The Wireless Sensors Network (WSN) applied in this platform is crucial to allow a wide distribution of sensors without the need of physical connections to the analytic engine. A similar IoT framework is adopted in this project with the FPGA functioning as the local controller hub with embedded analytic engine developed using Verilog HDL. To reduce the cost, open source IoT data platforms, Dweet.io and ThingSpeak, were utilized to allow the users to access the system.

## 3. SYSTEM DESIGN AND IMPLEMENTATION

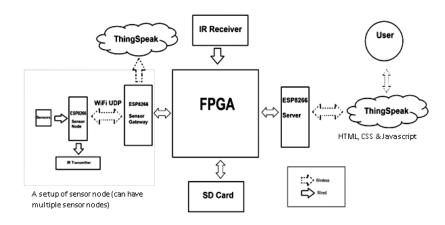

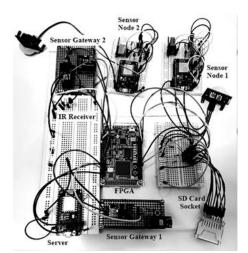

An overview block diagram of the system is shown in Figure 1. The FPGA home hub acts as a local analytic engine based on the analytic rules configured by the users via web interface. Multiple sensor nodes are employed to provide the input data to the FPGA via Verilog-HDL based UART module developed in this project. The baud rate of the serial communication is set to 115200. Based on the sensory data received by the FPGA, users can configure the analytic rules in the form of "if-else" structure for home automation. The hardware prototype of the implemented system is shown in Figures 2a and 2b. It consists of an FPGA-based analytic engine that communicates with various sensor nodes via Wi-Fi connection and a web interface. Users can combine the status of the sensory data from various sensor nodes to define the control rules via the web interface hosted in remote cloud using ThingSpeak Plugins. These user-defined control rules are stored inside a Secure Digital (SD) card. In this design, users can define up to 10 rules. The output of the system is infrared (IR) profile signals for home appliances. The IR receiver module learns the IR profiles of home appliances and stores them in the SD card. This eliminates the need to hardcode any IR profiles in the system and provides the flexibility to control various brand and model of IR controlled home appliances.

# 4. LOCAL ANALYTIC ENGINES IN FPGA HOME HUB

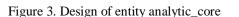

The Verilog design entity of the local analytic engines is shown in Figure 3. The number of data sets and rules are pre-defined but can easily be re-defined using parameters named as "NUM\_ESP" and "NUM\_RULES", during module instantiation as shown in Figure 4. (i.e., the parameter. NUM\_RULES is

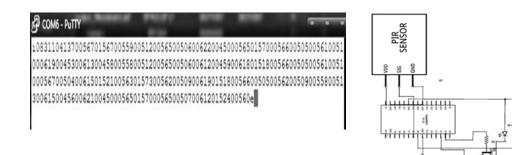

redefined to 10 instead of 2 as in Figure 3.) The rules applied on the data set are implemented using "if-else" structures defined in module "rule\_subcore", with the input values configured via web-page interface. In the operation mode, the result of entity "analytic core" will be used to match the IR profiles stored in the SD card. Then, the ESP8266-based sensor node will transmit the IR profile signal via UART transmitter for home automation tasks such as turning the air-conditioning and lighting on / off. A sample output of the UART transmitter, to trigger the LG air conditioning unit, is shown in Figure 5.

Figure 1. Overview block diagram

Figure 2a. Hardware prototype

Figure 2b. Web user interface

# 5. MULTIPLE SENSOR NODES TO FPGA HOME HUB

Two ESP-12-E-based sensor nodes and a single FPGA home hub are constructed and tested in this project. Each node consists of an ESP-12-E with sensors (i.e., temperature, humidity, and motion) and an IR transmitter, TSOP38238. This structure emulates the function of a WSN. Signals from the sensor are transmitted to the FPGA home hub wirelessly via internal home network. This demonstrates the ability of the FPGA home hub to serve as a local analytic engine for scalable distributed sensors nodes.

All the sensor signals are collected and analyzed by the FPGA home hub for immediate action, as well as being displayed on IoT dashboard for remote notification and action. The IR profiles learned and stored in the FPGA home hub's SD-Card are retrieved and transmitted via home network to the sensor nodes. The sensor nodes which contain IR transmitters then transmit the IR signal based on the received IR profile received to turn ON/OFF the home appliances. The schematic diagram of the sensor node which consist of ESP8266 by Espressif is shown in Figure 6.

module analytic\_core #( parameter NUM ESP = 2. parameter NUM\_RULES = 2 input clk, input [8\*NUM\_ESP-1:0] temperature, //unsigned 8-bit input [8\*NUM\_ESP-1:0] humidity, input [8\*NUM ESP-1:0] motion, input [47:0] conf\_data, //47:0 data for lower and upper boundary input [15\*NUM\_RULES-1:0] conf\_sel, input conf\_sig\_in, //output reg conf\_sig\_out, output [NUM\_RULES-1:0] result, input [7:0] count\_rules, output reg busy );

analytic\_core #{

.NUM\_ESP(2),

.NUM\_RULES(10)

) al(

.clk(clk),

.temperature(temperature),

.humidity(humidity),

.motion(motion),

.conf\_data(conf\_data),

.conf\_sel(conf\_sel),

.conf\_sig\_in(conf\_sig\_in),

.result(result\_rule),

.count\_rules(count\_rules),

.busy(analytic\_busy)

);

Figure 4. Module analytic core instantiation with 10 rules

Figure 5. IR profile sent from uart transmitter to trigger an Figure 6. Schematic diagram of the sensor node air conditioning unit

#### 6. PERFORMANCE RESULTS

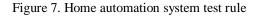

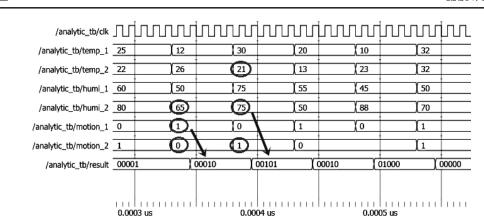

A physical field test was conducted at Digital home and lifestyle Lab in Multimedia University (MMU) to ensure the analytic rule is triggered correctly according to its configuration and subsequent pre-set action is performed according to the triggered rules. One of the rules tested is shown in Figure 7. Two parameters, room temperature (between 00C to 300C) and motion, were used in this rule in order to trigger the air conditioner unit via IR signal transmitted from sensor node 2. The test has verified the functionality of the FPGA home hub and its ability to control a home appliance (the air conditioner unit) based on the status of the sensory data and its configured rule. The functionality of the analytic core was verified using a Verilog HDL test bench. Figure 8 shows the result waveform of the test bench and Table 3 shows the comparison of expected result and the actual result obtained.

| Home Automation System Home Rules Setting IR Setting |                    |             |             |                     |

|------------------------------------------------------|--------------------|-------------|-------------|---------------------|

|                                                      | Parameter 1        | Parameter 2 | Parameter 3 | Action              |

| 1                                                    | 0≤temperature_2≤30 | None        | motion_2=1  | Send IR 2 to Unit 2 |

| 2                                                    | Deactivated        |             |             |                     |

| 3                                                    | Deactivated        |             |             |                     |

| 4                                                    | Deactivated        |             |             |                     |

| 5                                                    | Deactivated        |             |             |                     |

| 6                                                    | Deactivated        |             |             |                     |

*Fpga-based embedded architecture for IoT home automation application (Chee-Pun. Ooi)*

DHT11

Entity:analytic\_tb Architecture: Date: Tue Jan 24 16:20:13 +0900 2017 Row: 1 Page: 1

Figure 8. Result waveform of the test bench

Five rules were configured and eight sets of data with different parameters were fed into the analytic engine. Table 1 shows the list of configures rules and Table 2 shows the list of sensory data that fed into the analytic engine. The analytic core was instantiated to accommodate two sensor nodes. As highlighted in Figure 8, rule 2 ("0010") is generated when the sensory data comply with the rule no 2 as in Table 1 (i.e., humi\_2>=50, motion\_1=1, and motion\_2=0). Similarly, rule 5 ("0101") is generated when the data comply to rule 5 in Table 1 (i.e., temp\_2>=20, humi\_2>=70, and motion\_2=1). Hence, the Verilog-HDL test bench results verified the analytic engine's functionality.

Table 1. List of Configured Rules Tested in the Test Bench

| Rule<br>No. | Parameter 1        | Parameter 2                   | Parameter 3        |

|-------------|--------------------|-------------------------------|--------------------|

| 1           | 15 <= temp_1 <= 30 | 20 <= temp_2 <= 26            | motion_ $2 = 1$    |

| 2           | 50 <= humi_2 <= 70 | $motion_1 = 1$                | motion_ $2 = 0$    |

| 3           | 70 <= humi_1 <= 80 | 60 <= humi_2 <= 75            | 20 <= temp_2 <= 23 |

| 4           | motion_ $1 = 0$    | $10 \le \text{temp}_1 \le 15$ | 30 <= humi_1 <= 50 |

| 5           | 20 <= temp_2 <= 25 | 70 <= humi_2 <= 90            | $motion_2 = 1$     |

Table 2. List of Data Fed nto the Analytic\_Core in the Test Bench

|      |        |        |          | <u> </u> |        |          |

|------|--------|--------|----------|----------|--------|----------|

| Data | temp_1 | humi_1 | motion_1 | temp_2   | humi_2 | motion_2 |

| 1    | 25     | 60     | 0        | 22       | 80     | 1        |

| 2    | 12     | 50     | 1        | 26       | 65     | 0        |

| 3    | 30     | 75     | 0        | 21       | 75     | 1        |

| 4    | 20     | 55     | 1        | 13       | 50     | 0        |

| 5    | 10     | 45     | 0        | 23       | 88     | 0        |

| 6    | 32     | 50     | 1        | 32       | 70     | 1        |

| 7    | 24     | 70     | 0        | 20       | 70     | 0        |

| 8    | 28     | 65     | 1        | 21       | 60     | 1        |

Table 3. List of Data Fed into the Analytic\_Core in the Test Bench

| 1 401 | Tuble 5. Elst of Duta Ted into the Thiarytic_Core in the Test Denen |                 |                                   |  |  |

|-------|---------------------------------------------------------------------|-----------------|-----------------------------------|--|--|

| Data  | Expected Result                                                     | Obtained Result | Expected matches obtained results |  |  |

| 1     | 00001                                                               | 00001           | 1                                 |  |  |

| 2     | 00010                                                               | 00010           | 1                                 |  |  |

| 3     | 00101                                                               | 00101           | 1                                 |  |  |

| 4     | 00010                                                               | 00010           | 1                                 |  |  |

| 5     | 01000                                                               | 01000           | 1                                 |  |  |

| 6     | 00000                                                               | 00000           | 1                                 |  |  |

| 7     | 00100                                                               | 00100           | 1                                 |  |  |

| 8     | 00001                                                               | 00001           | 1                                 |  |  |

|       |                                                                     |                 |                                   |  |  |

**G** 651

#### 7. CONCLUSION

An FPGA-based home hub featuring a local analytic engine has been implemented and tested with several test cases in an actual home environment setup at Digital Home and lifestyle Lab in MMU. An Verilog-HDL Test bench results were also included to verify the functionality of the analytic core developed in this project. The FPGA home hub successfully demonstrated the ability of FPGA being used in an IoT platform and its internal architecture in handling multiple sensor nodes. This shows the potential of FPGA in handling multiple sensor nodes simultaneously without any software delay as in most sequential programming microcontroller based system. New sensor node units can be added to the system easily without conflicts. The prototype implementation of the system included two sensor nodes to demonstrate this. From that, it can be concluded that as long as the firmware code is well-written with scalability in consideration, FPGA-based design can be scaled up with minimum effort.

# ACKNOWLEDGEMENTS

The authors gratefully acknowledge the financial support and the smart home facilities at Digital Home and lifestyle Lab at Multimedia University (Cyberjaya campus) to successfully implement the project.

#### REFERENCES

- [1] Intel. (2014). "Could Smart Homes Be as Commonplace as Smartphones by 2025?". [Online]. Available: http://download.intel.com/newsroom/kits/iot/pdfs/IntelSmartHomeSurveyBackgrounder.pdf

- [2] Amine Rghioui, Abdelmajid Oumnad, "Challenges and Opportunities of Internet of things in Healthcare" IJECE, vol 8, No 5, Oct 2018, pp2753-2761.

- [3] Intel. (2015). "Introducing the Intel Smart 'Tiny House': Exploring Smart Home Technology in 210 Square Feet." [Online]. Available: http://download.intel.com/newsroom/kits/iot/pdfs/IntelTinyHomeFactSheet.pdf

- [4] Rajina R Mohamed et.al, "Provisioning of Street Lighting based on Ambience Intensity for Smart City" Vol 12, No 3, Dec 2018, pp 1401-1406.

- [5] Karen Rose, et.al., "The internet of Things (IoT): An Overview", The Internet Society, p.5, October 2015.

- [6] S. Lucero, "IoT platforms: enabling the Internet of Things", IHS Technology white paper, March 2016.

- [7] R. Brzoza-Woch, P. Nawrocki, "FPGA-Based Web Services--Infinite Potential or a Road to Nowhere?" IEEE Internet Computing, Jan 2016, 20(1), pp.44–51.

- [8] Archana Rani, Naresh Grover, "An Enhanced FPGA Based Asynchronous Microprocessor Design Using VIVADO and ISIM" Bulletin of Electrical Engineering and Informatics, Vol 7, No 2, June 2018, pp 199-208.

- [9] Shamala N, C.Lakshminarayana, "Performance Enhancement in Active Power Filter (APF) by FPGA Implementation", International Journal of Electrical and Computer Engineering, Vol 8, No 2, April 2018, pp 689-698.

- [10] C. J. Debono and K. Abela, "Implementation of a Home Automation System Through a Central FPGA Controller" in 16th IEEE MediterraneanElectrotechnical Conference (MELECON 2012), Tunisia, 2012, pp. 641–644.

- [11] S. Sharma, J. Boddu, G. S. Charan, S. Sharma, S.Sivanantham, and K.Sivasankaran, "Home Automation Through FPGA Controller", in 2015 Online International Conference on Green Engineering and Technologies (IC-GET 2015), Coimbatore, India, 2015, pp 1–4.

- [12] P. S. Chinchansure and C. V. Kulkarni, "Home Automation System based on FPGA and GSM", in 2014 International Conference on Computer Communication and Informatics (ICCCI), Coimbatore, 2014, pp. 1–5.

- [13] S.P. Kumar, S.V. Rao, "RF Module Based Wireless Secured Home Automation System Using FPGA", Journal of Theoretical and Applied Information Technology, July 2015, 20, 77(2).

- [14] O.V. Rusu, A.V. Duka,"Monitoring and Control Platform for Homes Based on FPGA, SoC and Web Technologies", Procedia Engineering, Jan 2017, 181, pp.588-595.

- [15] K. Laubhan, et.al, "A Low-Power IoT framework: From Sensors to the Cloud", in 2016 IEEE International Conference on Electro Information Technology (EIT), Grand Forks, 2016, pp.648–652.

#### **BIOGRAPHIES OF AUTHORS**

Dr. Ooi Chee Pun received his M.Sc. in Electronics from Queen's University of Belfast, UK and a Ph.D. in Engineering from University of Malaya. He is currently a senior lecturer at Multimedia University. Dr. Ooi's areas of expertise include FPGA implementation and embedded system design. He has been involved in various government-funded projects since he started his career with the University. His works have been published in numerous international journals and conferences. Dr. Ooi has been actively involved in designing hardware prototype for FPGA based embedded systems. He is also teaching digital computer design and computer architecture at both undergraduate and postgraduate levels, as well as conducting trainings for industries. In addition, Dr. Ooi is also a regular participants in competitions such as Innovate Malaysia Design Competition, ITEX and PECIPTA, from which he has won several awards.

Fpga-based embedded architecture for IoT home automation application (Chee-Pun. Ooi)

| Dr. Tan Wooi Haw received his M.Sc. in Electronics from Queen's University of Belfast, UK and a Ph.D. in Engineering from Multimedia University. He is currently a senior lecturer at Multimedia University. Dr. Tan's areas of expertise include image processing, embedded system design, Internet of Things (IoT), machine learning and deep learning. He is teaching embedded system design and computer networking at both undergraduate and postgraduate levels, as well as providing trainings and workshops for industries especially in the areas of Internet of Things (IoT), machine learning and deep learning. His research works have been published in numerous international journals and conferences. Besides, he has also co-authored two textbooks on microcontroller systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mr Cheong Soon Nyean received his B.Eng. (Hons) and his Master of Engineering Science at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multimedia University, Malaysia. He is currently a senior lecturer at Faculty of Engineering, Multimedia University, Malaysia. He is a reviewer for a number of international journals and conferences. He has received grants from Telekom Malaysia, Penang ICT, MOSTI and MOHE for his research works. Cheong Soon Nyean has published papers in the form of books, book chapters, peer-reviewed journals and international conferences. His teaching and research interests include web engineering, natural user interface, smarthome, gerontechnology, educational technology and interactive multimedia content.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ms Lee Yee Lien B.Eng. and M.Eng. degrees in 2002 and 2007 respectively. She has been attached to the Faculty of Engineering, Multimedia University, since 2008. She teaches programming, object-oriented designs, and digital computer design. Her research interests include smart living technologies and applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dr Vishnu Monn Baskaran is a Senior Lecturer with the School of IT, Monash University Malaysia. He received his B.Eng. (1st class Hons.) and M.Eng. Degrees in Electrical and Electronics Engineering from University Tenaga Nasional, Malaysia in 2004 and 2007, respectively. In 2016, he obtained his Ph.D. in Engineering from Multimedia University, Malaysia. He was with Multimedia University from 2009 to 2017, and prior to that, a R&D engineer with Panasonic R&D Centre Malaysia from 2005 to 2009. His research interests include multidisciplinary parallel computing research, predictive analytics and statistics with special interest in Markov model. He has successfully solicited research grants worth RM 1.25 million as principal/co-principal investigator and he has published various research papers in the area of network and video processing. He is also well experienced in academic teaching for programming courses. These courses include C/C++ programming and Parallel Processing & Programming. He is a recipient of an excellent teaching award from Multimedia University. He has also published a book chapter specifically for parallel programming using the C programming language. In addition, Vishnu regularly provides technical consultancy to the industry. Notable consultancies include Motorola, Robert Bosch, Sony Electronics, MIMOS, Texas Instruments, Keysight, Contraves, and Cyber Security Malaysia. |

| Mr Low Yeong Liang obtained Bachelor of Engineering (Hons) Electronics from Multimedia<br>University in 2017.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |