# Implementation of a camera system using nios II on the altera DE2-70 board

## Chan Boon Cheng, Asral Bahari Jambek

School of Microelectronic Engineering, Universiti Malaysia Perlis, Malaysia

| Article Info                                                                                                | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Article history:                                                                                            | The implementation of a camera system with a field programmable gate                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Received Sep 25, 2018<br>Revised Nov 26, 2018<br>Accepted Jan 28, 2019                                      | array (FPGA) is an important step within research towards constructing a video processing architecture design based on FPGA. This paper presents the design and implementation of a camera system using the Nios II soft-core embedded processor from Altera. The proposed camera system is a flexible platform for the implementation of other systems such as image processing                                                                                                                    |  |  |  |  |  |  |  |

| Keywords:                                                                                                   | and video processing. The system architecture is designed using the Quartus II SOPC Builder System and implemented on an Altera DE2-70 development                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Cyclon II EP2C70 FPGA<br>SDRAM controller<br>SOPC builder<br>Terasic TRDB-D5M                               | platform. The image or video is captured using a Terasic TRDB-D5M camera and stored into two different synchronous dynamic random access memories (SDRAM) using an SDRAM Controller. The specifications of the Terasic TRDB-D5M and SDRAM are examined to confirm that the recorded and stored data match. The results of this experiment show that the system is able to record and store data correctly into SDRAM. The data in the SDRAM correctly displays the recorded image on a VGA monitor. |  |  |  |  |  |  |  |

|                                                                                                             | Copyright © 2019 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Corresponding Author:                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Chan Boon Cheng,<br>School of Microelectronic Engineeri<br>Universiti Malaysia Perlis,<br>Perlis, Malaysia. | ng,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

Email: chanbc91@gmail.com

#### 1. INTRODUCTION

The implementation of a camera system is important for FPGA-based processing applications, and especially for video processing. The design of an architecture for a camera system is major stage in the further development of a video processing system on an FPGA platform [1]. An intelligent camera system may be implemented on any real-life video processing-based design. The proposed system is implemented on the Altera DE2-70 development platform [2, 3], and the Altera Cyclone II 2C70 FPGA device is the core of the system. The role of the Cyclone II 2C70 FPGA is as a platform for the architecture design of the camera system. In order to make full use of the Cyclone II 2C70 FPGA, the Quartus II system on programmable chip (SOPC) builder was used as the main software for architecture design [3-5].

The proposed camera system makes use of an external peripheral device, the Terasic 5 Mega Pixel Digital Camera (TRDB-D5M). The output data of the TRDB-D5M is in raw format [6], and needs to be converted to RGB format to reduce the complexity of data storage and processing applications. The RGB conversion of captured video for further processing or storage is well-understood in video processing applications [7]. The full resolution frame rate of the TRDB-D5M Camera is up to 15 frames per second (FPS), and the image capture frame resolution is up to 2592\*1944 pixels [6, 8].

SDRAM plays an important role in the design of the camera system [9]. The Altera DE2 board contains an SDRAM chip that can store 8 Mbytes of data, in which the memory is organized into 1M x 16 bits x 4 banks. In order to access the SDRAM Chip, an SDRAM controller circuit is needed while working on the architecture design of the camera system. This SDRAM controller circuit generates signals which can

communicate with the SDRAM chip when receiving read or write instructions from the Cyclon II 2C70 processor [2, 10].

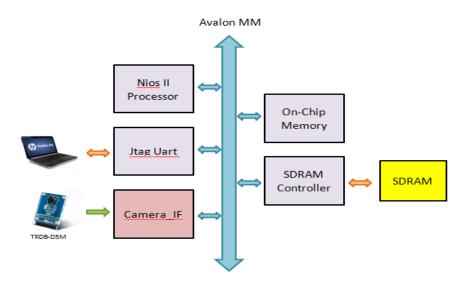

Architecture is the most important part of a camera system design [11], and errors in design or simulation will give rise to major or minor errors at the subsequent compilation stage. Figure 1 presents a typical block diagram of the architecture design for the proposed system. The user is able to debug the program in C/C++ language using the Nios II Software Build Tool for Eclipse [1, 3, 5, 12] and to download the instructions into the Nios II processor through the joint test action group-universal asynchronous receiver transmitter (JTAG-UART) core. The video captured by the TRDB-D5M camera is converted into RGB format and stored in the SDRAM Chip through the camera\_if controller and the SDRAM controller. Instructions for writing from the Nios II processor allow the SDRAM controller to carry out writing of the recorded data to the SDRAM Chip. The data correctly stored in SDRAM is able to display the recorded image on a VGA monitor [13, 16]. A more detailed explanation of the communication between the TRDB-D5M and the SDRAM chip will be discussed in Section 3.

Figure 1. Typical block diagram of the architecture design for the proposed system

In this article, several methods for the design of camera system architectures and applications are surveyed. The architecture design and applications examined are as follows: the implementation of a smart camera system on Xilinx VSK platform [9], the implementation of an open image processing system on the Altera DE2-70 board [8], the implementation of a smart camera on the Altera Stratix EP1S60F1020C7 device [1], the implementation of a camera system controlled from an LCD touch panel on an Altera DE2 board [14], and a real-time edge detector implementation on FPGA [15]. In Section 2, the design of these architectures and the application of existing methods are discussed. This section ends with a comparison between the pros and cons of existing methods for architecture design. In Section 3, a detailed description is given of the proposed implementation for a camera system. Section 4 describes the outcome of the design in terms of the flow of data conversion and storage.

### 2. LITERATURE REVIEW

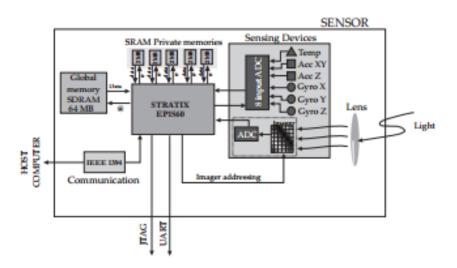

The design of camera system architecture plays an important role in the implementation of a video processing application on FPGA. An intelligent architecture design is able to run perfectly on any processing implementation of the camera system. The research on an FPGA-based smart camera implementation presented by the author in [1] provides another reference for the use of an Altera platform. The Altera Stratix EP1S60F1020C7 plays a major role in this system. The sub-memory is 10 Mb of SRAM, while the major data storage device is 64 Mb of SDRAM. A smart camera LUPA-4000 with an image sensor of 4 Mpixels is the current camera configuration. The communication between smart camera, SSRAM, SDRAM and host computer is shown in Figure 2.

Figure 2. Communication between smart camera, SSRAM, SDRAM and host computer

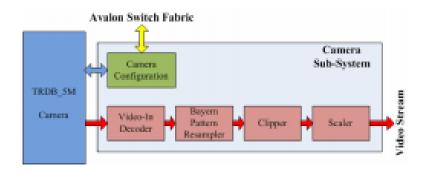

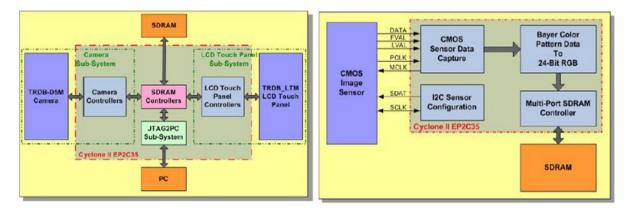

In [8], the author described the implementation of an open image processing system on the FPGA platform, using the Altera DE2-70 as the chosen development platform. The TRDB-D5M camera and the 4.3" Ultra-high Resolution LCD Touch Panel (TRDB-LTM) are important external peripherals completing the research. The camera sub-system core in this paper provides a good reference for the current camera implementation. The proposed camera sub-system is able to produce a 24-bit RGB image frame with a resolution of 640x480 pixels. SDRAM is used as the major data storage device for the captured images or video for further processing and display. Figure 3 shows the design of the camera sub-system proposed by the author.

Figure 3. Design of the camera sub-system proposed by the author

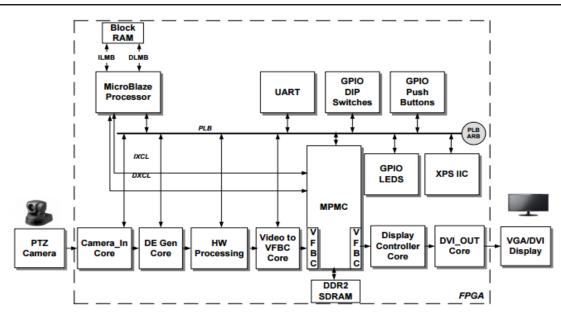

The author of [9] has proposed an FPGA-based smart camera system, which involves the two important features of a pan-tilt-zoom (PTZ) Camera and a Spartan-3A DSP-based Xilinx VSK platform. DDR2. The major data storage device for storing and extracting frames is SDRAM. Figure 4 shows the block diagram for the architecture design proposed by this author.

The architecture of the camera sub-system design presented in [14] provides another reference for the current camera implementation. An LCD touch panel sub-system is a further external peripheral used to display the captured image. JTAG-UART is used to transfer data, and the main FPGA device is the Altera DE2. The camera controller, SDRAM controller and LCD touch panel controller are responsible for communication between the FPGA board, internal devices and external peripheral devices. Figure 5 shows the proposed architecture design of the full system. The camera sub-system in this proposed method captures the image from the CMOS image sensor, which then undergoes some processing before being stored into SDRAM. Figure 6 shows the block diagram of this proposed camera sub-system.

Figure 4. Block diagram for the architecture design proposed by this author

Figure 5. Proposed architecture design of the full system

Figure 6. Block diagram of this proposed camera sub-system

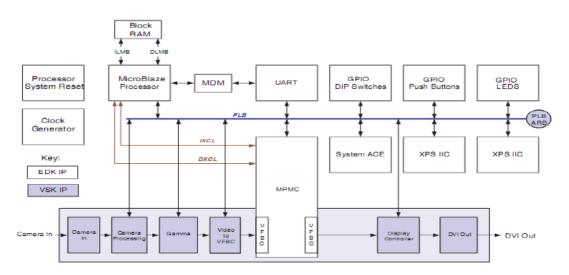

In [15], the author proposed a real-time implementation for edge detection using FPGA. A CMOS camera was chosen to capture images in real time and perform further processing steps. The Sobel, Prowitt, Robert and Compass edge detection algorithms were studied and implemented in this design. The Microblase RISC processor was used as the main processing unit, and a DVI display was used as another external peripheral for displaying the outcome of processing. The design of this architecture included LEDR PIO, push-button and switch PIO and other system peripherals. Figure 7 shows the design of the system architecture.

Table 1 shows a comparison between the implementations of camera systems on FPGA. Each of the proposed methods involves an external peripheral camera and FPGA. The different types of output depend on the relevant FPGA. All of these methods have the common feature of collecting video frames using an external peripheral camera and storing these into a memory device for display or further processing. The various development platforms contain different types of memory device for data storage. For example, the Xilinx VSK uses DDR2 SDRAM for video frame storage, while the Altera DE2 and DE2-70 use SDRAM for video frame storage. The Altera Stratix uses both SRAM and SDRAM to store video frames.

Figure 7. Design of the system architecture

| Features             | [1]                       | [8]                                    | [9]                           | [14]                                 | [15]                         |

|----------------------|---------------------------|----------------------------------------|-------------------------------|--------------------------------------|------------------------------|

| Year                 | 2007                      | 2015                                   | 2013                          | 2009                                 | 2011                         |

| Development Platform | Altera Stratix            | Altera DE2-70                          | Xilinx VSK                    | Altera DE2                           | Microblaze RISC<br>Processor |

| Camera               | 4Mpixels<br>LUPA-4000     | TRDB-D5M Camera                        | PTZ Camera                    | TRDB-D5M Camera                      | CMOS Camera                  |

| Display Device       | VGA Monitor               | TRDB-LTM LCD                           | VGA Monitor                   | TRDB LTM LCD                         | DVI Display                  |

| Memory Usage         | SRAM &<br>SDRAM           | SDRAM                                  | DDR2 SDRAM                    | SDRAM                                | Line Buffer                  |

| Output Display Size  | 640*480                   | 680*480                                | 752*582                       | 640*480                              | 720*480                      |

| Data Processing      | Window-Base<br>Processing | Image Processing                       | HW Processing                 | Not Stated                           | Image Processing             |

| Software             | Not Stated                | Quartus II, Nios II<br>SBT for Eclipse | ISE, EDK, SDK<br>Xilinx Tools | Not Stated                           | Not Stated                   |

| Language             | VHDL, C/C++,<br>Assembler | HDL, VHDL, C/C++                       | Not Stated                    | C/C++                                | Not Stated                   |

| Special Features     | Not Stated                | Selection Mode<br>Display              | Not Stated                    | Adjustable Exposure<br>Time Register | Edge Detection               |

The selection mode display described in [8] is an extra feature that allows switching between different modes of image processing. The processing mode includes negative colour, edge detection, a median filter and a sharpen convolution filter. The FPGA-based digital camera system proposed in [14] involves the special feature of an adjustable exposure time register. This feature provides adjustable brightness for display image by increasing or decreasing the register value. The edge detection proposed in [15] is another interesting feature that allows the detection of the edges of a captured object. Each of the features listed above can be implemented after the implementation of the camera system.

The implementation of the current camera system is suited to the Altera DE2-70 platform, due to the various types of language chosen to carry out architecture design. The C/C++ algorithm design in the Nios II SBT for Eclipse allows the design of various types of function and run on the Altera DE2-70 board. The Altera DE2-70 board contains both SDRAM and SSRAM devices; SDRAM is suitable for the storage of processed video frames, while SSRAM is suitable for storage of temporary video frames or instructions. The architecture design step is simple, and is carried out using the Qsys function in Quartus II software. The combination of Verilog and Qsys architecture designs simplifies the setting step for the pin planner and camera\_if settings. The complete system design is discussed in Section 4.

#### 3. RESEARCH METHOD

In Section 3, the existing methods for implementation of camera systems are discussed. Section 4 explains the architecture design and the important peripherals used in the proposed camera implementation system. The proposed architecture design is implemented on the Altera Cyclone II 2C70 FPGA and is

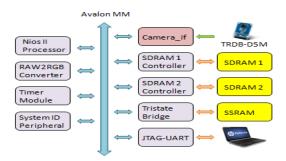

interfaced with an external peripheral, the TRDB-D5M. The important components of the architecture design include a Nios II soft-core processor, one Cypress CY7C1380C SSRAM, two 32\_Mb SDRAMs with an SDRAM controller, a JTAG-UART, a RS-232 serial port universal asynchronous receiver transmitter (UART), a timer module, an Avalon bus, a TRDB-D5M with a camera\_if and a system ID Peripheral. Figure 8 shows the block diagram for the proposed design for the implementation of the camera system.

Figure 8. Block diagram for the proposed design for the implementation of the camera system

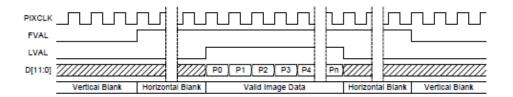

The TRDB-D5M is the major external peripheral that carries out the image capture progress. The pixel array in the TRDB-D5M consists of a 2752-column by 2004-row matrix of pixels, addressed by column and row. The output of the pixels is in a Bayer pattern format, consisting of four colours, Green1 (G1), Green2 (G2), Red (R) and Blue (B) [6]. The FRAME\_VALID and LINE\_VALID signals in the TRDB-D5M indicate the boundaries between the frame and the outline of the output image. In order to capture a valid image, FRAME\_VALID and LINE\_VALID signals are sent, and valid image data is captured and stored into SDRAM. Figure 9 shows the theoretical communication between FRAME\_VALID (FVAL), LINE\_VALID (LVAL) and SDRAM.

Figure 9. Theoretical communication between FVAL, LVAL and SDRAM

The proposed architecture design was developed using the Qsys tool from the Quartus II Version 10.0 software. Version 10.0 of the Quartus II was chosen rather than Version 13.0, since the external peripheral TRDB-D5M performs better in the older version. Figure 10 shows the interconnection of the proposed camera system in the Qsys tool. The system design is based on the block diagram shown in Figure 8. During the system design, a phase-locked loop (PLL) was used to generate a 100 MHz clock for the system and 100 MHz pulse with a -65 degree phase shift for SDRAM, while 50 MHz clock pulses were used as the supply for the PLL module.

SSRAM was chosen as the reset and exception vector for the Nios II processor design, in order to avoid exceeding block limitations in SignalTap II when generating the waveform of SDRAM data. The camera\_if function in the Qsys tool performs as a communication bus between the processor and the TRDB-D5M camera. Verification for the port of the TRDB-D5M camera was carried out using Verilog coding and this was then incorporated into the design unit in Quartus II software. The verification of the port enables the TRDB-D5M to accept and send signals, from and to the development platform, through camera\_if. Figure 11 shows the part of the verification code involving port declarations.

The Nios II processor is the primary component in the design of the system. Its relatively high processing speed is able to accelerate the task given to the development platform. The Nios II full version soft-core processor is chosen for this system, since its highest processing speed is approximately 101 Dhrystone million instructions per second (DMIPS) at 100 MHz. A push-button GPIO is added to the Qsys

design, which includes start and stop recording functions. The camera begins capturing and saves the image into SDRAM when the start recording push-button is triggered. At the same time, the GPIO of the seven-segment LED display shows the running time of the record function.

| Jse      | Connecti                    | Module Name        | Description                          | Clock       | Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | End        | Tags | IRQ |

|----------|-----------------------------|--------------------|--------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|

| V        |                             | 🗆 pll              | Avalon ALTPLL                        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $ \longrightarrow $         | pll_slave          | Avalon Memory Mapped Slave           | clk         | 0x00401090                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0040109f |      |     |

| 1        |                             | 🖂 сри              | Nios II Processor                    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          |                             | instruction_master | Avalon Memory Mapped Master          | pll_c0_syst |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $\parallel \succ \prec$     | data_master        | Avalon Memory Mapped Master          |             | IRQ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IRQ 31     |      | ~   |

|          | $  \rightarrow \rightarrow$ | jtag_debug_module  | Avaion Memory Mapped Slave           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x00400fff |      |     |

| <b>V</b> |                             | jtag_uart          | JTAG UART                            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $   \longrightarrow$        | avalon_jtag_slave  | Avaion Memory Mapped Slave           | pll_c0_syst | 🖹 0x004010a0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x004010a7 |      | ┝   |

| 1        |                             | 🖃 uart             | UART (RS-232 Serial Port)            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $   \rightarrow$            | s1                 | Avalon Memory Mapped Slave           | pll_c0_syst |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0040101f |      |     |

| <b>V</b> |                             | 🖃 camera           | CAMERA_IF                            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $   \rightarrow$            | s1                 | Avalon Memory Mapped Slave           | pll_c0_syst | Ox00401060                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0040106f |      |     |

| 1        |                             | ⊡ timer            | Interval Timer                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $   \longrightarrow$        | s1                 | Avaion Memory Mapped Slave           | pll_c0_syst |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0040103f |      | ┝─  |

| <b>V</b> |                             | timer_stamp        | Interval Timer                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $   \rightarrow$            | s1                 | Avalon Memory Mapped Slave           | pll_c0_syst | 0x00401040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0040105f |      | ┝   |

| 1        |                             | sysid              | System ID Peripheral                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $   \rightarrow$            | control_slave      | Avalon Memory Mapped Slave           | pll_c0_syst | 🖹 0x004010a8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x004010af |      |     |

| 1        |                             | 🖃 ssram            | Cypress CY7C1380C SSRAM              |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $     \rightarrow$          | s1                 | Avalon Memory Mapped Tristate Slave  | pll_c0_syst | Ox00200000     Ox00200000     Ox00200000     Ox00200000     Ox00200000     Ox00200000     Ox00200000     Ox002000000     Ox000000     Ox00000     Ox000000     Ox00000     Ox000000     Ox00000     Ox000000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox000000     Ox00000     Ox00000     Ox00000     Ox000000     Ox00000     Ox000000     Ox000000     Ox00000      Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox0000     Ox00000     Ox0000     Ox0000     Ox0000     Ox0000     Ox00000     Ox0000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox0000     Ox000     Ox000     Ox0000     Ox000     Ox000     Ox000     Ox00 | 0x003fffff |      |     |

| 1        |                             | tristate_bridge    | Avalon-MM Tristate Bridge            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $  \rightarrow \rightarrow$ | avalon_slave       | Avaion Memory Mapped Slave           | pll_c0_syst |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

|          | $    \subseteq$             | tristate_master    | Avalon Memory Mapped Tristate Master |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

| <b>v</b> |                             | pio_led            | PIO (Parallel I/O)                   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      |     |

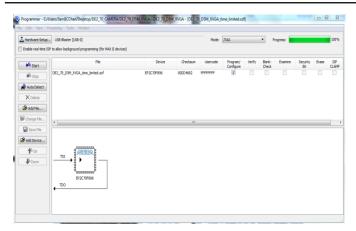

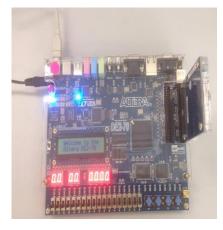

|          | $  \rightarrow$             | s1                 | Avalon Memory Mapped Slave           | pll_c0_syst |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0040107f |      |     |