DOI: 10.11591/telkomnika.v12i8.5644

# Research on Multichannel Test Device of Missile Fuze

7196

# Guoyong Zhen<sup>1,2</sup> Yanhu Shan\*<sup>1,2</sup>, Yiran Wei<sup>1,2</sup>

<sup>1</sup>National Key laboratory for Electronic Measurement Technology,

North University of China, Taiyuan 030051

<sup>2</sup>Key Laboratory of Instrumentation Science & Dynamic Measurement of Ministry of Education,

North University of China, Taiyuan 030051

\*Corresponding author, e-mail: shanyanhu@126.com

### Abstract

This paper introduces the design of multichannel acquisition circuit based on FPGA which samples and records the Doppler signals, ignition signal and the working condition of fuze security enforcement agencies of missile fuze in real-time in the test of high speed dynamic intersection. Furthermore, for the problem of increasing number of sample channel which causes the complexity of the multiplexer control, a general programmable channel switching method is proposed based on FPGA. In the method, FPGA is the control core, and using the internal ROM resource effectively simplifies the complexity of channel switch in the multichannel acquisition system. This paper analyzes the acquisition system design, and describes the design of hardware circuit and analog switch address coding in detail. The test result shows that the acquisition circuit meets the design requirements with high sampling precision and application value.

Keywords: missile fuze, multichannel, FPGA, switching method

Copyright © 2014 Institute of Advanced Engineering and Science. All rights reserved.

#### 1. Introduction

In the missile dynamic intersection flight simulation test, usually test method is using the ground cable transmitting information, the tape recorder and telemetry technology. For the few test channels and low speed flight simulation test, the method of using the ground cable transmitting information can meet the experiment requirement. However, for the high speed flight experiment, due to the releasing speed and distance of cable, and the reliability reasons such as disturbances, broken line, it cannot be used. The tape recorder is being phased out gradually because of the complex operation and the mechanical system reliability [1, 2]. Due to the high cost and test debugging complexity the telemetry is used on small tactical missile battle less. With the widely used of storage test technology which has many advantage such as high reliability, low cost, multichannel, large capacity, easy operation and so on, the solid state recorder is the best resolution for the test of missile fuze [3-5].

With the increasing performance of the missile, the test system is more and more complex and the number of test signal is also growing. In the high-speed dynamic intersection experiment, the Doppler signals, ignition signal and the working condition of fuze security enforcement agencies are needed to record in real-time. The more test channels are, the more complex the structure of the data frame is. The channel switch is mainly related to the order of input channel and the data frame. When the number of test signal is less and the structure of data frame is simple, regulating the switch order of multiplexer or data frame can achieve multichannel acquisition. However, when the number of channel is many, the above resolution will undoubtedly increase the difficulty and complexity of the system design. Channel switch of multichannel acquisition system is becoming more complex. How to design of channel switching reasonably has become the key technology of the design of acquisition system. To solve these problems, we proposed a design of solid state recorder for the test of missile fuze. And for the requirement of multichannel test, a general programmable multichannel acquisition method is also proposed, which simplify the hardware design for the multichannel acquisition circuit. When the flight simulation test is finished, we recover the flight data from the recorder which is convenient for analyzing the cause of malfunction.

## 2. The Structure and Working Principle of System

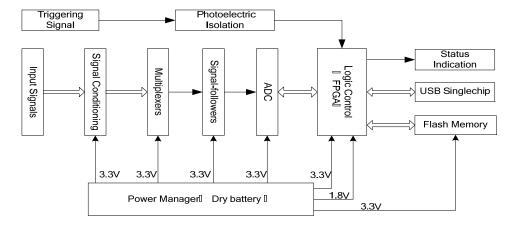

The block diagram of acquisition and storage system is shown in Figure 1. The system takes the 27V pulse signal whose during time is 100ms as the trigger signal. When the mixed signals go through the input interface, these signals are firstly regulated by the signal regulation module and are then transmitted to analog switch. Then, the analog signals are transmitted through analog switch that are sequentially controlled by the logic control module and sent to ADC. The FPGA stores the converted data into Flash memory. The recorded data is uploaded via USB after finishing the test. The system uses dry battery pack as the independent power supply, which avoids the need of power supply by missile and is convenient for interface design and installation.

Figure 1. The Block Diagram of Acquisition and Storage System

# 3. The Design of Acquisition and Storage Module

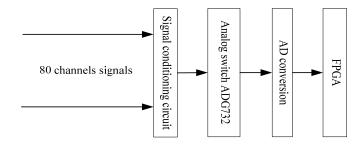

After modulating by the operational amplifier, the modulated analog signals are outputted to analog multiplexer ADG732. And then FPGA control the address lines of ADG732 to switch in an order, so that the 80 analog signals can be orderly inputted into the analog-to-digital converter- THS1040. The output digital signal of AD-THS1040 is gathered by FPGA in 10 bit data length. In the FPGA, the sampled data will be framed as the data pack. The structure diagram of acquisition process is shown as the Figure 2.

Figure 2. The Diagram of Acquisition Process

### 3.1. Signal Conditioning

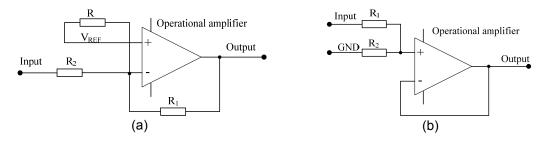

In the process of design, in order to guarantee the integrity and accuracy of signals before they are inputted to analog switch, we use operational amplifier with the character of rail to rail to modulate the signal. This design improves the input impedance of signal, and at the same time also reduces the output impedance of modulated signal. After modulating, all the high amplitude signals are processed uniformly into  $0\sim$ 2V signals that are convenient for data

7198 ■ ISSN: 2302-4046

sample. The -10V $\sim$ +10V and -30V $\sim$ +30V interface circuit is shown in the Figure 3(a). The 0 $\sim$ +40V, 0 $\sim$ +10V interface circuit as shown in the Figure 3(b). According to the different range of input, the value of R1 and R2 is different. In Figure 3(a), the output VO1 is:

$$V_{O1} = \left(1 + \frac{R_1}{R_2}\right) V_{REF} - \frac{R_1}{R_2} V_{I1} \tag{1}$$

In the Figure 3(b), the output VO2 is:

$$V_{02} = \left(1 + \frac{R_2}{R_1}\right) V_{I2} \tag{2}$$

According to the Equation (1) and Equation (2), the selection of R1 and R2 is shown in Table 1.

Figure 3. (a)-10V~10V and -30V~30V interface circuit, (b) 0V~40V and 0V~10V interface circuit

Table 1. The Value of R1 and R2

| Input range | R1(Ω) | R2(Ω) |

|-------------|-------|-------|

| -10V∼+10V   | 13K   | 150K  |

| -30V∼+30V   | 4.7K  | 150K  |

| 0∼+40V      | 120K  | 6.2K  |

| 0∼+10V      | 160K  | 39K   |

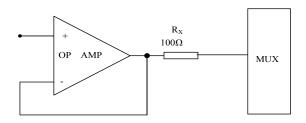

The operational amplifier is susceptible to the capacitive load in the unity gain configuration. To avoid the phenomena of oscillating, the resistor RX of  $100\Omega$  can be inserted in the output of operational amplifier. The block diagram is shown in Figure 4.

Figure 4. The Block Diagram of the Output of op amp

# 3.2. General Programmable Channel Switching Method

The sample rate of each signal is different, so when data packing the hybrid frame is used with prime-frame and subframe. According the requirement of frame format, there is no regular switch between channels. The conventional method is regulating the order of multiplexer channels to meet the requirement of the sequential control of FPGA. However, when the number of signal channel is larger, the hardware design and the control of FPGA are more complex. So the conventional method is fit for the acquisition system with a few channels, not

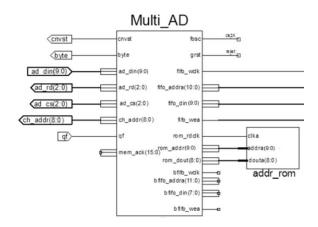

for the system with a large number of channels. Therefore, for the complex channel switch, we proposed a general programmable channel switching method. We encode all the switch addresses according to the frame format, and write them into the internal ROM of FPGA in advance. When the acquisition system works, the addresses of channels are read out from ROM which is named addr\_rom in Figure 5 to control the group of multiplexers.

Figure 5. The Control of ROM in the FPGA

In the acquisition system, each sixteen-channel multiplexer contains four address gates (A3, A2, A1 and A0) and one enable signal (EN). Each enable signal of multiplexer uses one control line alone and all the multiplexers share the address lines. For the eighty channels acquisition system, five multiplexers are needed. So, nine control lines can determine a channel address, which is shown in Table 2.

Table 2. The Corresponding Relation of the Multiplexer Address

| 9 bits of address |                    |     |     |     |     |               |    |    |    |  |  |

|-------------------|--------------------|-----|-----|-----|-----|---------------|----|----|----|--|--|

|                   | the enable signals |     |     |     |     | address gates |    |    |    |  |  |

|                   | EN4                | EN3 | EN2 | EN1 | EN0 | A3            | A2 | A1 | A0 |  |  |

The method realizes complete separation between the input signal channel and the frame format design. And the method is programmable, which can adjust the address code of ROM with the change of frame format. So, the method has generality. In the frame format, except the characteristic signal, one signal is according to one multiplexer address. The data frame format is 58×10. The characteristic data is 50, so the address number is 530. The data width of 9 bit and the depth of 1024 bit of the ROM in FPGA can meet the address control requirement.

### 3.3. Storage Module

The storage module uses Flash memory K9WBG08U1M (4GByte) as data storage, due to the characteristics of small size, low power consumption, large memory capacity and so on. The writing and reading operation of Flash is in the unit of page. It is necessary to write the control word and address of next page again after finishing writing one page. Therefore, to guarantee data integrity in the alternating time of adjacent page, the internal FIFO of FPGA is used as data cache. The sampled data is written into FIFO first, and then stored to Flash. In the process of data operation, the average speed of input of FIFO is low than output. To improve the writing speed of Flash, the interleaving two-plane programming mode is used in the writing operation that the fastest writing speed can reach 30MByte/s. The waiting time of page programming is reduced to the minimum by the interleaving pattern. Also, to manage the invalid block of Flash conveniently, the address of invalid block is identified and written into the ROM of FPGA. When in the operation of page programming, reading or erasing, the address is read out to compare with the current address to identify whether the current block is invalid or not.

7200 ■ ISSN: 2302-4046

## 4. The Design of Resistance to Overload

The solid state recorder accomplishes the acquisition and storage of signals. During the collision of missile high-speed intersection, the resistance to overload capacity of recorder reaches more than 2000g. So the effective measure should be taken to strengthen overload resistance of the recorder. After welding, chip itself is suspended in circuit boards, and connect the circuit boards only through the chip pin. Chip and circuit board didn't really form a whole. When the recorder is hit so hard, because the quality of various components is different, the overload is also different. This will be very easy to appear loose solder joints, virtual welding or pull up welding plate, etc. The circuit is packaged with encapsulating material and then become an integrated structure which is help for protecting the circuit. The process is called embedment. With a special resin of high strength and high toughness the chips and the circuit board are encapsulating into a whole, which can restrict the movement between the chip and circuit board. In addition, this has the effect of stable components, circuit parameters, to ensure no damage to circuit under high overload.

### 5. System Test and Result

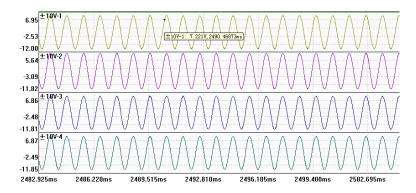

In the process of system test, a multichannel signal source is used to verify the function of the acquisition system. In the experiment, the first operation is erasing after power-on. When the erase operation is complete, +27V step signal is loading to start sampling and recording. After recording, the data is read into computer via the USB interface, and then analyze the data graphically. The software can draw up the wave of all the channels. Meanwhile, it also can check the frame format whether correct or not. The partial channels' waveform is shown in the Fig.6. The frame format of all the data of each channel is correct. Through acquiring the sine ware, the acquisition precision which is expressed by ENOB can be calculated [6-9]. The ENOB of the acquisition system is better than 8 bit.

Figure 6. The Partial Channels' Waveform

#### 6. Conclusion

This paper proposed a general programmable multichannel acquisition method for the missile fuze test. For the eighty channels analog signals which consists Doppler signal and ignition signal and the working conditions of the security fuze enforcement agencies, the device is used solid state recorder which can resist the overload capacity of more than 2000g and be employed repeatedly. Therefore, the design reduces experiment cost and has engineering practical value. The device has been used in the high-speed dynamic intersection experiment, which records the signals correctly and provides the accurate data for the fuze design and the fault analysis.

#### References

[1] LI Jing hai, SUN Xi jing. A Fast Data Processing Method in Air Defense Missile Proximity Fuse Test. Journal of Naval Aeronautical and Astronautical University. 2012; 27(4): 439-442.

- [2] Chen Ruo fei, Bai Hao. A Modularized Generalization Testing System for the Radio Fuze. Guidance & Fuze. 2010; 31(3): 13-17.

- [3] Wei Wan, Yong Hong Hu, Peng Wu. Multi Channel Recorder for Unmanned Aerial Vehicle Based on ARM9. Advanced Materials Research. 2011; 181(3): 604-609.

- [4] Abdallah M, Elkeelany O, Alouani AT. A Low-Cost Stand-Alone Multichannel Data Acquisition, Monitoring, and Archival System with On-Chip Signal Preprocessing. Instrumentation and Measurement. *IEEE Transactions on.* 2011; 60(8): 2813-2827.

- [5] Su Shujing, Lei Jiansheng. A Method of Multi-channel Data Acquisition with Adjustable Sampling Rate. *TELKOMNIKA: Indonesian Journal of Electrical Engineering*. 2013; 11(9): 5299-5307.

- [6] Shirong Yin, Yituan He. Sinusoidal Signal Generator for ADC Testing in Mixed-Signal SOC. *TELKOMNIKA: Indonesian Journal of Electrical Engineering*. 2013;11(7): 3711-3717.

- [7] Daniel Belega, Dario Petri. Accuracy analysis of the amplitude estimation of a sine-wave by the energy-based method using the direct and indirect procedures. *Measurement*. 2012; 45(9): 2264-227.

- [8] IEEE Std. 1241-2000, IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, IEEE, NY, 2001.

- [9] Armin Jalili, Sayed Masoud Sayedi, J Jacob Wikner, Abolghasem Zeidaabadi Nezhad. A nonlinearity error calibration technique for pipelined ADCs. *Integration, the VLSI Journal.* 2011; 44(3): 229-241.