# Mathematical analysis of cost function and reliability condition for new proposed multilevel inverter topology

# D. Karthikeyan<sup>1</sup>, K. Vijayakumar<sup>2</sup>, D. Senthil Kumar<sup>3</sup>, Daki Krishnachaitanya<sup>4</sup>

<sup>1,2</sup>Departement of Electrical and Electronics Engineering, SRM Institute of Science & Technology, India <sup>3</sup>Departement of computer science Engineering, SRM Institute of Science & Technology, India <sup>4</sup>Departement of Electrical and Electronics Engineering, Vellore Institute of Technology, India

## **Article Info**

#### Article history:

Received Feb 19, 2020 Revised Apr 20, 2020 Accepted May 5, 2020

## Keywords:

Cost function Mathematical analysis Mean time failure Reliability analysis

## ABSTRACT

In this paper cost function and reliability analysis of classic novel symmetric multilevel inverter topology has been presented. Cost function and reliability analysis are the economical factors of the efficiency of an inverter, this made the intrest in this area.cost function deneotes the cost of the inverter based on the power flow, reliability explain the mean time failure proportional to the life span. Firstly the cost function of the novel topology has been proposed using mathematical calculation using various current rating and the results are validated compared with exiting topology. Secondly reliability analysis equations and the results are evaluate the reliability of the switch with respect to the failure rate and mean time period of the switch using fedis and markow reliability analysis equations and the results are the compared with the conventional multilevel inverter, cost function and reliability analysis of the proposed multilevel inverter.

Copyright © 2020 Institute of Advanced Engineering and Science. All rights reserved.

## **Corresponding Author:**

D. Karthikeyan, Departement of Electrical and Electronics Engineering, SRM Institute of Science & Technology, Kattankulathur, Tamil Nadu, India. Email: karthikd@srmist.edu.in

#### 1. INTRODUCTION

Now a day's renewable energy resources like solar and wind plays a vital role in the field of energy production, particularly speaking the solar energy has numerous advantage compared to wind resources like less installation cost, enormous availability [1-4]. Cost function is defined as expressing the production cost of the product in terms of the amount produced for designing of circuit. It helps to decide the pricing of the particular product. Cost function is depends on the number of components are used in the inverter topology. If number of components is increased cost also increased. Cost function is related to cost of switch. It's depends on the various factors in this implementing the factor of the blocking voltage across the switch. Performance is the one of the factor to cost fixing [5-8]. The capability of a product to perform a required function for the given time interval is called reliability. Demonstration and taking technical and physical factors have identified role in reliability. Reliability provides the electrical and mechanical component. Failure mechanism means a set of cause's effect relation for physical, chemical or other process that relates to the root cause of the failure rate for the component [9-12].

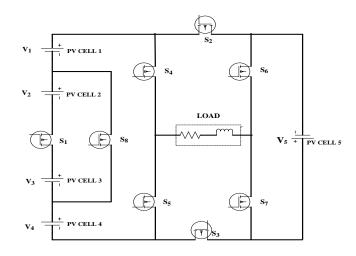

The proposed topology can produce 11-level and the level can be increase by cascading the topology both in symmetrical and as well as in unsymmetrical aspects. In this paper the cost function and reliability analysis has been analyzed and its cost function is compared with various same level existing topologies. The Figure 1 represents the new topology multilevel inverter which has 8 switches and 5 sources in symmetrical condition and can also be redrawn using three sources and two capacitor if it has been as unsymmetrical mode [13-18]. Load we are considering is practical RL load for medium voltage applications.

**G** 654

Figure 1. New topology multilevel inverter with reduced number of switches & sources

## 2. METHODOLOGY

First condition to design a noval multi level inverter topology is, it should have less number of power electronics components like less number of switches, sources and passive elements, so that the cost and size of the inverter is less [19-23]. Second condition is it should have better performance in its working condition like high voltage, current, less THD, cost function & reliability condition, here the new designed topology is analyized based on its cost function and reliability, so that its results the economic condition of the designed inverter based on cost, life span & failure condition, here two analysis has been done using mathematical equations and fedis reliability conditions to verify the circuit efficiency based on cost and maen time failure. The cost function of the proposed circuit is given below in the Section 3:

## 3. COST FUNCTION

#### 3.1. Cost function for the conventional multilevel inverter

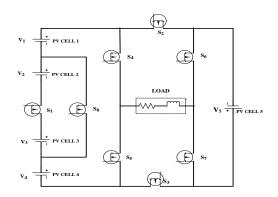

For making the analysis at first we are considering the conventional multilevel inverter topology with 12 switches and 5 sources as shown in Figure 2.

Figure 2. Conventional multilevel inverter

To make the analysis understandable, consider the SwitchesS1 and S2: per unit value=1 From this assumption the voltage across each switch is given in, in open Condition each switch will block Voltages V 1 and V 2 i.e. 1+1=2VSimilarly, S3 and S4 each will block V2 and V3 i.e. 1+1=2VSimilarly, S5 and S6 each will block V3 and V4 i.e. 1+1=2VSimilarly, S7 and S8 each will block V4 and V5 i.e. 1+1=2V respectively. Switches M1 and M4 each will block V1 and V5 i.e 1+1=2V

Mathematical analysis of cost function and reliability condition for new proposed ... (D. Karthikeyan)

Similarly Switches M2 and M3 each will block V1 and V5 i.e 1+1=2V respectively  $S_1 = S_2 = 1 + 1 = 2V \quad S_3 = S_4 = 1 + 1 = 2V \\ S_5 = S_6 = 1 + 1 = 2V \quad S_7 = S_8 = 1 + 1 = 2V \\$  $M_1 = M_4 = 1V$  $M_2 = M_3 = 1V$ Blocking Voltage across the Switch is given by  $= \frac{V_{max}}{V_{block}}$ (1)Consider  $V_{max} = 5V$  $S_{1} = S_{2} = \frac{5}{2} = 2.5V \qquad S_{3} = S_{4} = \frac{5}{2} = 2.5V \\ S_{5} = S_{6} = \frac{5}{2} = 2.5V \qquad S_{7} = S_{8} = \frac{5}{2} = 2.5V \\ M_{1} = M_{4} = \frac{5}{1} = 5V \\ M_{5} = 5V \qquad S_{7} = S_{8} = \frac{5}{2} = 2.5V \\ M_{1} = M_{4} = \frac{5}{1} = 5V \\ M_{5} = 5V$  $M_2 = M_3 \frac{5}{1} = 5V$ The Blocking Voltages across the Switches are  $S_1 = S_2 = S_3 = S_4 = S_5 = S_6 = S_7 = S_8 = 2.5V$  $M_1 = M_2 = M_3 = M_4 = 5V$ The Total Blocking Voltage of the circuit is given by  $S_1 + S_2 + S_3 + S_4 + S_5 = S_6 + S_7 + S_8 + M_1 + M_2 + M_3 + M_4 = (2.5 * 8) + (5 * 4) = 40V$  $V_{Switch}^{p.V} = \frac{\text{Total voltage}}{\text{max voltage}} = \frac{40}{5} = 8$ (2)**D T T**

$$Cost function = N_{IGBT} + \alpha V_{switch}^{P,V}$$

(3)

where  $\alpha$  is current rating

a) If  $\alpha = 0.5$

- C. F = 8 + 0.5(8) = 12b) If  $\alpha = 1.5$

- C.F = 8 + 1.5(8) = 20

c) If

$$\alpha = 2.5$$

C. F = 8 + 2.5(8) = 28

d) If

$$\alpha = 3.5$$

*C*. *F* = 8 + 3.5(8) = 36

e) If  $\alpha = 4.5$

*C*. *F* = 8 + 4.5(8) = 44

In connection with earlier analysis in section 3.1, we are moving to the comparative analayis for proposed novel topology 11-level inverter with reduced power components as shown in Figure 3.

Figure 3. Proposed novel topology 11-level inverter

Total block voltages = V1 + V2 + V3 + V4 + V5 = 1 + 1 + 1 + 1 + 1 = 5vper unit value = 1 Consider the switches S<sub>4</sub> & S<sub>5</sub> In open Condition each switch will block Voltages V<sub>1</sub> and V<sub>4</sub> = 1 + 1 = 2V Similarly, S<sub>6</sub> and S<sub>7</sub> each will block voltage V<sub>5</sub>=1V Similarly, S<sub>1</sub> block voltage V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, V<sub>4</sub> = 4V Similarly, S<sub>8</sub> block voltage V<sub>2</sub> V<sub>3</sub>=2V Similarly, S<sub>3</sub> S<sub>2</sub> block voltage V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, V<sub>4</sub>, V<sub>5</sub> = 5V Blocking voltage across the switch= $\frac{V_{max}}{V_{block}}$  V<sub>max</sub>=5V

$$S1 = \frac{5}{4} = 1.25V \qquad S8 = \frac{5}{2} = 2.5V \\ S2, S3 = \frac{5}{5} = 1V \qquad S4, S5 = \frac{5}{2} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{2} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{2} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{2} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S6, S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \qquad S4, S5 = \frac{5}{1} = 2.5V \\ S7 = \frac{5}{1} = 5V \\ S7 = \frac{5}{1} = \frac{5}{1$$

Total blocking voltage circuit given by

$S_1+S_2 + S_3+S_4 + S_5+S_6 + S_7 + S_8 = 1.25 + 1 + 1 + 2.5 + 2.5 + 5 + 5 + 2.5 = 20.75V$   $V_{\text{Switch}}^{\text{p.V}} = \frac{\text{Total voltage}}{\text{max voltage}} = \frac{20.75}{5} = 4.15V$

Cost function= $N_{IGBT} + \alpha V_{switch}^{P.V}$ where  $\alpha$  is current rating

- a) If  $\alpha = 0.5$

- c. F = 8 + 0.5(4.15) = 10.075b) If  $\alpha = 1.5$

- b) If  $\alpha = 1.5$ C.F = 8 + 1.5(4.15) = 14.225

- c) If  $\alpha = 2.5$

- C. F = 8 + 2.5(4.15) = 18.375d) If  $\alpha = 3.5$

- c. F = 8 + 3.5(4.15) = 22.525e) If  $\alpha = 4.5$

$$C.F = 8 + 4.5(5) = 26.675$$

#### 3.3. Comparison of cost function between conventional and new topology multilevel inverter

Table 1 repersents the comparison of cost function between conventional multilevel inverter and new topology multilevel inverter, from the results it is evident that the cost function of new toplogy has better performance in all the variants of " $\alpha$ " compared to the conventional topology.

| Table 1. Comparison between conventional and new topology multilevel inverter | Table 1. Comparison | between conventional | and new topology | multilevel inverter |

|-------------------------------------------------------------------------------|---------------------|----------------------|------------------|---------------------|

|-------------------------------------------------------------------------------|---------------------|----------------------|------------------|---------------------|

| Cost Function                    | <i>α</i> =0.5 | <i>α</i> =1.5 | <i>α</i> =2.5 | <i>α</i> =3.5 | <i>α</i> =4.5 |

|----------------------------------|---------------|---------------|---------------|---------------|---------------|

| Conventional Multilevel Inverter | 12            | 20            | 28            | 36            | 44            |

| New Topology                     | 10.075        | 14.225        | 18.375        | 22.525        | 26.675        |

## 4. RELIABILITY OF PROPOSED MULTILEVEL INVERTER

## 4.1. Reliability analysis

- Calculate failure rate of each switch according to data sheet to the used thyristor [24-27].

- a) Calculate the failure rate for used thyristor.

Formula for failure rate:

$$-\lambda = \lambda_{physical} \cdot \pi_{PM} \cdot \pi_{Process}$$

(4)

## $\lambda$ is failure rate

$\pi_{PM}$  is part manufacturing represents quality and technical control over manufacturing of item.  $\pi_{Process}$  is quality and technical control over manufacturing and usage.

$$\lambda_{physical} = \lambda_b$$

$\pi_{PM} = \pi_T \pi_Q \pi_E$  $\pi_{Process} = \pi_R \pi_S$  $\lambda_p = \lambda_b . \pi_T . \pi_Q . \pi_E . \pi_R . \pi_S$

where

$$\begin{split} \lambda_b & \text{is base failure rate.} \\ \pi_T & \text{is temperature factor} \\ \pi_Q & \text{is quality factor} \\ \pi_E & \text{is environmental factor} \\ \pi_R & \text{is current rating factor} \\ \pi_S & \text{is voltage stress factor} \\ \text{Used switch ratings:-} \\ \text{Junction temperature} &= 150^\circ \text{c} & \text{I}_{\text{rms}} = 30 \text{A} & \text{quality of product} = \text{JANTX} \\ \text{Case temperature} &= 75^\circ \text{c} & \text{V}_{\text{s}} = 500 \text{V} & \text{marine application} \\ \text{Substitute in (5)} \end{split}$$

$$\lambda_p = \lambda_b.\pi_T.\pi_Q.\pi_E.\pi_R.\pi_S$$

According to datasheet all values are having numerical values  $\lambda_b$  is base failure rate=0.002 (for all type devices same value)  $\pi_T$  is temperature factor=150°c

$$= e^{\left(-3082\left(\frac{1}{Tj+273} - \frac{1}{298}\right)\right)} = e^{\left(-3082\left(\frac{1}{150+273} - \frac{1}{298}\right)\right)} = 21$$

where Tj = junction temperature.

0°c temperature converted into Kelvin=273 At room temperature 25°c converted into Kelvin=273+25=298  $\pi_Q$  is quality factor =1.0  $\pi_E$  is environmental factor=N<sub>s</sub>=marine application=9.0  $\pi_R$  is current rating factor=30A  $= (i_{rms})^{0.40} = (30)^{0.40} = 3.9$   $\pi_S$  is voltage stress factor=500v=0.5  $= (V_S)^{1.9} = (0.5)^{1.9} = 0.27$

b)  $\lambda_p = \lambda_b . \pi_T . \pi_Q . \pi_E . \pi_R . \pi_S = 0.002 * 21 * 1.0 * 9.0 * 3.9 * 0.27 = 0.437$  failure/10<sup>6</sup> hours Failure rate for selected model switch (hardware) = 0.437 failured/10<sup>6</sup> hours Now,

Failure rate per year:-

The failure rate for each phase

$$\lambda_{physical} = \sum_{i}^{phase} \frac{annual time phase - i}{8760} * \lambda_{phase}$$

(5)

For 1- $\phi$  consider operation for 265 days= 265\*24=6360 hours 365 days= 365\*24=8760 hours Failure rate of the selected switch  $\lambda_{phase}$ =0.437 per 10<sup>6</sup> hours

$$\lambda_{physical} = \frac{6360}{8760} * 0.437 = 0.3712 \text{ per } 10^6 \text{ hours}$$

On-mission failure rate:-

On-mission failure rate

$$\lambda_{mission} = \lambda_{calander} * \frac{calander duration}{duration on-mission}$$

(6)

$$= 2* 365*24*10^{-9}* \frac{6760}{6360}$$

for 2 years

= 2.412\*10<sup>-5</sup> hours

Now this all values applied to the multilevel inverter switching operation its depends on the switch on condition in each level.

Switch1:- it conducts in 4 levels.

$$T_{conduction} = T_{total} - (T_{on} - T_{off})$$

$$T_{on} = 0.0985^* 10^{-6}$$

$$T_{off} = 0.005^* 10^{-6}$$

Total conduction period T<sub>conduction</sub> =2-(0.0985^\* 10^{-6} - 0.005^\* 10^{-6})

=1.9 sec

Total failure rate of the switch  $S_1=T_{conduction}$ \*no.of levels on-condition \*  $\lambda_p$ =1.9\*4\*0.437=0.003322w-sec

Total failure rate of the switch S<sub>2</sub>=T<sub>conduction</sub>\* no.of levels on-condition \*

$$\lambda_p$$

=1.9\*5\*0.437=0.0041515 w-sec

Total failure rate of the switch S<sub>3</sub>=  $T_{conduction}$  \* no.of levels on-condition \*  $\lambda_p$ =1.9\*5\*0.437=0.0041515 w-sec

Total failure rate of the switch S<sub>4</sub>=T<sub>conduction</sub> \* no.of levels on-condition \*  $\lambda_p$ =1.9\*5\*0.437=0.0041515 w-sec

Total failure rate of the switch  $S_5 = T_{conduction} * no.of$  levels on-condition  $* \lambda_p$ =1.9\*5\*0.437=0.0041515 w-sec

Total failure rate of the switch S<sub>6</sub>=T<sub>conduction</sub>\* no.of levels on-condition \*  $\lambda_p$ =1.9\*5\*0.437=0.0041515 w-sec

Total failure rate of the switch S<sub>7</sub>=  $T_{conduction}$  \* no.of levels on-condition \*  $\lambda_p$ =1.9\*5\*0.437=0.0041515 w-sec

Total failure rate of the switch S<sub>8</sub>=  $T_{conduction} *$  no.of levels on-condition \*  $\lambda_p$ =1.9\*4\*0.437=0.003322 w-sec

On-machine failure rate per year:- for 265 days 265\*24 = 6360 hours Switch 1, 8:-

$$\lambda_{physical} = \frac{6360}{8760} * 0.0033212 = 2.4112 * 10^{-3}$$

hours

Switch 2, 3, 4, 5, 6, 7:-

$$\lambda_{physical} = \frac{6360}{8760} * 0.0041515 = 3.0141 * 10^{-3}$$

hours

According to the manufactured material:-All switches are made of germanium material is a chemical element with symbol Ge and atomic number 32.  $S_1$ ,  $S_8$ =total loss\*material atomic number

$=2.4112*10^{-3}*32$ =0.0771per 10<sup>6</sup> hours

$\begin{array}{l} S_2,\,S_3,\,S_4,\,S_5,\,S_6,\,S_7 = total \; loss*material \; atomic\; number \\ = 3.0141^*10^{-3}*32 \\ = 0.0964\; per\; 10^6\; hours \end{array}$

## 5. CONCLUSION

The cost of the proposed multilevel inverter quite lesser compared with the conventional multilevel inverter topology and the number of dc sources and switches also less for same level of output voltage generation. Reliability analysis has been performed towards the proposed multilevel inverter based on the mean time failure with various equations given in the FEDI reliability mathematical modeling design the results of the proposed multilevel inverter is having lesser failure rate and it is good for fewer chances of failure for medium voltage high power applications.

Mathematical analysis of cost function and reliability condition for new proposed ... (D. Karthikeyan)

#### REFERENCES

- L. Maharjan, S. Inoue, H. Akagi, and J. Asakura, "State-of-charge (SOC)-balancing control of a battery energy storage system based on a cascade PWM converte," in *IEEE Transactions on Power Electronics*, vol. 24, no. 6, pp. 1628-1636, 2009.

- [2] K. Himour, K. Ghedamsi, and E. M. Berkouk, "Supervision and control of grid connected PV-Storage systems with the five level diode clamped inverter," *Energy Conversion and Management*, vol. 77, pp. 98-107, 2013

- [3] Escalante, Miguel F., J-C. Vannier, and Amir Arzandé, "Flying capacitor multilevel inverters and DTC motor drive applications," in *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 809-815, 2002.

- [4] K. Ramani, M. A. J. Sathik, and S. Sivakumar, "A new symmetric multilevel inverter topology using single and double source sub-multilevel inverters," *Journal of Power Electronics*, vol. 15, no. 1, pp. 96-105, 2015.

- [5] A. Mokhberdoran, and Ali Ajami. "Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology," in *IEEE Transactions on Power Electronics*, vol. 29, no. 12, pp. 6712-6724, 2014.

- [6] R. S. Alishah, S. H. Hosseini, E. Babaei, M. Sabahi, "Optimal Design of New Cascaded Switch-Ladder Multilevel Inverter Structure," in *IEEE Transactions on Industrial Electronics*, vol. 64, no. 3, pp. 2072-2080, 2017.

- [7] R. Samanbakhsh and A. Taheri, "Reduction of Power Electronic Components in Multilevel Converters Using New Switched Capacitor-Diode Structure," in *IEEE Transactions on Industrial Electronics*, vol. 63, no. 11, pp. 7204-7214, 2016.

- [8] Z. Du, L. M. Tolbert, J. N. Chiasson, and B. Ozpineci, "A cascaded multilevel inverter using a single dc source," *Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition*, 2006. APEC '06, Dallas, TX, p. 5, 2006.

- [9] R. Shalchi Alishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Novel topologies for symmetric, asymmetric and cascade switched-diode multilevel converter with minimum number of power electronic components," in *IEEE Transactions on Industrial Electronics*, vol. 61, no. 10, pp. 5300-5310, 2014.

- [10] J. M. Carrasco, et al., "Power-electronic systems for the grid integration of renewable energy sources: A survey," in *IEEE Transactions on Industrial Electronics*, vol. 53, no. 4, pp. 1002-1016, 2006.

- [11] P. Palanivel and S. S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques," in *IET Power Electronics*, vol. 4, no. 8, pp. 951-958, 2011.

- [12] A. M. Massoud, S. J. Finney, and B. W. Williams, "Control Techniques for Multilevel Voltage Source Inverters," *IEEE 34th Annual Conference on Power Electronics Specialist, 2003. PESC '03., Acapulco*, Mexico, vol. 1, pp. 171-176, 2003.

- [13] R. Gupta, A. Ghosh, and A. Joshi, "Switching characterization of cascaded multilevel inverter controlled systems." in *IEEE Transactions on Industrial Electronics*, vol. 55, no. 3, pp. 1047-1058, 2008.

- [14] J. Ebrahimi, E. Babaei, and G.B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," in *IEEE Transactions on Industrial Electronics*, vol. 59, no. 2, pp. 655-667, 2012.

- [15] Haji-Esmaeili M. M., Naseri M., Khounjahan H., Abapour M., "Fault tolerant structure for cascaded H-bridge multilevel inverter and reliability evaluation," in *IET Power Electronics*, vol. 10, no. 1, pp. 59-70, 2017.

- [16] Catelani M., Ciani L., Luchetta A., Manetti S., Piccirilli M. C., Reatti A, Kazimierczuk M. K., "Fault detection of resonant inverters for wireless power transmission using MLMVNN," 2016 IEEE 2nd International Forum on Research and Technologies for Society and Industry Leveraging a better tomorrow (RTSI), Bologna, pp. 1-5, 2016.

- [17] Haji-Esmaeili M. M., Naseri M., Khounjahan H., Abapour M., "Fault-tolerant and reliable structure for a cascaded quasi Z source DC-DC converter," in IEEE Transactions on Power Electronics, vol. 32, no. 8, pp. 6455-6467, 2017.

- [18] Luh D. D., Soon J. L., Verstraete D., "Derivation of dual-switch step-down DC/DC converters with fault-tolerant capability," in *IEEE Transactions on Power Electronics*, vol. 31, no. 9, pp. 6064-6068, 2016.

- [19] Jamshidpour E., Poure P., Saadate S., "Photovoltaic systems reliability improvement by real-time FPGA-based switch failure diagnosis and fault-tolerant DC-DC converter," in *IEEE Transactions on Industrial Electronics*, vol. 62, no. 11, pp. 7247-7255, 2015.

- [20] Catelani M., Ciani L., Luchetta A., Manetti S., Piccirilli M. C., Reatti A., Kazimierczuk M. K., "MLMVNN for parameter fault detection in PWM DC-DC converters and its applications for Buck DC-DC converter," 2016 IEEE 16th International Conference on Environment and Electrical Engineering (EEEIC), Florence, pp. 1-6, 2016.

- [21] Baldanzi I., Catelani M., Ciani L., Kazimierczuk M. K., Luchetta A., Manetti S., Reatti A., "MLMVNN for parameter faults detection in a DC-DC boost converter," *XXI IMEKO World Congress on "Measurement in Research and Industry*, Prague, Czech Republic, 2015.

- [22] Siwakoti Y. P., Peng F. Z., Blaabjerg F., Loh P. C., Town G. E., "Impedance-source networks for electric power conversion part I: a topological review," in *IEEE Transactions on Power Electronics*, vol. 30, no. 2, pp. 699-716, 2015.

- [23] Siwakoti Y. P., Peng F. Z., Blaabjerg F., Loh P. C., Town G. E., Yang S., "Impedance-source networks for electric power conversion part II: review of control and modulation techniques," in *IEEE Transactions on Power Electronics*, vol. 30, no. 4, pp. 1887-1906, 2015.

- [24] Mouna Es-Saadi, Mohamed Khafallah, Hamid Chaikhy, "Using the Five-Level NPC Inverter to Improve the FOC Control of the Asynchronous Machine," *International Journal of Power Electronics and Drive System (IJPEDS)*, vol. 9, no. 4, pp. 1457-1466, 2018.

- [25] V. S. Prasadarao K., V. Joshi Manohar, "Grid Interconnection of PV System Using Symmetric and Asymmetric MLI Topology," *International Journal of Power Electronics and Drive System (IJPEDS)*, vol. 9, no. 4, pp. 1616-1623, 2018.

- [26] K. Rajasekhara Reddy, V. Nagabhaskar Reddy, M. Vijaya Kumar, "Control of Single Stage Grid Tied Photovoltaic Inverter Using Incremental Conductance Method," *International Journal of Power Electronics and Drive System* (*IJPEDS*), vol. 9, no. 4, pp. 1702-1708, 2018.

- [27] Tarek Selmi, Maher Rezgui, "A Novel DC-AC Inverter Topology to Eliminate Leakage Current," *International Journal of Power Electronics and Drive System (IJPEDS)*, vol. 9, no. 4, pp. 1733-1744, 2018.

**G** 661

## **BIOGRAPHIES OF AUTHORS**

**D** Karthikeyan received his B.E. degree from the Department of Electrical and Electronics Engineering of A. I. H. T College, Chennai, India (affiliated with Anna University, Chennai, India), in 2009;and his M.Tech. degree in Power Electronics and Drives from SRMIST (Formerly SRM University), Kattankulathur, India, in 2013, where he had completed his Ph.D. degree in Multilevel Inverters (2019). He is presently working as Assistant Professor in the Department of Electrical Engineering SRMIST (Formerly SRM University), Kattankulathur and Chennai, India. His current research interests include power electronic multilevel inverters, AC drives and DC drives.He is a Member of various professional societies such as the IEEE, IEI and ISCA.

**Vijayakumar Krishnaswamy** received his B. E. and M. E. degrees from Annamalai University, Annamalai Nagar, India; and his Ph.D. degree from SRMIST (Formerly SRM University), Kattankulathur, India. He is presently working as a Professor and as the Head of the Department of Electrical and Electronics Engineering of SRMIST (Formerly SRM University). His current research interests include power system modeling, power electronics converters for grid connected PV systems, computational intelligence applications in power systems, FACTS devices and power quality. He has been awarded a Best Teacher Award in hisdepartment for the academic years 2004 and 2006. He is a Member of various professional societies such as the IEEE, IET,FIE, ISTE and ISCA.

**D** Senthil Kumar received his B.Tech. degree in the Department of Information Technology from Anjalai Ammal Mahalingam Engineering College, Thiruvarur, India (affiliated with Anna University, Chennai, India), in 2012; and his M.E. degree in Software Engineering from Jerusalem College of Engineering, Chennai, India, in 2014. He is presently working as Teaching Associate in the Department of Computer Science and Engineering, SRMIST (Formerly SRM University), Kattankulathur and Chennai, India. He is a Member of various professional societies such as the IRED, IAENG and ISCA.

**Daki.Krishnachaitanya** recived his M.Tech degree in Power Electronics and Drives from SRMIST (Formerly SRM University), Kattankulathur, India, in the year 2018, he is presently working as research scholor in the Department of EEE at vellore institute of technology vellore tamilnadu his area of intrest is Power Electronics, Drives & Multilevel Inverter. He is a Member of various professional societies such as the IRED, IAENG and ISCA