# Recent advances in phase-locked loop based synchronization methods for inverter-based renewable energy sources

# Haval Sardar Kamil<sup>1</sup>, Dalila Mat Said<sup>2</sup>, Mohd Wazir Mustafa<sup>3</sup>, Mohammad Reza Miveh<sup>4</sup>, Nasarudin Ahmad<sup>5</sup>

<sup>1,2</sup>Centre of Electrical Energy Systems (CEES), Universiti Teknologi Malaysia (UTM), Malaysia

<sup>1,2,3,5</sup>School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia (UTM), Malaysia

<sup>4</sup>Department of Electrical Engineering, Tafresh University, Iran

# Article Info

# ABSTRACT

| Article history:                                                                                          | Recently, researchers have shown an increased interest in renewable energy sources (RESs) to improve power quality, reliability and stability of the power                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Received Jul 10, 2019<br>Revised Sep 10, 2019<br>Accepted Oct 22, 2019                                    | sources (REDS) to improve power quarty, remainly and stability of the power<br>system. However, RESs require proper control strategies to ride through grid<br>disturbances and stay connected to the main grid for the stability contribution.<br>Moreover, the control of them relies mainly on the synchronization algorithms<br>to precisely detect the voltage phase angle, magnitude and frequency.                                                   |  |  |  |  |

| Keywords:                                                                                                 | Throughout the years, various synchronization schemes have been introduced<br>and developed. In the renewable-based generation sources, the phase-locked                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Grid-tied converters<br>Phase-locked loop (PLL)<br>Renewable energy sources<br>Synchronization algorithms | loop (PLL) is a well-known technique for operating grid-tied power converters<br>for the estimation of the synchronization information and grid voltage<br>monitoring. This paper aims to provide a comprehensive review of the recently<br>developed PLL algorithms for grid synchronization applications. At first,<br>various estimation techniques are discussed. Then, a comparison between<br>various PLLs and possible future works are recommended. |  |  |  |  |

|                                                                                                           | Copyright © 2020 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Corresponding Author:                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

Dalila Mat Said, Centre of Electrical Energy Systems (CEES), School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia (UTM), Johor Bahru 81310, Johor, Malaysia. Email: dalila@utm.my

# 1. INTRODUCTION

In recent years, the use of renewable energy sources (RESs) has remarkably increased and they are currently becoming a popular option to replace the dependency on fossil fuels for the effort to achieve the sustainable development [1, 2]. Therefore, it is needed to integrate more RESs in the power system to provide economic and environmental advantages [3]. However, the increasing penetration of RESs is required power electronic-based grid side converters to ease the smooth, reliable and efficient integration with he power system.

Increasing penetration of RESs may deteriorate the reliability, stability and power quality of the power grid. So that, these renewable sources must ride-through all disturbances efficiently and become in synchronism with the power system. The interaction of these RESs over the power converter with the grid or among various converters are followed with the process called synchronization. Moreover, to attain the grid synchronization between the power converters output voltages and the main grid voltages at the point of common coupling (PCC), it is substantial to have precise information regarding the grid voltage fundamental components such as phase angle, magnitude and frequency.

The most well-known synchronization method is based on phase-locked loop (PLL) for advantages such as robustness, simplicity and effectiveness. However, voltage sags, swell, harmonics, voltage unbalance

and DC offset in the voltage have negative impacts and affect the tracking ability of the PLL for accurate fundamental grid voltage phase angle. For this reason, a continuous attempt of improvement and development of the existing PLL schemes is taking place to fulfill reliable operation with better stability and faster synchronization without the large computational overhead. In recent years, many papers have introduced various PLL schemes such as synchronous reference frame PLL (SRF-PLL), dual second-order generalized integrator PLL (DSOGI-PLL), double synchronous reference frame PLL (DSRF-PLL), and enhanced PLL (EPLL) [4, 5]. Table 1 illustrates the comparison of the selected PLL algorithms with their strong and weak sides.

| Synchronization algorithm | Advantage-side                   | Limitation-side                    |

|---------------------------|----------------------------------|------------------------------------|

| SRF-PLL                   | -Simple implementation           | -Harmonics                         |

|                           | -Stability                       | -Phase Jump                        |

|                           | -DC offset                       | -Voltage unbalances                |

|                           | -Low computational burden        | -Load rising                       |

|                           | -Fast dynamic response           | -Frequency rising and overshoot    |

|                           | -Voltage unbalance               |                                    |

|                           | -Load rising                     |                                    |

| DDSRF-PLL                 | -Harmonics                       | -Frequency rising and overshoot    |

|                           | -DC offset                       | -Average implementation simplicity |

|                           | -Stability                       |                                    |

|                           | -Phase jumping                   |                                    |

|                           | -Low computational burden        |                                    |

| DSOGI-PLL                 | -Voltage unbalance               | -Harmonic                          |

|                           | -Frequency rising and variations | -Average implementation simplicity |

|                           | -Phase jumping                   | -Load rising                       |

|                           | -DC offset                       | -High computational burden         |

|                           | -Stability                       | Ingii computational burden         |

|                           | -Fast dynamic response           |                                    |

|                           | -Harmonics                       | -Load rising                       |

| EPLL                      | -DC offset                       | -Average implementation simplicity |

|                           | -Phase jumping                   | -Frequency rising and variations   |

|                           | -Stability                       | -Voltage unbalances                |

|                           |                                  | -Slow dynamic response             |

| Table 1. Performance com | parisons of | some PLL s | vnchronization schemes |

|--------------------------|-------------|------------|------------------------|

|                          |             |            |                        |

This paper introduces a thorough survey on the most relevant and applicable PLL synchronization strategies to facilitate the appropriate selection for most desirable applications and letting know the research community and engineers their advantages and limitations. The rest of the paper is organized as follows. In section 2, grid synchronization methods during faulty conditions are introduced. Section 3 summarizes PLL in detail as well as several PLL algorithms along with their specific block diagrams and equations. Sections 4 concludes the paper with the recommendation for future works.

# 2. GRID SYNCHRONIZATION METHODS DURING FAULTY CONDITIONS

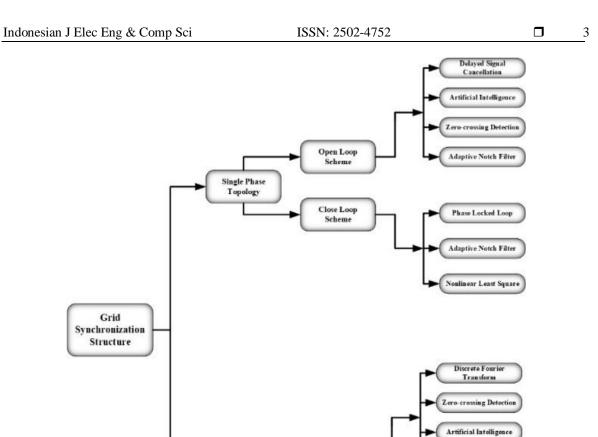

In recent years, the rapid proliferation of distributed generation (DG) in the power system has given rise to the proposal of various synchronization schemes for grid-connected converter (GCC) applications. They can be classified into two categories, the open-loop and closed-loop approaches as depicted in Figure 1. The zero-crossing detection method [6-8], adaptive notch filtering [9, 10], artificial intelligence [11, 12], nonlinear least square [13], discrete Fourier transform [14], delayed signal cancellation [15, 16], and Kalman filter [17] are the common examples of the open-loop category. On the other hand, the PLL method, SRF-PLL [18, 19], EPLL [20], and SOGI-PLL [21] are the main examples of the closed-loop category. Most of the proposed methods have very good behavior, when the grid voltage is symmetrical; although, find it crucial to accurately estimate the grid voltage angle under distorted voltages or particularly under asymmetrical grid faults. In this paper, despite the importance of the open-loop methods, however, the concentration on phase-locked loop synchronization technology taking into account as PLL techniques are most popular due their accuracy and robustness.

Open Loop Scheme

Close Loop Scheme Kalman Filte

Phase Locked Loop

Frequency Locked Loo

Adaptive Notch Filter Delayed Signal Cancellation

Figure 1. Different grid synchronization methods

#### 3. OVERVIEW OF PHASE-LOCKED LOOP SYNCHRONIZATION TECHNOLOGY

Three Phase

Topology

PLL is an old technology since its concept first came into publishing by Bellescise in 1932 [22]. Moreover, it has been applied in an expansive range of applications such as communications, instrumentation, control schemes and many other methods. The basic schematic block diagram of PLL can be described by the three basic elements as shown in Figure 2, where the difference between the phase angle of the input and the output signal is measured by the phase detection (PD) and passed through the loop filter (LF) for phase error elimination. The LF output signal drives the voltage-controlled oscillator (VCO) to generate the output phase, which could follow the input signal. Furthermore, to enhance the PLL performance in different grid conditions, various modifications and improvements have been made such as SRF-PLL, decoupled double synchronous reference frame PLL (DDSRF-PLL), EPLL and SOGI-PLL are among these development schemes. The difference among these strategies usually lies in how the PD block is implemented. In the following subsections, some of them has discussed in detail.

Figure 2. Schematic diagram of a PLL

Recent advances in phase-locked loop based synchronization methods for inverter ... (Haval Sardar Kamil)

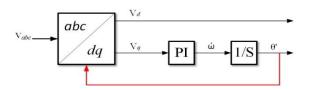

#### 3.1. SRF-PLL Algorithm

The synchronous reference frame PLL is considered a fundamental PLL, and different advanced PLLs are built upon the Clarke and Park transformations, which converts the natural abc reference frame into the synchronous reference frame. Additionally, the proportional integrator (PI) is then applied to control the q variables and the output of the PI controller is the grid frequency. Moreover, the utility phase angle is attained by integrating this grid frequency, which is then fed back into the PD ( $\alpha\beta$ -dq transformation). Many works have been presented the SRF-PLL algorithm that is used in three-phase grid-connected power converters due to implementation simplicity and fast and accurate estimation of the phase/frequency in typical grid conditions. Figure 3 illustrates the SRF-PLL structure. As mentioned earlier, since the SRF is rotating with the positive angular speed; hence, the conventional SRF-PLL allows fast and accurate estimation of the phase angle and grid-voltage frequency in ideal situations and works properly under balanced grid faults conditions. On the other hand, it fails to track the phase angle, when an unbalanced fault takes place. This is due to the consequence of the presence of twice-grid frequency ( $2\omega$ ) fluctuations which induced by the negative sequence components that disturb the *dq*-components appearing in the mismatch of V<sub>d</sub> from the positive sequence magnitude [23]. In addition, the SRF-PLL cannot properly work under harmonically distorted voltages.

Figure 3. The structure of the synchronous reference frame PLL

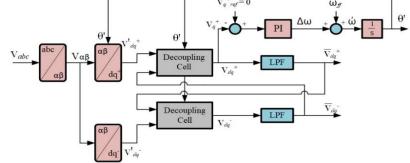

# 3.2. DDSRF-PLL Algorithm

Under unbalanced grid conditions, the performance of SRF-PLL is inaccurate, which leads the loop filter being incapable to abolish harmonic contents occurrence. Using two different reference systems are essential, as the algorithm that expresses grid voltage vector through its direct and inverse sequence components using double synchronous reference frame is called DDSRF-PLL, which the coupling effect between the positive and negative sequences of the voltage is decoupled subsequently [24]. As can be seen in (1) and (2), the transformed voltage vectors consist of DC values and oscillation ( $2\omega$ ) values. The DDSRF-PLL is implemented by converting the grid voltage into positive and negative synchronous reference frames, as shown in Figure 4.

Even though this method can completely remove estimation errors in conventional SRF-PLL, the estimation process is quite complex and sensitive to the phase-angle jump of the grid voltage. The theoretical basis of the DDSRF-PLL with its decoupling network model (Figure 4) is explained below. As a consequence of the decoupling process, the DDSRF-PLL assures a satisfactory operation under unbalanced grid faults.

$$v_{dq}^{-1} = \begin{bmatrix} v_{d}^{-1} \\ v_{q}^{-1} \end{bmatrix} = \begin{bmatrix} T_{dq}^{-1} \end{bmatrix} \cdot v_{a\beta} = v^{+1} \begin{bmatrix} \cos(2\omega t) \\ \sin(2\omega t) \end{bmatrix} + v^{-1} \begin{bmatrix} 1 \\ 0 \end{bmatrix}$$

(1)

Figure 4. Block diagram of the DDSRF-PLL

$v_{dq}^{+1} = \begin{bmatrix} v_d^{+1} \\ v_{q}^{+1} \end{bmatrix} = \begin{bmatrix} T_{dq}^{+1} \end{bmatrix} \cdot v_{\alpha\beta} = v^{+1} \begin{bmatrix} 1 \\ 0 \end{bmatrix} + v^{-1} \begin{bmatrix} \cos(-2\omega t) \\ \sin(-2\omega t) \end{bmatrix}$ (2)

ISSN: 2502-4752

where

$$\begin{bmatrix} T_{dq}^{+1} \end{bmatrix} = \begin{bmatrix} T_{dq}^{-1} \end{bmatrix} = \begin{pmatrix} \cos(\theta') & \sin(\theta') \\ -\sin(\theta') & \cos(\theta') \end{pmatrix}$$

(3)

However, for extracting direct sequence grid voltage vector, cross-feedback decoupling network is needed along with the low pass filter (LPF). LPF block is usually selected with first-order transfer function presented in (4):

$$LPF(s) = \frac{\omega_f}{s + \omega_f} \tag{4}$$

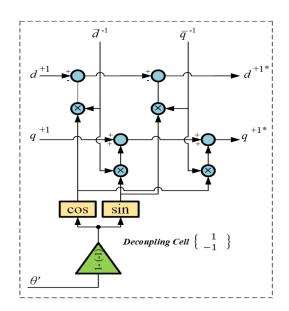

where  $\omega_f$  presents LPF's cut-off frequency. With refer to [23], to secure a stable response of the PLL, the ratio of cut-off frequency and fundamental grid frequency has to be below  $(1/\sqrt{2})$ . The demonstration of decoupling network for direct sequence is presented in Figure 5.

Figure 5. Block diagram of the decoupling cell [23]

#### 3.3. DSOGI-PLL Algorithm

A solution to surpassing issues caused by the voltage unbalances to the phase angle detection can be achieved by proposing a DSOGI-PLL [23]. Basically, DSOGI-PLL has designed in the stationary reference frame basis on instantaneous synchronous technique [25, 26]. In addition, the SOGI converts the input voltages as seen in (5), into an in-phase and a quadrature signal in the  $\alpha\beta$  reference frame. The strategy uses a LPF together with a bandpass filter (BPF), to take care of the harmonic filtering as well as handle the in-quadrature signals (90° shifted) for  $V_{\alpha\beta}$  which computed by two SOGI with a quadrature signal generation (SOGI-QSG) [27]. The block diagram of SOGI, which behaves as an integrator with infinite gain and its transfer functions is described in Figure 6. As seen in (6) and (7), the transfer function of the SOGI's LPF and BPF can be derived from the block diagram as:

$$SOGI(s) = \frac{v'}{k\varepsilon_v}(s) = \frac{s}{s^2 + {\omega'}^2}$$

(5)

Recent advances in phase-locked loop based synchronization methods for inverter ... (Haval Sardar Kamil)

$$BPF(s) = \frac{v'}{v}(s) = \frac{ks}{s^2 + ks + \omega'^2}$$

(6)

$$LPF(s) = \frac{qv'}{v}(s) = \frac{k\omega'^2}{s^2 + ks + \omega'^2}$$

$$V + V + V + V'$$

(7)

Figure 6. Block diagram of second order generalized integrator (SOGI)

SOGI

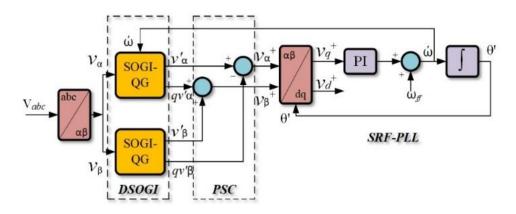

Direct voltage sequence in  $\alpha\beta$ -frame is extracted by applying two SOGIs based on a quadrature generation (QG), which acts as an adaptive band-pass filter along with Positive-Sequence Calculator (PSC). The Block diagram of complete DSOGI-PLL is shown in Figure 7. When the positive sequence voltage vector is obtained, the *q*-component is forced to zero. Consequently, in order to adapt the center frequency of the DSOGI, the estimated frequency is fed back to the SOGI-QG block. Moreover, the DSOGI-PLL performs an accurate phase angle estimation under unbalanced grid fault conditions, unless it results in large frequency-overshoots and slow dynamics as well.

Figure 7. Schematic block diagram of quadrature generation based DSOGI-PLL

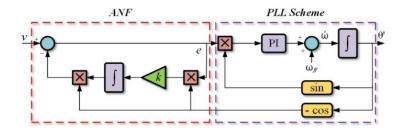

#### 3.4. EPLL Algorithm

Fundamentally, the enhanced PLL algorithm is a frequency-adaptive nonlinear synchronization method, its major difference with the existing PLL schemes is to grant more resilience and offer more information to track the frequency, phase angle and magnitude of three-phase input systems [20]. The concept that EPLL basis on the extraction of the positive sequence component of an input signal through a BPF. Furthermore, it is well-known that the impact of the nonideal grid situations, such as noise, unbalance, harmonics, and also the DC offset on the EPLL must be eliminated to assure that it is capable to implement in the utility supply voltage. EPLL is also applied with unified power-quality conditioner (UPQC) to control its voltage source converters (VSCs). When tested in the presence of voltage sags and harmonics on an Electromagnetic Transients DC analysis program, the UPQC was capable to extract the reference signals quickly and directly for the supply voltage and the load current. Introduction of the LPF after the integrator block in the VCO can result in a smoother estimate of phase angle under distorted utility grid conditions [6]. The schematic block diagram of EPLL is depicted in Figure 8. As can be seen that the K parameter is controlling the dynamic response of the phase-locked loop by affecting the speed of convergence of the peak value

estimation loop. Moreover, EPLL can provide the  $90^{\circ}$  shift of the input signal. Thus, it is an attractive solution in some single-phase system implementations.

Figure 8. Block diagram of EPLL

### 4. CONCLUTION AND FUTURE RECOMMENDATIONS

This paper provides a comprehensive review of several state-of-the-art PLL synchronization algorithms than can be applied as a benchmark for the appropriate control of the grid-tied RESs. From the existing literature, it can be clarified that many modifications have been made in the past couple of years for enhancing PLL performance to dismiss any adverse grid conditions. A detailed implementation analysis regarding operating principals, schematic diagram and performance ability has been carried out. Furthermore, as the grid voltage disturbances affecting the capability of synchronization algorithms to accurately estimate the phase angle, hence, this work highlighted the significant characteristics and detailed comparisons of popular PLL synchronization methods performance under different causes of unbalanced conditions. In addition, for the future recommendation, developing effective techniques for frequency deviation and phase angle detection for efficient dynamic performance under severe voltage conditions and harmonics is highly required. Correspondingly, initiating artificial intelligence methods in hybrid with the conventional schemes for grid-tied power converters can be paid more attention in the future researches.

#### ACKNOWLEDGEMENTS

The authors would like to acknowledge the support of the Ministry of Education, Malaysia and Universiti Teknologi Malaysia through research grants 07G53 and 03G88.

#### REFERENCES

- [1] H. S. Kamil, D. M. Said, M. W. Mustafa, M. R. Miveh, and N. Ahmad, "Low-voltage Ride-through Methods for Gridconnected Photovoltaic Systems in Microgrids: A Review and Future Prospect," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 9, no. 4, p. 1834, 2018.

- [2] H. S. Kamil, D. M. Said, M. W. Mustafa, M. R. Miveh, and N. Ahmad, "Low-voltage ride-through for a three-phase four-leg photovoltaic system using SRFPI control strategy," *International Journal of Electrical and Computer Engineering*, vol. 9, no. 3, p. 1524, 2019.

- [3] H. S. Kamil, D. M. Said, M. W. Mustafa, M. R. Miveh, and S. M. Hussin, "Control Strategy for a Three-Phase Fourleg Grid Connected PV Inverter under Unbalanced Faults," in 2018 IEEE 7th International Conference on Power and Energy (PECon), 2018, pp. 13-18: IEEE.

- [4] Z. Ali, N. Christofides, L. Hadjidemetriou, E. Kyriakides, Y. Yang, and F. Blaabjerg, "Three-phase phase-locked loop synchronization algorithms for grid-connected renewable energy systems: A review," *Renewable and Sustainable Energy Reviews*, vol. 90, pp. 434-452, 2018.

- [5] N. Jaalam, N. Rahim, A. Bakar, C. Tan, and A. M. Haidar, "A comprehensive review of synchronization methods for grid-connected converters of renewable energy source," *Renewable and Sustainable Energy Reviews*, vol. 59, pp. 1471-1481, 2016.

- [6] O. Vainio and S. J. Ovaska, "Noise reduction in zero crossing detection by predictive digital filtering," *IEEE Transactions on Industrial Electronics*, vol. 42, no. 1, pp. 58-62, 1995.

- [7] O. Vainio, S. J. Ovaska, and M. Polla, "Adaptive filtering using multiplicative general parameters for zero-crossing detection," *IEEE Transactions on Industrial Electronics*, vol. 50, no. 6, pp. 1340-1342, 2003.

- [8] M. A. Pérez, J. R. Espinoza, L. A. Morán, M. A. Torres, and E. A. Araya, "A robust phase-locked loop algorithm to synchronize static-power converters with polluted AC systems," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 5, pp. 2185-2192, 2008.

- [9] D. Yazdani, A. Bakhshai, G. Joós, and M. Mojiri, "A real-time extraction of harmonic and reactive current in a nonlinear load for grid-connected converters," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 6, pp. 2185-2189, 2009.

Recent advances in phase-locked loop based synchronization methods for inverter ... (Haval Sardar Kamil)

- 8 🗖

- [10] G. Yin, L. Guo, and X. Li, "An amplitude adaptive notch filter for grid signal processing," *IEEE Transactions on Power Electronics*, vol. 28, no. 6, pp. 2638-2641, 2012.

- [11] G. W. Chang, C.-I. Chen, and Y.-F. Teng, "Radial-basis-function-based neural network for harmonic detection," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 6, pp. 2171-2179, 2009.

- [12] A. Bouknadel, N. Ikken, A. Haddou, N.-E. Tariba, H. E. Omari, and H. E. Omari, "A new SOGI-PLL method based on fuzzy logic for grid connected PV inverter," *International Journal of Electrical & Computer Engineering* (*IJECCE*), (2088-8708), vol. 9, 2019.

- [13] G. Simon, R. Pintelon, L. Sujbert, and J. Schoukens, "An efficient nonlinear least square multisine fitting algorithm," *IEEE Transactions on Instrumentation and Measurement*, vol. 51, no. 4, pp. 750-755, 2002.

- [14] B. C. Babu, K. Sridharan, E. Rosolowski, and Z. Leonowicz, "Analysis of SDFT based phase detection system for grid synchronization of distributed generation systems," *Engineering Science and Technology, an International Journal*, vol. 17, no. 4, pp. 270-278, 2014.

- [15] Y. F. Wang and Y. W. Li, "Three-phase cascaded delayed signal cancellation PLL for fast selective harmonic detection," *IEEE Transactions on industrial electronics*, vol. 60, no. 4, pp. 1452-1463, 2011.

- [16] Y. F. Wang and Y. W. Li, "Analysis and digital implementation of cascaded delayed-signal-cancellation PLL," *IEEE Transactions on Power Electronics*, vol. 26, no. 4, pp. 1067-1080, 2010.

- [17] P. K. Dash, R. Jena, G. Panda, and A. Routray, "An extended complex Kalman filter for frequency measurement of distorted signals," *IEEE Transactions on Instrumentation and Measurement*, vol. 49, no. 4, pp. 746-753, 2000.

- [18] M. Reyes, P. Rodriguez, S. Vazquez, A. Luna, R. Teodorescu, and J. M. Carrasco, "Enhanced decoupled double synchronous reference frame current controller for unbalanced grid-voltage conditions," *IEEE Transactions on power electronics*, vol. 27, no. 9, pp. 3934-3943, 2012.

- [19] F. González-Espín, E. Figueres, and G. Garcerá, "An adaptive synchronous-reference-frame phase-locked loop for power quality improvement in a polluted utility grid," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 6, pp. 2718-2731, 2011.

- [20] M. Karimi-Ghartemani et al., "A new phase-locked loop system for three-phase applications," IEEE Transactions on Power Electronics, vol. 28, no. 3, pp. 1208-1218, 2012.

- [21] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Dynamics assessment of advanced single-phase PLL structures," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 6, pp. 2167-2177, 2012.

- [22] H. de Bellescize, "La reception synchrone". E. Chiron, 1932.

- [23] R. Teodorescu, M. Liserre, and P. Rodriguez, "Grid converters for photovoltaic and wind power systems". *John Wiley & Sons*, 2011.

- [24] F. Filipović, B. Banković, M. Petronijević, N. Mitrović, and V. Kostić, "Benchmarking of phase lock loop based synchronization algorithms for grid-tied inverter," *Serbian Journal of Electrical Engineering*, vol. 16, no. 1, pp. 1-19, 2019.

- [25] S. Golestan, M. Monfared, and F. D. Freijedo, "Design-oriented study of advanced synchronous reference frame phase-locked loops," *IEEE Transactions on Power Electronics*, vol. 28, no. 2, pp. 765-778, 2012.

- [26] P. Rodriguez, R. Teodorescu, I. Candela, A. V. Timbus, M. Liserre, and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," in 2006 37th IEEE Power Electronics Specialists Conference, 2006, pp. 1-7: IEEE.

- [27] Rodriguez, A. Luna, M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "Advanced grid synchronization system for power converters under unbalanced and distorted operating conditions," in IECON 2006-32nd Annual Conference on IEEE Industrial Electronics, 2006, pp. 5173-5178: IEEE.