# Estimation of power and delay in CMOS circuits using LCT

Aylapogu Pramod Kumar, B.L.V.S.S Aditya, G. Sony, Ch. Prasanna, A. Satish Department of Electronics & Communication Engineering, Lendi Institute of Engineering and Technology,

JNTUK Vizianagaram (A.P.), India

### **Article Info**

#### Article history:

Received Sep 23, 2018 Revised Dec 27, 2018 Accepted Jan 15, 2019

#### Keywords:

CMOS HTLCT IC LCT Leakage current Power dissipation Time delay VLSI

# ABSTRACT

With a rapid growth in semiconductor Industry, complex applications are being implemented using small size chips, with the use of Complementary Metal Oxide Semi-Conductors (CMOS). With the introduction of new Integrated Circuit (IC) technology, the speed of the circuits has been increased by around 30%. But it was observed that for every two years, the power dissipation of a circuit doubles. The main reason for this power dissipation is leakage currents in the circuit. To reduce these leakage currents, we can reduce the width of the device. In addition to this, we can use lector techniques that use Leakage Control Transistors (LCT) and High Threshold Leakage Control Transistors (HTLCT). In this paper; we present a circuit technique that uses 130 nano-meter CMOS VLSI circuits that use two extra transistors to mitigate the leakage currents. The proposed technique overcomes the limitations posed by the existing methods for leakage reductions an average leakage reductions is 82.5%. The estimation of power and delay will be discussed using LCT's and HTLCT's.

> Copyright © 2019 Institute of Advanced Engineering and Science. All rights reserved.

# **Corresponding Author:**

Aylapogu Pramod Kumar, Department of Electronics & Communication Engineering, Lendi Institute of Engineering and Technology, JNTUK, Vizianagaram (A.P.), India. Email: pramodkumar.a@lendi.org

# 1. INTRODUCTION

As the impact of electronic systems on every walk of life is becoming more and more, the demand for very low cost, very small and very reliable systems is also increasing exponentially. The rapid development of the semiconductor technology is leading to very tiny systems that have the power of supercomputers of the last decade. Designing such tiny systems is now being witnessed in every field mobile communications, industrial electronics and ubiquitouscomputing. Electronic circuits are characterized by reliability, low power dissipation, extremely low weight and volume and effective cost with a high degree of computations and complexities. The advancements in technology mainly contributed towards the miniature in transistor size, reduced power supply consumption and enhancement of services with reliability as a major factor.VLSI Technology has been the enabler for the advancement of the present electronics and communication age. Almost 90% of the electronic circuits fabricated worldwide are made of silicon using CMOS technology [1]-[2]. For relatively high performance and cost-effective [3] VLSI circuits, CMOS technology is used. It is the most popular technology because of its low power and less area requirement [4]. Scaling of CMOS technology improved the speed however the leakage currents [5] are leftover as an adverse effect. These unsolicited leakage currents should be reduced for the smooth functioning of the circuits. LECTOR Technique [6-8] is the technique to reduce leakage power consumption[9] in CMOS circuits without affecting the dynamic power [10]-[11] of the circuit. In this paper, the performance of parallel addersubtractor implemented with NAND gates using LECTOR technique is compared to the basic model and power dissipation and delay are compared.

991

# **1.1.** Conventional Principles and Techniques

## 1.1.1 Nand Gate

The fundamental building blocks of digital systems are logic gates. They are circuits in which the output depends upon the inputs according to the logic rules. The electronic circuits that operate on one or more input signals to produce an output signal are known as logic gates.

The NAND gate is called a Universal gate because it can perform all the three basic functions of AND, OR, NOT gates. The NAND gate is a AND gate followed by NOT gate. It is a NOT- AND operation. It may have two or more inputs but only one output.

The logical symbol of NAND gate

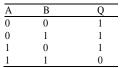

The truth table of a NAND gate:

It is clear from the truth table of two input NAND gate that the output is 1 when either A or B or when both the inputs are at logic '0'. For all input value combinations AND gate output is exactly opposite to the output of NAND gate. The logical expression for the output is given by:

$Q = \overline{A}\overline{B} = \overline{A} + \overline{B}$

The NAND gate can perform the OR function by inverting the inputs. The OR gate with inverted inputs is called bubbled OR gate or negative OR gate. The NAND gate is also called active low OR gate.

## 1.1.2 Exclusive or Gate (Xor)

A basic XOR gate is a two-input single output logic gate, whose output is assumed to be HIGH only when one and only one of its inputs are HIGH. XOR can simply be defined as one or the other but not both. Logical representation of XORgate as shown in Figure 1.

Figure 1. Logical representation of XORgate

If input variables are represented by A and B then the logical expression for output is given by

$Q = A\bar{B} + \bar{A}B$

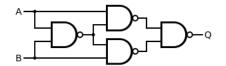

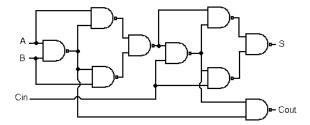

XOR gate is known as an odd number of 1's detector in the input. Realization of XOR gate using NAND gate as shown in Figure 2.

Figure 2. Realization of XOR Gate using NAND gate

The most important application of XOR gate is in parity generation and detection. It is also known as staircase switch. XOR gate acts as an inverter for control input of logic '1'.

Estimation of power and delay in CMOS circuits using LCT (Aylapogu Pramod Kumar)

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

The truth table of XOR gate

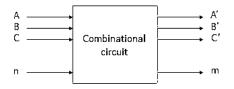

## 1.1.3 Combinational Logic Circuits

The circuit which consists of an interconnection of logic gates whose outputs at any instant of time are determined from a present combination of inputs only is defined as a combinational logic circuit. The 'n' input binary variables come from external sources; the combinational logic circuit produces 'm' output variables by the internal logic connections and go to an external destination. Every input and output variables are contacts physically as an analog signal whose values are interpreted to be a binary signal that represents logic high and logic low:

For 'n' input variables, there are 2n possible combinations of binary inputs.

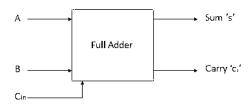

#### 1.1.4 Full-Adder

The combinational circuit that performs the arithmetic sum of three input bits is known as a Full-Adder. It consists of three input variables designated by augend, addend and the carry bit. The two output variables produce the SUM and CARRY. Block diagram of full adder as shown in Figure 3. Full adder realization using NAND gate as shown in Figure 4.

Figure 3. Block diagram of full adder

Figure 4. Full Adder realization using NAND gate

From the truth table given below, the logical expressions for Sum (S) and Carry (Cout) are:

$S = \overline{ABC} + \overline{ABC} + A\overline{BC} + A\overline{BC} + ABC = A \oplus B \oplus C$  $C_{out} = AB + BC + CA = AB + C (A \oplus B)$

Indonesian J Elec Eng & Comp Sci, Vol. 14, No. 2, May 2019 : 990 - 998

| <b>D</b> 9 | 93 |

|------------|----|

|------------|----|

|   | Inpu | t |   | Ou | tput |

|---|------|---|---|----|------|

| А | В    | С |   | S  | Cout |

| 0 | 0    | 0 |   | 0  | 0    |

| 0 | 0    | 1 |   | 1  | 0    |

| 0 | 1    | 0 |   | 1  | 0    |

| 0 | 1    | 1 | 0 |    | 1    |

| 1 | 0    | 0 |   | 1  | 0    |

| 1 | 0    | 1 |   | 0  | 1    |

| 1 | 1    | 0 |   | 0  | 1    |

| 1 | 1    | 1 |   | 1  | 1    |

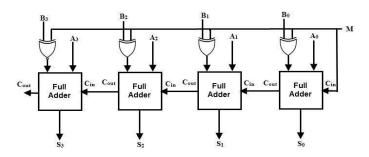

#### 1.1.5 Paralleladder-Subtractor

A binary parallel adder-subtractor is a combinational digital circuit that adds two binary numbers in parallel form. It consists of full-adders connected in cascade with output carry from each full adder connected to the input carry of the next full adder. The mode bit 'M'acts a control line i.e. depending on the value of M, the circuit acts as an adder or subtractor. The circuit shows Parallel Adder-Subtractor realized using Full Adders. Four bit parallel adder as shown in Figure 5.

Figure 5. Four bit parallel adder

When M is driven low (M=0) then one input to each and every XOR gate would be logic '0'. This results in un-altered XOR outputs. Also, Cin of the first full adder would be low. The cascaded circuit will act as a parallel adder. When M control line is pulled high (M=1) then one of the inputs to each XOR gate would be logic '1'. This results in complemented bits as XOR output which is fed as an input to each full adder circuit. Also, Cin of the first full adder would be logically high. As a result, the cascaded arrangement will act as a parallel subtractor.

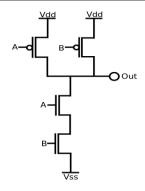

#### 1.1.6 Cmos Logic Family (Nand Gate)

A CMOS (Complementary Metal Oxide Semi- Conductor FET) logic family is obtained by connecting a p-channel and an n-channel MOSFET in series to realize several advantages over the PMOS and NMOS families. In CMOS, p-channel and n-channel MOS devices are fabricated on the same chip. It makes the CMOS fabrication more complicated and reduces the package density. The important advantages are high speed and low power consumption. They can also be operated in high voltage resulting in improved noisemargin. To implement the CMOS NAND gates, the NMOS transistors are connected in series and the PMOS transistors are connected in parallel. For a given Silicon area, the 'ON' resistance for NMOS is less than that of the PMOS. CMOS NAND gate is generally faster than NOR gate. CMOS NAND gate and truth table are givenbelow.

When the inputs A and B are high, PMOS transistors are open circuited and NMOS transistors are short-circuited resulting in zero output. If any of the inputs is low, PMOS transistors are short-circuited and NMOS transistors are open circuited providing a high output. The truth table shows the possible operation of NAND gate usingCMOS. CMOS NAND gate as shown in Figure 6.

| Inp | outs | Out | puts  |

|-----|------|-----|-------|

| А   | В    | Y   | Logic |

| 0   | 0    | Vdd | 1     |

| 0   | 1    | Vdd | 1     |

| 1   | 0    | Vdd | 1     |

| 1   | 1    | GND | 0     |

Estimation of power and delay in CMOS circuits using LCT (Aylapogu Pramod Kumar)

Figure 6. CMOS NAND gate

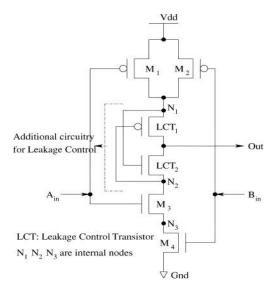

# 2. PROPOSED LECTOR TECHNIQUE

In the design of CMOS VLSI circuits, power dissipation is one of the major considerations. The minimization of the threshold voltage due to voltage climb up leads to increase in sub-threshold leakage current and static power dissipation in CMOS circuits. CMOS gates are designed using LEakage Control TransistOR (LECTOR) Technique which results in the reduction of the leakage current without any impact on dynamic power dissipation. In any supply to ground path, a state with more than one transistor OFF in a path from the source voltage to earth is far less leaky than a state with only one transistor OFF. Two leakage control transistors are introduced in every CMOS logic gate such that one of the LCT's is near its cut-off region of operation. Two input LCT NAND gate. In this paper, we implement LECTOR Technique with NAND gate. A CMOS NAND gate with the addition of two leakage control transistors is shown in the Figure 7.

Figure 7. Two input LCT NAND gate. The leakage control transistors LCT1 and LCT2 are inserted between the nodes N1 and N2 and they act as self-controlled stacked transistors

Two leakage control transistors LCT1 (PMOS) and LCT2 (NMOS) are introduced between the nodes N1 and N2 of the pull-up and pull-down logic of the NAND gate. The drain terminals of the transistors LCT1 and LCT2 are wired together to form the output node of the NAND gate. The source terminals of the transistors are wired to nodes N1 and N2 of pull-up and pull-down logic respectively. The switching of the transistors LCT1 and LCT2 are controlled by the voltage potentials at nodes N2 and N1 respectively. This configuration ensures that one of the LCT's is always near its cut-off region irrespective of the input vector applied to the NAND gate [3]. LECTOR does not require any other additional control circuitry to monitor the states of the circuit. Self-biased transistors have their gate and their drain terminals wired together as a single node. Thus no external control circuitry isrequired.

# 3. SIMULATION RESULTS AND DISCUSSION

Basing on the schematic model of the parallel adder-subtractor, the conventional and LECTOR models are simulated in Mentor Graphics. The parallel adder-subtractor is realized using the NAND gates throughout the simulation. By varying the supply voltage, power dissipation and delay are observed for each voltage and adder-subtractor inputs. The values for both conventional and LECTOR models are recorded for further comparisons and observations.

The adder-subtractor inputs are considered as shown in the below tables. As discussed in section I.E, the model acts as an adder when Mode M = 0 and as a subtractor for mode M = 1.

|        | A1 | B1 | S1         | C1 |  |

|--------|----|----|------------|----|--|

|        | 0  | 1  | 1          | 0  |  |

|        | 1  | 0  | 1          | 0  |  |

|        | 0  | 0  | 0          | 0  |  |

|        | A2 | B2 | S2         | C2 |  |

|        | 0  | 1  | 1          | 0  |  |

|        | 1  | 1  | 0          | 1  |  |

|        | 1  | 0  | 1          | 0  |  |

| Mode 0 | A3 | B3 | <b>S</b> 3 | C3 |  |

|        | 1  | 1  | 0          | 1  |  |

|        | 0  | 1  | 0          | 1  |  |

|        | 1  | 1  | 0          | 1  |  |

|        | A4 | B4 | <b>S</b> 4 | C4 |  |

|        | 1  | 1  | 1          | 1  |  |

|        | 1  | 1  | 1          | 1  |  |

|        | 0  | 0  | 1          | 0  |  |

|        |    |    |            |    |  |

Let 010 and 100 be the inputs A1, B1 to the first full-adder in simulated Parallel Adder- Subtractor circuit. When the Mode input M is '0', the circuit will act as an adder. The Carry input for the first full adder will be 0. The XOR gate takes B and Mode as inputs and gives B as its output as M=0. The Full-Adder will then add A, XOR output, Cin and gives S1 and C1 as its outputs. C1 will act as an input carry for the next full-adder. The operation will be carried out similarly through the remaining circuit till S4 and final Carry are obtained.Similarly, when the Mode input M is '1', the circuit will act as a subtractor. The Carry input for the first full adder will be 1. The XOR gate takes B and Mode as inputs and gives S1 and C1 as its output as M=1. The Full-Adder will then add A, XOR output, Cin and gives S1 and C1 as its outputs. C1 will act as an input carry for the next full-adder. The operation will be carried out similarly through the remaining circuit till S4 and final Carry are obtained. S1 and C1 as its output. C1 will act as a final C1 as its output as M=1. The Full-Adder will then add A, XOR output, Cin and gives S1 and C1 as its outputs. C1 will act as an input carry for the next full-adder. The operation will be carried out similarly through the remaining circuit till S4 and final Carry areobtained.

|        | A1 | B1 | S1         | C1 |

|--------|----|----|------------|----|

|        | 0  | 1  | 1          | 0  |

|        | 1  | 0  | 1          | 1  |

|        | 0  | 0  | 0          | 1  |

|        | A2 | B2 | S2         | C2 |

|        | 0  | 1  | 0          | 0  |

| Mode 1 | 1  | 1  | 0          | 1  |

|        | 1  | 0  | 1          | 1  |

|        | A3 | B3 | <b>S</b> 3 | C3 |

|        | 1  | 1  | 1          | 0  |

|        | 0  | 1  | 1          | 0  |

|        | 1  | 1  | 0          | 1  |

|        | A4 | B4 | <b>S</b> 4 | C4 |

|        | 1  | 1  | 1          | 0  |

|        | 1  | 1  | 1          | 0  |

|        | 0  | 0  | 0          | 1  |

|        |    |    |            |    |

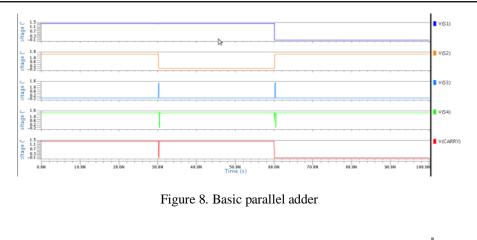

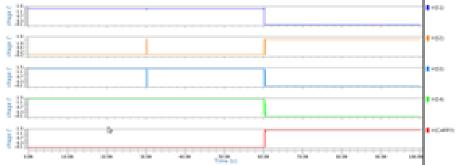

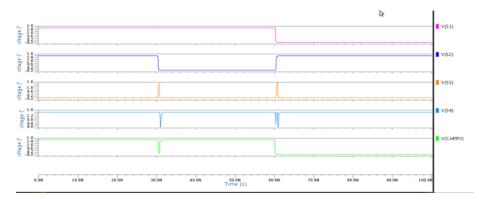

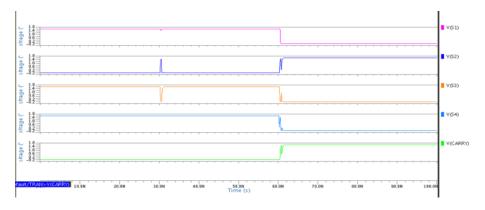

The outputs of a basic parallel adder-subtractor and LCT parallel adder-subtractor are plotted for the considered inputs as described in Table 4. Basic parallel adder, LCT adder, and LCT subtractor as shown in Figure 8 to 10.

Basic parallel subtractor

Figure 9. LCT adder

997

Power Dissipation and Delay of a Basic Parallel Adder-Subtractor in Adder Mode (M=0), Power Dissipation and Delay of a Basic Parallel Adder-Subtractor in Adder Mode (M=0) and Power Dissipation, Delay of an LCT Parallel Adder-Subtractor in Adder Mode (M=0) and Power Dissipation and Delay of an LCT Parallel Adder-Subtractor Mode (M=1) as shown in Table 1 to 4.

| Та     | Table 1. Power Dissipation and Delay of a Basic Parallel Adder-Subtractor in Adder Mode (M=0) |                 |        |        |           |        |        |  |

|--------|-----------------------------------------------------------------------------------------------|-----------------|--------|--------|-----------|--------|--------|--|

|        | Voltage                                                                                       | Power           |        |        | Delay(ps) |        |        |  |

|        |                                                                                               | Dissipation(nW) | S1     | S2     | S3        | S4     | C4     |  |

|        | 1                                                                                             | 49.4405         | 178.85 | 268.08 | 503.65    | 564.79 | 103.79 |  |

| Mode 0 | 1.2                                                                                           | 55.5687         | 137.76 | 209.94 | 391.95    | 436.61 | 79.439 |  |

|        | 1.4                                                                                           | 72.2754         | 114.95 | 176.23 | 329.13    | 363.61 | 65.995 |  |

|        | 1.6                                                                                           | 92.0056         | 100.60 | 156.13 | 283.50    | 318.49 | 57.405 |  |

|        | 1.8                                                                                           | 115.3078        | 90.891 | 141.53 | 262.87    | 287.68 | 51.622 |  |

Table 2. Power Dissipation and Delay of a Basic Parallel Adder-Subtractor in Subtractor Mode (M=1)

|        | Voltage | Power           |        | Delay(ps) |            |        |        |  |

|--------|---------|-----------------|--------|-----------|------------|--------|--------|--|

|        |         | Dissipation(nW) | S1     | S2`       | <b>S</b> 3 | S4     | C4     |  |

|        | 1       | 37.0195         | 336.11 | 479.73    | 458.25     | 177.75 | 613.07 |  |

| Mode 1 | 1.2     | 49.5823         | 259.72 | 370.37    | 355.16     | 137.74 | 471.71 |  |

|        | 1.4     | 64.4102         | 216.97 | 309.73    | 297.78     | 124.46 | 392.69 |  |

|        | 1.6     | 81.8852         | 190.22 | 271.77    | 262.03     | 120.38 | 343.64 |  |

|        | 1.8     | 102.4766        | 172.14 | 245.95    | 237.44     | 100.35 | 310.42 |  |

Table 3. Power Dissipation and Delay of an LCT Parallel Adder-Subtractor in Adder Mode (M=0)

|        | Voltage | oltage Power    |        | Delay(ps) |        |        |        |

|--------|---------|-----------------|--------|-----------|--------|--------|--------|

|        |         | Dissipation(nW) | S1     | S2        | S3     | S4     | C4     |

|        | 1       | 39.0280         | 664.75 | 994.99    | 1721   | 723.68 | 376    |

| Mode 0 | 1.2     | 51.6831         | 427.66 | 637.52    | 1119   | 459.24 | 237.52 |

|        | 1.4     | 66.5318         | 319.56 | 482.33    | 850.34 | 379.85 | 175.21 |

|        | 1.6     | 83.8677         | 261.97 | 397.90    | 704.96 | 338.96 | 140.44 |

|        | 1.8     | 104.0790        | 225.61 | 345.99    | 614.11 | 307.68 | 119.39 |

Table 4. Power Dissipation and Delay of an LCT Parallel Adder-Subtractor in Subtractor Mode (M=1)

|        | Voltage | Power<br>Dissipation(nW) | Delay(ps) |         |            |        |         |

|--------|---------|--------------------------|-----------|---------|------------|--------|---------|

|        |         | i v v                    | S1        | S2`     | <b>S</b> 3 | S4     | C4      |

| Mode 1 | 1       | 35.2997                  | 1338.2    | 1381.45 | 683.32     | 682.16 | 1282.30 |

|        | 1.2     | 45.2043                  | 840.63    | 892.71  | 432.42     | 432.16 | 817.06  |

|        | 1.4     | 59.6495                  | 624.35    | 671.72  | 322.84     | 322.40 | 617.12  |

|        | 1.6     | 76.9218                  | 509.01    | 559.55  | 263.48     | 263.15 | 508.87  |

|        | 1.8     | 94.4894                  | 438.75    | 493.38  | 226.90     | 196.48 | 443.06  |

The power dissipation and delay are the most important factors to measure the performance of the circuits. Actual power delivered by the circuit is measured as the power dissipated by the circuit. The time taken to propagate the input signal from the gate to the output of the gate is considered as adelay. When the speed of operation is important, each circuit must have a short propagation delay. As the number of logic levels decreases, delay decreases. The power dissipation and delay of a basic parallel adder-subtractor model acting as an adderi.e. when M=0 is given in the Table- I and as a subtractor when M=1 is given in Table-II. Voltage is varied and delay and dissipation are recorded for each varied input.Similarly, the power dissipation and delay of an LCT parallel adder-subtractor model acting as an adder i.e. when M=0 is given in the Table-IV. Voltage is varied and delay and dissipation are recorded for each varied and delay and dissipation are recorded for each varied methods leakage current dimnishments and efficiency measurements comparision are shown in below Table 5.

| Table | e 5. Effic | ciency Analysis for l | LCT Leakage Current |

|-------|------------|-----------------------|---------------------|

|       | S.No       | Topologies            | Efficiency (%)      |

| -     | 1          | Reference[6]          | 79.40               |

|       | 2          | Reference[7]          | 79.85               |

|       | 3          | Proposed Technique    | 82.50               |

# 4. CONCLUSION

Power dissipation and delay are the major parameters that affect the performance of the circuit. The performance of a simulated basic parallel adder-subtractor model and the LCT parallel adder-subtractor simulated model is compared. The parallel adder-subtractor with LCTs offer a reduction in leakage power as the LCT is in near cut-off region always. However, the increase in a number of logic levels increases the delay as the delay is considered by taking the average of delays at the gates of each logic level. The proposed technique overcomes the limitations posed by the existing methods for leakage reductions an average leakage reductions is 82.5%. When the speed of operation is needed, the reduction in a number of logic levels will improve the performance of the circuit decreasing the delays.

#### REFERENCES

- Preeti Verma, Ajay K. Sharma, Vinay Shankar Pandey, Arti Noor, Anand Tanwar "Estimation in leakage power and delay in CMOS circuits using parametric variation", Recent Trends in Engineering and Material Sciences, pg. 760-763,2016

- [2] Venkata Ramakrishna Nandyala, Kamala KantaMahapatra "A Circuit Technique for Leakage Power reduction in CMOS VLSI circuits", International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA),2016

- [3] Dr. K. V. V. K. Prasad, Kattula Shyamala "VLSI Design A comprehensive coverage of VLSI Implementation technologies, Electronic Design Automation Tools and FPGA Design Black Book", 2014 Edition.

- [4] Zhang Zhigang, Wang Jingqin, Wang Li, Wang Meng "Reliability Evaluation of Low-volatage Switchgear Based on Maximum Entropy Principle", TELKOMNIKA Journal, vol.15, no.1, pp. 101-108, March 2017.

- [5] Kanan Bala Ray, Sushanta K.Mandal, B.S.Patro"Low Power FGSRAM Cell Using Sleepy and LECTOR Technique ", Indonesian Journal of Electrical Engineering and Computer Science, vol.4, no.2, pp. 333-340, November 2016.

- [6] NarenderHanchate, NagarajanRanganathan "LECTOR: a technique for leakage reduction in CMOS circuits", IEEE Trans. VLSI Systems, vol.12, no.2, pp. 196-205, February 2004.

- [7] Mansi Gangele, K.Pitambar Patra "Comparative Analysis of LECTOR and Stack Technique to reduce the leakage current in CMOScircuits", IJRET, vol 4, July-2015.

- [8] B. Dilip, P. Surya Prasad, R.S.G Bhavani "Leakage Power Reduction in CMOS circuits using LECTOR Technique in nano scale echnology", IJESS, vol 2, 2012.

- [9] Nikhil Saxena, Sonal Soni "Leakage current reduction in CMOS circuits using stacking effect", IJAIEM, vol 2, November 2013.

- [10] Siddhesh Goankar "Design of CMOS inverter using LECTOR Technique to reduce the leakage power" IJRTA Special Issue 31, pp 231-233, September 2015.

- [11] Siba Monther Yousif, Roslina M. Sidek, Anwar Sabah Mekki, Nasri Sulaiman, Pooria Varahram "Efficient Low-Complexity Digital Predistortion Power Amplifier Linearization", International Journal of Electrical and Computer Engineering, vol.6, no.3, pp. 1096-1105, June 2016.

- [12] M. Morris Mano, Michael D. Ciletti "Digital Design", pg 486-523, Fourth Edition, 2008

- [13] R.P. Jain "Modern Digital Electronics", Chapter 4, Fourth Edition, 2010.

- [14] Anand Kumar "Switching Theory and Logic Design", Chapter 4, Fourth Edition, 2008.

- [15] Anand Kumar "Pulse and Digital Circuits", Chapter 8 and 9, Second Edition, 2008.