# Design of "32" Point Split Radix based Multipath Delay Commutator FFT Architecture for Low Power Applications

## A. Manimaran, ABY K. Thomas

Department of Electronics and Communication Engineering, Hindustan Institute of Technology & Science, Chennai, India

ADGTDACT

| Article into                                                                                  | ABSIRACI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article history:                                                                              | FFT is used in Modern high speed signal processing application. In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Received May 23, 2018<br>Revised Jul 25, 2016<br>Accepted Jul 30, 2016                        | aforementioned technologies that tends to operate in various operational<br>modes. To implement FFT obviously it not only needs to meet high<br>throughput demand and also it needed to scalable cater selectable N point<br>FFT. Our contribution to this paper is two-fold of our existing method, as<br>proposes for the split radix using Multipath Delay Commutator (MDC)                                                                                                                                                                                                           |

| Keywords:                                                                                     | <ul> <li>algorithm has the least complex design and less multiplications comparing to<br/>radix-2 algorithm. So that it can able to reduce power consumption and area</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| Multipath delay commutator<br>(MDC)<br>Split radix FFT (SRFFT)<br>Low power<br>Area efficient | than our existing work. The implementation of power efficient hardware of<br>split radix FFT (SRFFT) is built up by pruning excessive computation.<br>Leveraging this potential, a new architecture of a configurable SRFFT<br>processor is first developed so that unnecessary computations, which yield<br>zeros at the output, are pruned. Simulations show that maximum power<br>saving of around 20% is achieved. The proposed algorithm consists of mixed<br>radix butterflies, whose structure is more regular. It has the conjugate-pair<br>version, which requires less memory. |

|                                                                                               | Copyright © 2018 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **Corresponding Author:**

A --- the le T--- fe

A. Manimaran Department of Electronic and Communication Engineering, Hindustan Institute of Technology and Science, Chennai, India. Email: lims0181@gmail.com

#### 1. INTRODUCTION

FFT with split radix method was initially described by Duhamel and Hollman in the year of 1948. The SRFFT algorithm is also called as FFT algorithm. It uses two radix in single butterfly operations, even terms for radix-2 and odd terms for radix-4 structure, which computes in the butterfly structure with the shape of "L". Radix-8 Cooley–Turkey (CT) algorithm's efficiency, can be obtained by this algorithm. It can be designed by the combination of radix-2 and radix-4 [1]. This can be achieved by Radix-4 CT FFT's complexity and the Radix-2 CT FFT's flexibility. By combining radix-2 algorithm the cost for computing is minimized in the split radix FFT architecture.

In pipelined architecture, the both SDF architecture and MDC architecture furnishes the same throughput with the low memory and less complex multipliers and adders. Although, multipath Commutator architecture can yield N times throughput of single feedback architecture only at the high Memories, high number of complex multipliers and adders. The FFT with split radix structure has the advantages of which a multiplier /accumulator is the basic processor, but has the disadvantage of SRFFT butterfly computational unit as the basic processor. Pipelined hardware is much hard to realize for the SR algorithm than CT algorithm because the computational load varies between the various stages. The SRFFT algorithm using MDC of VLSI implementation is proposed for the radix 4-FFT and radix 2-FFT because it has less computations in pipelined architecture with multiple path delay commutators. It has good throughput

obtained from its raised parallelism and also has the elasticity of providing the SRFFT of sequence that have the power of two, also by using four, for the R4-FFT.The cost that needs to implement SRFFT has increase due to the high parallelism but it balances the computational power and flexibility also added for the proposed FFT architecture [2].The FFT algorithm with split radix and radix-2 FFT algorithm are almost same with the exception of its location and twiddle factors values. The computational complexity of the FFT can be reduced by using pipelined 32-point split-radix multi-path delay commutator (SRMDC) FFT architecture. It reduces the slices and LUT counts for reducing the area occupying of the FFT processor. The proposed architecture is mainly to improve an efficiency of the FFT processor

### 2. BACKGROUND

In explained an extensive FFT algorithm with split radix structure. The extended FFT algorithm and the traditional FFT algorithm with split radix structure has the same asymptotic arithmetic difficulty. FFTs are operated on that the need registers to compute a split-radix FFT algorithm; FFTs will use few loads and stores on the radix-4 FFT algorithm. The no of load, store, arithmetic operations used for R2, R4, and R8 and extended split-radix using 4- multiply 2-add schemes.

In described that the implementation of split radix FFT. They are compared with the SRFFT algorithm for power of two (i.e.,)  $x^2$  transform to the Cooley-Turkey (CT) FFT algorithm. The SR FFT requires few complex multiplications than the CT algorithms of radix two, four and eight. It requires about 20-50% more butterfly operations than the radix four CT FFT [3]. Subsequently, the utilities of SRFFT algorithm for depend on multiply or accumulate the rate of throughput. The techniques that are used to construct SRFFT pipelined implementation are simple.

In explained parallel MDCFFT processor with efficient scheduling. The proposed work FFT processor can attain by using parallel data-path design with high throughput MDC structure. This scheme reduces the no of complex multipliers from eight to six with no rising of delay buffers. It can also offer a lower hardware computational complexity with 100 percent utilization of hardware [4]. The FFT processor can be utilized in OFDM essential with the lower complexity and higher complexity.

In proceeded that the flexible MDC-based FFT architecture and are used for higher performance generator applications [5]. The proposed work was done easy and flexible that is to satisfy throughput rate. In proposed work, automatically generate the particular HDL code by hardware generator and hardware generator is also developed so that the time and cost can be extremely reduced. MDC-based architectures first divide the input sequence into two parallel data streams by properly-controlled switches/FIFOs and direct them to the correct butterfly units MDC-based architecture demands a little bit resources and with high throughput but larger throughput [6].

# 3. MIXED R2SDF-R4SDC

There are four types of pipelined FFT architecture are single delay feedback (SDF), singlepath delay commutator (SDC), Multipath delay feedback(MDF), Multipath delay commutator(MDC). It can be classified as Multipath or single path by their no. of input data stream paths [7]. Mixed R2SDF-R4SDC pipelined FFT architecture gives the  $\log_2$  (N-1) SDC stage with one SDF stage. The R2SDF-R4SDC work done for the 100% efficient utilization of hardware resources in multiplexed time approach by sharing the same resource of arithmetic operations that considers of adders and also multipliers. It reduces the requirement of complex multipliers while comparing with other radix FFT architectures [8]. It also requires complex adders and complex delay. Figure represents the DIF Dataflow graph the combined SDC-SDF FFT Pipelined structure which has the output in sequential flow[9]. It reduces complex multiplier of 50% while comparing with the other radix FFT architecture.

### 4. PROPOSED SPLIT RADIX USING MDC ARCHITECTURE

Fast computation of the discrete Fourier transform (DFT) is called as fast Fourier transform. Algorithm of Multipath delay split radix FFT (SRFFT) algorithm for sequential data that having a power integer length of  $2(N = 2^m)$  is based on radix-2 application for coefficients computation of even terms of the transform and radix-4 applications for computing the odd terms coefficient of the transform. SR-DIF FFT algorithm is obtained by applying equally in R-2 and R-4 FFT algorithm to clear the problem [10].

By changing the exponents of twiddle factor, it can be obtained by converting straight forwardly into radix 4 FFT algorithm. The SR algorithm is based on the following decomposition:

NI A

$$Y_{k} = \sum_{n=0}^{N-1} y_{n} W^{nk}$$

$$Y_{k} = \sum_{n=0}^{\frac{N}{2}-1} (y_{n} + y_{n} + \frac{N}{2}) W_{N}^{2nk} k = 0, 1, \dots, \frac{N}{2} - 1$$

$$Y_{4k+1} = \sum_{n=0}^{\frac{N}{4}-1} [(y_{n} - y_{n} + \frac{N}{2}) - j(y_{n} + \frac{N}{4} - y_{n} + 3\frac{N}{4})] W_{N}^{n} W_{N}^{4nk}$$

$$Y_{4k+3} = \sum_{n=0}^{\frac{N}{4}-1} [(y_{n} - y_{n} + \frac{N}{2}) + j(y_{n} + \frac{N}{4} - y_{n} + 3\frac{N}{4})] W_{N}^{3n} W_{N}^{4nk} k = 0, 1, \dots, N/4 - 1$$

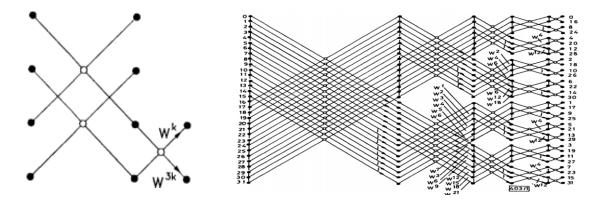

To calculate FFT using the method of Split radix using radix-2 and radix-4, it can be computed that even no points and the odd no points and that can be resulted independently. This reduces the complexity of arithmetic computational processing complexity in the opportunity of using various computational schemes for various parts of the algorithm [11]. Splitting by combining two radix that is the radix-2 and radix-4 and why are proceeding for the split radix is because radix-2 is best mean for simplicity and radix-4 is for less computational complexity, resulting in less arithmetic calculation stages [12]. Split radix FFT algorithm represents the DIF length N, length N/2 represents one small DFT and length N/4 represents two small DFTs. In Figure 1 shows the split radix algorithm FFT flow graph and the butterfly structure of 32-point split radix FFT using MDC shown in Figure 2.

Figure 1. Structure of Split Radix algorithm

Figure 2. 32-point Split Radix FFT Butterfly Structure

## 5. PROPOSED MULTIPATH DELAY COMMUTATOR (MDC) WITH SPLIT RADIX FFT

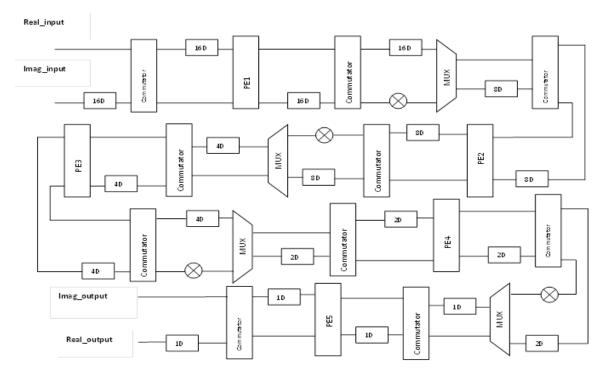

In this paper, the proposed work gives the architecture of 32 point split radix multipath delay Commutator is established to decrease the area utilization and power utilization of the processors. In the conventional method, mixed architecture of radix-2, radix-4 and radix-8 is design is used to decrease the power and area consumption. In the proposed split radix FFT architecture using MDC was designed. The designed architecture is compared with the conventional architecture; the proposed FFT structure has great increase in the speed and throughput of the processor and also drastically decreases the power, occupied slices, and LUT counts.

Compared with the existing method, proposed work gives the better performance. Split radix FFT is evaluated completely in MDC. Figure 3 represents the 32-point split-radix Multipath delay commutator pipelined architecture. Figure 3 show the proposed method contains processing elements, commutators, twiddle factors, multiplexers, delay buffers. Converting from one signal form to another signal form is the main process of commutator. By using processing elements, that is used for the complex value addition and

subtraction. Among four input data samples one sample is selected at each clock cycles, Multiplexers are used [13]. Twiddle factors are to be implemented efficiently using signed digit approach. In this architecture, FFT processor performance can be improved by using multiple numbers of delays. Split radix based FFT algorithm needs only both smaller number of multiplies and joint multiplies and adds than radix-4 and radix-2 algorithm. An arithmetic operation in the split radix based MDC architecture is reduced. High throughput can be achieved by using pipelined method and MDC structure. Reduced complexity radix-4 FFT is used in 32-point split radix FFT with multiple path delay.

Figure 3. 32-point split-radix multi-path delay commutator (SRMDC) pipelined FFT architecture

# 6. **RESULTS AND DISCUSSION**

The proposed split radix FFT using the multipath delay commutator by using Verilog HDL. The proposed architecture has the advantage of having only few arithmetic operations compared to the existing method. Split-radix also have some advantages that is it has a clear cut structure, except the output signals it has no reordering of input signals, etc. The simulation results have been processed by using ModelSim XE simulator and those results are evaluated using Xilinx ISE 10.1 processing tool. Power, Area has been reduced and performance of proposed one has been utilized efficiently. Figure 4 shows the simulation result of the proposed FFT structure. Table.1 shows the Existing and proposed method performance.

| Т                         | able 1. Comparison b         | etween Existing and Proposed M | lethod    |

|---------------------------|------------------------------|--------------------------------|-----------|

| Parameters Noticed        | Existing FFT<br>Architecture | Proposed FFT Architecture      | % reduced |

| Number of LUTs            | 13602                        | 10143                          | 25.1%     |

| Number of flip flops      | 1761                         | 931                            | 47.13%    |

| Number of slice Registers | 2476                         | 1711                           | 30.89%    |

| Power(mW)                 | 5.248                        | 2.958                          | 43.63%    |

| Delay (ns)                | 19.470ns                     | 25.188ns                       | ~         |

| Messages             |                    |                   |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      | 4                 |             |                   |          |      |      |      |      |               |      |            |             |           |

|----------------------|--------------------|-------------------|-----------|--------|------|------------------|------------|-------------|-----|-----------------|-------------------|------|------------------|-----|------------|------|-------------------|-------|------|-------------------|-------------|-------------------|----------|------|------|------|------|---------------|------|------------|-------------|-----------|

| /top_new/dk          | St1                |                   |           |        |      |                  |            |             | Б   |                 | П                 |      |                  |     |            | F    |                   |       |      |                   |             |                   |          |      |      |      |      |               | Ь    |            |             |           |

|                      | St1                |                   |           |        |      |                  |            |             |     |                 | -                 |      |                  |     |            |      |                   |       |      |                   | -           |                   |          |      |      | -    |      |               | -    |            |             |           |

| -👉 /top new/data rin | 14                 | 1                 |           |        |      |                  |            |             | -   |                 | -                 |      |                  | -   |            | -    |                   |       | -    |                   |             |                   |          |      |      |      |      |               | -    |            |             |           |

| /top_new/data_in     | 14                 | 1                 |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/data_rout   | 0                  |                   | )496 (-16 | 1-32   | 10   | <u>)</u> -54     | Ì-10       | Í-22        | 22  | Ĭ-95            | ) <del>-</del> 13 | í-27 | 17               | -39 | Ĭ-5        | )-19 | 163               | 1-172 | I-16 | )-28              | 10          | ) <del>-4</del> 6 | Ì-6      | 1-22 | )34  | Ĭ-62 | )-16 | Í-20          | 110  | Ĵ-35       | Ĭ1          | )-15 (13) |

| /top_new/data_iout   | 0                  | )                 | 496 -16   | 0      | (-32 | 22               | 1-22       | (-10        | -54 | 63              | )-19              | (-5  | )-39             | 7   | 1-27       | )-13 | ( <del>-</del> 95 | 140   | -16  | -4                | 1-32        | (14               | -26      | -10  | -66  | (30  | -16  | (-12          | -42  | 13         | (-33        | -17 -16   |

| /top_new/constant    | 0 0                |                   |           |        |      | _                | _          |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   | _           |                   |          |      |      |      |      | _             |      |            |             |           |

| /top_new/cnt         | 14                 | 161               | 62 63     | 1-64   | j-63 | Ĭ-62             | Ì-61       | Ĭ-60        | -59 | Ĭ-58            | ) <del>-</del> 57 | Í-56 | Ĵ-55             | -54 | Ĭ-53       | )-52 | Ĭ-51              | )-50  | -49  | )-48              | Ì-47        | ) <del>-4</del> 6 | Ĵ-45     | -44  | )-43 | (-42 | )-41 | (- <b>4</b> 0 | 1-39 | 1-38       | <u>(-37</u> | )-36 (-35 |

| /top_new/con1        | 1                  |                   | ·         |        |      |                  | -          |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   | -           |                   | <u> </u> |      |      | -    |      |               |      |            |             |           |

| /top_new/con2        | 0 0                |                   |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/con4        | 0                  | 2                 |           | 10     |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/con5        | 0                  |                   |           | -2     |      |                  |            |             |     |                 |                   | 0    |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/con6        | 0                  |                   |           | -2     |      |                  |            |             |     |                 |                   | 0    |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/con7        | 0                  | 2                 |           | 1      |      |                  |            |             |     |                 |                   | -2   |                  |     |            |      |                   |       |      | ) <mark>0</mark>  |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/con9        | 0                  | 2                 |           | 11     |      |                  |            | (-2         |     |                 |                   | 1    |                  |     |            | )-2  |                   |       |      | 0                 |             |                   |          |      |      |      |      |               |      |            |             |           |

| /top_new/con 10      | 0 6                |                   |           | -2     |      |                  |            | 1           |     |                 |                   | (-2  |                  |     |            | )1   |                   |       |      | )-2               |             |                   |          | 0    |      |      |      |               |      |            |             |           |

| /top_new/con11       | 0                  |                   |           | 1-2    |      |                  |            | 11          |     |                 |                   | (-2  |                  |     |            | 11   |                   |       |      | )-2               |             |                   |          | 10   |      |      |      |               |      |            |             |           |

| 🔶 /top_new/con 12    | 0                  | 2                 |           | 1      |      |                  |            | -2          |     |                 |                   | 1    |                  |     |            | )-2  |                   |       |      | 1                 |             |                   |          | -2   |      |      |      | 0             |      |            |             |           |

| 🔶 /top_new/con 14    | 0 1                |                   | )-2       | 1      |      | )-2              |            | <u>)</u> 1  |     | ) <del>-2</del> |                   | 1    |                  | -2  |            | )1   |                   | )-2   |      | )1                |             | )-2               |          | 1    |      | (-2  |      | 0             |      |            |             |           |

| 🔶 /top_new/con15     | 0                  | 2                 | )1        | -2     |      | <u>)</u> 1       |            | <b>.</b> -2 |     | <u>(1</u>       |                   | -2   |                  | 1   |            | )-2  |                   | )1    |      | ) <mark>-2</mark> |             | <u>)</u> 1        |          | -2   |      | (1   |      | <b>[-2</b>    |      | 0          |             |           |

| 🔶 /top_new/con 16    | 0                  | 2                 | )1        | -2     |      | <u>)</u> 1       |            | (-2         |     | (1              |                   | -2   |                  | 1   |            | )-2  |                   | )1    |      | -2                |             | <u>)</u> 1        |          | -2   |      | (1   |      | (-2           |      | 0          |             |           |

| -💠 /top_new/con 17   | 0                  |                   | -2        | 1      |      | )-2              |            | <u>(1</u>   |     | <u>(-2</u>      |                   | (1   |                  | -2  |            | )1   |                   | )-2   |      | <u>)1</u>         |             | )-2               |          | 1    |      | (-2  |      | <u>(1</u>     |      | Į-2        |             | )0        |

| 🔶 /top_new/con 19    | 0                  | .) <del>-</del> 2 | )1 (-2    | 1      | (-2  | )[1              | <u>[-2</u> | <u>(1</u>   | -2  | (1              | )-2               | (1   | ) <del>-</del> 2 | 1   | )-2        | )1   | (-2               | )1    | -2   | <u>)1</u>         | I-2         | )1                | -2       | 1    | )-2  | (1   | -2   | (1            | -2   | 1          | (-2         | )0        |

| 🔶 /top_new/con20     | 0 0                | 1                 | -2 1      | -2     | (1   | ) <del>-</del> 2 | (1         | ) <b>-2</b> | 1   | <b>(-2</b>      | )1                | -2   | )1               | -2  | <u>)</u> 1 | )-2  | <u>(1</u>         | -2    | 1    | -2                | 11          | ) <del>-</del> 2  | )1       | -2   | )1   | (-2  | )1   | (-2           | 1    | <b>[-2</b> | <u>)</u> 1  | -2 0      |

| 🔶 /top_new/con21     | 0 0                | 1                 | )-2 (1    | -2     | _(1  | )-2              | 1          | )-2         | 1   | (-2             | )1                | 2    | )1               | -2  | )1         | )-2  | 1                 | )-2   | 1    | )-2               | 11          | )-2               | )1       | -2   | )1   | (-2  | )1   | (-2           | 1    | <u>[-2</u> | )1          | -2 0      |

| 🔶 /top_new/con22     | 0                  | )                 | )1 (-2    | 1      | (-2  | )[1              | <u>[-2</u> | <u>(1</u>   | -2  | (1              | )-2               | (1   | ) <del>-</del> 2 | 1   | )-2        | )1   | (-2               | )1    | -2   | <u>)</u> 1        | I-2         | )1                | -2       | 1    | )-2  | (1   | -2   | (1            | -2   | 1          | (-2         | 1 -2      |

| 🔶 /top_new/con3      | 0                  | (15               | )-16 (-15 | 0      |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| 🔶 /top_new/con 13    | 0                  |                   | 2 3       | 4      | (5   | )6               | 17         | 18          | 9   | <u>(10</u>      | )11               | (12  |                  |     |            |      |                   | 13    | 14   | <u>)</u> 15       | I-16        | )-15              | -14      | -13  | -12  | (-11 |      |               |      |            |             |           |

| 🔶 /top_new/con 18    | 0                  |                   | 2         | 3      | (4   | ),5              | 6          | <b>)</b> 7  |     |                 | 8                 | 9    |                  |     | (10        | )11  |                   |       | 12   | 13                | <u>1</u> 14 | 15                | -16      | -15  |      |      | -14  | (-13          |      |            | (-12        | 0         |

| 🔶 /top_new/con8      | 0 2                | 3                 | )4 (5     | 6      |      |                  |            |             |     |                 |                   |      |                  |     |            | 7    | <u>(</u> -8       | )-7   | -6   | 0                 |             |                   |          |      |      |      |      |               |      |            |             |           |

| 🔶 /top_new/data_iin  | 0                  | 1                 |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             |           |

| A Iton newIrom1      | 14 6               |                   |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      | -    |               |      |            |             |           |

| Now                  | 9.9 ns<br>1.506 ns |                   |           | 6.5 ns |      |                  |            |             |     |                 |                   |      |                  | ins |            |      |                   |       |      |                   |             |                   |          | 5 ns |      |      |      |               | 9 ns |            |             |           |

| Cursor 1             |                    | 1                 |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   |             |                   |          |      |      |      |      |               |      |            |             | 1         |

| ·                    | نا کے ا            |                   |           |        |      |                  |            |             |     |                 |                   |      |                  |     |            |      |                   |       |      |                   | _           | _                 | _        | -    | _    | -    | _    | _             | _    | _          | _           |           |

Figure 4. Result based on 32-point split-radix MDC FFT

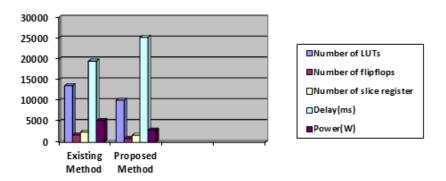

The proposed FFT architectural design offers 17.72% reduction of area and gives the power reduction of 43.63% reduction. The proposed work offers the better performance and utilizes it efficiently compared to the existing 32-point mixed R2, R4, R8 FFT. Performance comparison graph between the existing method and proposed method for different parameters are shown in the Figure 5.

Figure 5. Performance comparison between the existing and proposed method

#### 7. CONCLUSION

The split radix based FFT architecture was designed in VLSI using verilogHDL language. The Multipath delay commutator (MDC) architecture using split radix technique is used for reducing the slices counts occupied by the chip, LUTs counts and higher consumption of power. The proposed structure offers 25.1% reduction in LUTs count, 47.13% reduction in flip-flops usage and 30.89% reduction in slices utilization and 43.63% power reduction. The proposed split radix based MDC structure will be extended to 64-point, 128-point, and 256-point split radix based MDC architecture. For 128-point split radix FFT can be computed by using radix-8 and radix-16 for future development of FFT.

#### REFERENCES

- [1] A R. Mark "On hardware implementation of the split-radix FFT", *IEEE Transactions on Speech and Signal Processing*, vol. 36, no. 10, pp .1575-81, 1998.

- [2] T. Daisuke "An extended split-radix FFT algorithm. Signal processing letters", *IEEE*, vol. 8, no. 5, pp .145-47, 2001.

- [3] L Bu-Ching et al., "Expandable MDC-based FFT architecture and its generator for high-performance applications", SOC Conference (SOCC), 2010 IEEE International. IEEE, Las Vegas, NV, pp.188-92, 2010.

- [4] G Kim et al., "New parallel MDC FFT processor with efficient scheduling scheme", *Circuits and Systems* (APCCAS), IEEE Asia Pacific Conference on. IEEE, Ishigaki, pp. 667-70, 2014.

- [5] Z. Wanget al., "A combined SDC-SDF architecture for normal I/O pipelined radix-2 FFT", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, No. 5, pp.973-977, 2015.

- [6] T. Cho. and H. Lee. "A High-Speed Low-Complexity Modified \${\ rm Radix}-2^{5} \$ FFT Processor for High Rate WPAN Applications", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 21, No. 1, pp.187-191, 2013.

- [7] S. G. Chen Huang et al., "Continuous-flow Parallel Bit-Reversal Circuit for MDF and MDC FFT Architectures", IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 61, No. 10, pp: 2869-2877, 2014.

- [8] B.W. Dickson, and A. Albert, "Parallel Extensions to Single-Path Delay Feedback FFT Architectures", *IEEE conference on 2014.*

- [9] M V K Naik, 'Design of carry select adder for low-power and high speed VLSI applications", *IEEE International Conference on Electrical, Computer and Communication Technologies (ICECCT).* 2015; 1-4.

- [10] G Shilpha, "Low power 128 point split radix fft for lte application", International Journal of MC square Scientific Research (IJMSR).vol. 6, Issue.1, pp: 66-74, 2014.

- [11] A Salh et al. "Maximizing Energy Efficiency for Consumption Circuit Power in Downlink Massive MIMO Wireless Networks", *International Journal of Electrical and Computer Engineering (IJECE)*, vol.7, no. 6, 2017.

- [12] R. Karthik et al., "Distributed Optimal Relay Selection in Wireless Sensor Networks", Indonesian Journal of Electrical Engineering and Computer Science, vol. 7, no. 1, pp.71-74, 2017.

- [13] V. Sharma et al., "Comparative Study of Fuzzy Logic Mobility Based FLM-AODV Routing Protocol and AODV in MANETs", *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 7, no. 1, pp.158-163.